Abstract

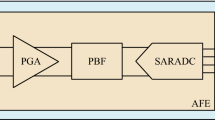

This paper shows an auto adaption unit for reconfigurable ADC that is designed for low power operation with the transistor being operated in weak inversion region. The presented adaptation unit separates high frequency bio-signals from low frequency bio-signals and configures the ADC in the correct mode of operation. The adaptive mechanism provides technological flexibility in order to reconfigure the analog to digital converter (ADC) resolution and sampling rate regardless of the direction of the converter. It produces control bits toconfigure the ADC, based on the frequency and amplitude of the input signal. The reconfigurable ADC along with a auto adaptation circuitis designed for bio-mpedance monitoring systems. The paper consists of pre-amplifier and utilized models of FVC and Schmitt trigger concepts to design auto adaptation unit. The adaption unit consumes 89 \(\upmu\)W with a supply voltage of 0.8 V. Simulation results found the frequency of input signals 1 to 10 MHz for the 10 KHz input signal, the DC voltage produced by the frequency-to-voltage converter is − 691 mV.The entire circuitry is designed, simulated and analyzed by using Cadence EDA tool with 18nm Fin-FET technology.

Similar content being viewed by others

References

Adler, A., & Boyle, A. (2017). Electrical impedance tomography: Tissue properties to image measures. IEEE Transactions on Biomedical Engineering, 64(11), 2494–2504.

Allen, P. E., & Holberg, D. R. (2011). CMOS analog circuit design. Amsterdam: Elsevier.

Anderson, M., Norling, K., Dreyfert, A., & Yuan, J. (2005). A reconfigurable pipelined adc in 0.18/spl mu/m cmos. In: Digest of technical papers, 2005 symposium on VLSI circuits, 2005 (pp. 326–329). IEEE.

Audoglio, W., Zuffetti, E., Cesura, G., & Castello, R. (2006). A 6-10 bits reconfigurable 20 ms/s digitally enhanced pipelined adc for multi-standard wireless terminals. In: 2006 proceedings of the 32nd European solid-state circuits conference (pp. 496–499). IEEE.

Bogónez-Franco, P., Nescolarde, L., Gálvez-Montón, C., Bragós, R., & Rosell-Ferrer, J. (2012). An implantable bioimpedance monitor using 2.45 GHz band for telemetry. Physiological Measurement, 34(1), 1.

Djemouai, A., Sawan, M., & Slamani, M. (1998). High performance integrated cmos frequency-to-voltage converter. In: Proceedings of the tenth international conference on microelectronics (Cat. No. 98EX186) (pp. 63–66). IEEE.

Djemouai, A., Sawan, M. A., & Slamani, M. (2001). New frequency-locked loop based on cmos frequency-to-voltage converter: Design and implementation. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 48(5), 441–449.

Holder, D. (2004). Appendix A. Brief introduction to bioimpedance. Electrical impedance tomography methods, history and applications (pp. 411–422). New York: Taylor & Francis.

Holder, D. S. (2004). Electrical impedance tomography: methods, history and applications. New York: CRC Press.

Iizuka, K., Matsui, H., Ueda, M., & Daito, M. (2006). A 14-bit digitally self-calibrated pipelined adc with adaptive bias optimization for arbitrary speeds up to 40 ms/s. IEEE Journal of Solid-State Circuits, 41(4), 883–890.

Ivorra, A. (2003). Bioimpedance monitoring for physicians: An overview. Centre Nacional de Microelectrònica Biomedical Applications Group, 11, 17.

Jaffrin, M. Y., & Morel, H. (2008). Body fluid volumes measurements by impedance: A review of bioimpedance spectroscopy (bis) and bioimpedance analysis (bia) methods. Medical Engineering & Physics, 30(10), 1257–1269.

Kassanos, P., Constantinou, L., Triantis, I. F., & Demosthenous, A. (2014). An integrated analog readout for multi-frequency bioimpedance measurements. IEEE Sensors Journal, 14(8), 2792–2800.

Luu, D., Kull, L., Toifl, T., Menolfi, C., Brändli, M., Francese, P. A., et al. (2018). A 12-bit 300-ms/s sar adc with inverter-based preamplifier and common-mode-regulation dac in 14-nm cmos finfet. IEEE Journal of Solid-State Circuits, 53(11), 3268–3279.

Martens, E., Hershberg, B., & Craninckx, J. (2018). A 69-db sndr 300-ms/s two-time interleaved pipelined sar adc in 16-nm cmos finfet with capacitive reference stabilization. IEEE Journal of Solid-State Circuits, 53(4), 1161–1171.

Oh, B., Park, K., & Kim, J. J. (2019). A triple-mode performance-optimized reconfigurable incremental adc for smart sensor applications. IEEE Access, 7, 19013–19023.

Qiao, G., Wang, W., Duan, W., Zheng, F., Sinclair, A. J., & Chatwin, C. R. (2012). Bioimpedance analysis for the characterization of breast cancer cells in suspension. IEEE Transactions on Biomedical Engineering, 59(8), 2321–2329.

Razak, Z., Erdogan, A.T., & Arslan, T. (2010). An adaptive algorithm for reconfigurable analog-to-digital converters. In: 2010 NASA/ESA conference on adaptive hardware and systems (pp. 250–257). IEEE

Razavi, B. (1995). Principles of data conversion system design (Vol. 126). New York: IEEE Press.

Razavi, B. (2013). Design considerations for interleaved adcs. IEEE Journal of Solid-State Circuits, 48(8), 1806–1817.

Takhti, M., & Odame, K. (2019). A power adaptive, 1.22-pw/hz, 10-MHz read-out front-end for bio-impedance measurement. IEEE Transactions on Biomedical Circuits and Systems, 13(4), 725–734.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations

Rights and permissions

About this article

Cite this article

Kakarla, H.K., Alagirisamy, M. Design of an auto adaption unit for reconfigurable analog to digital converters. Int J Speech Technol 24, 351–357 (2021). https://doi.org/10.1007/s10772-021-09819-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10772-021-09819-x