Abstract

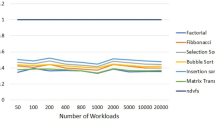

Chip multi-processors are applied in embedded system. An embedded system with multi-cores is considered large and consumes substantial power. Scathed-pad memory (SPM) and non-volatile memory (NVM) are new memory technologies, and an embedded system that uses SPM and NVM can reduce its size and power consumption.This study proposes an optimization of data allocation with data migration algorithm on task-level (TODMA). Data migration and dynamic programming are co-dependent and are combined to allocate task data in TODMA. In the experiments, we evaluated the performance of TODMA algorithm based on DSPstone benchmark and random benchmark. Results of DSPstone show that TODMA reduces the time cost, the number of write activities on NVM, and system energy consumption by 36.25, 24.58, and 34.41 %, respectively, compared with the greedy algorithm. The corresponding reductions are 33.82, 10.00, and 24.27 %, respectively, compared with the iterational optimal data placement algorithm (IODA). For the random benchmark, TODMA can reduce the time cost, the number of write activities on NVM, and system energy consumption by 26.79, 33.32, and 26.88 %, respectively, compared with the greedy algorithm. The advanced percentages are 25.17, 9.87, and 19.54 %, respectively, which are similar to IODA algorithm. Results show that the proposed TODMA algorithm effectively optimizes data allocation problems, improves system performance, reduces the number of write activities on NVM main memory, and lessens system energy consumption.

Similar content being viewed by others

References

Chakraborty, P., Panda, P.R.: Integrating software caches with scratch pad memory. In: Proceedings of the 2012 International Conference on Compilers, Architectures and Synthesis for Embedded Systems, pp. 201–210. ACM (2012)

Chakraborty, P., Panda, P.R.: Spm-sieve: a framework for assisting data partitioning in scratch pad memory based systems. In: Proceedings of the 2013 International Conference on Compilers, Architectures and Synthesis for Embedded Systems, p. 21. IEEE Press (2013)

Dong, X., Wu, X., Sun, G., Xie, Y., Li, H., Chen, Y.: Circuit and microarchitecture evaluation of 3D stacking magnetic ram (MRAM) as a universal memory replacement. In: 45th ACM/IEEE Design Automation Conference, 2008. DAC 2008, pp. 554–559. IEEE (2008)

Dong, X., Xu, C., Xie, Y., Jouppi, N.P.: Nvsim: a circuit-level performance, energy, and area model for emerging nonvolatile memory. Comput.-Aided Des. Integr. Circuits Syst. IEEE Trans. 31(7), 994–1007 (2012)

Hu, J., Xue, C.J., Zhuge, Q., Tseng, W.C., Sha, E.H.M.: Write activity reduction on non-volatile main memories for embedded chip multiprocessors. ACM Trans. Embed. Comput. Syst. (TECS) 12(3), 77 (2013)

Hu, J., Zhuge, X.C.Q., Tseng, W.C., Sha, E.M.: Towards energy efficient hybrid on-chip scratch pad memory with non-volatile memory. In: Design, Automation & Test in Europe Conference & Exhibition, pp. 1–6 (2011)

Joo, Y., Niu, D., Dong, X., Sun, G., Chang, N., Xie, Y.: Energy-and endurance-aware design of phase change memory caches. In: Proceedings of the Conference on Design, Automation and Test in Europe, pp. 136–141. European Design and Automation Association (2010)

Kandemir, M., Irwin, M.J., Chen, G., Kolcu, I.: compiler-guided leakage optimization for banked scratch-pad memories. Very Large Scale Integr. (VLSI) Syst. IEEE Trans. 13(10), 1136–1146 (2005)

Mangalagiri, P., Sarpatwari, K., Yanamandra, A., Narayanan, V., Xie, Y., Irwin, M.J., Karim, O.A.: A low-power phase change memory based hybrid cache architecture. In: Proceedings of the 18th ACM Great Lakes symposium on VLSI, pp. 395–398. ACM (2008)

Qiu, K., Zhao, M., Fu, C., Shi, L., Xue, C.J.: Migration-aware loop retiming for stt-ram based hybrid cache for embedded systems. In: 2013 IEEE 24th International Conference on Application-Specific Systems, Architectures and Processors (ASAP), pp. 83–86. IEEE (2013)

Takase, H., Tomiyama, H., Takada, H.: Partitioning and allocation of scratch-pad memory for energy minimization of priority-based preemptive multi-task systems. IEICE Trans Fundam. Electron. Commun. Comput. Sci. 94(10), 1954–1964 (2011)

Udayakumaran, S., Barua, R.: Compiler-decided dynamic memory allocation for scratch-pad based embedded systems. In: Proceedings of the 2003 International Conference on Compilers, Architecture and Synthesis for Embedded Systems, pp. 276–286. ACM (2003)

Wang, G., Ju, L., Jia, Z., Li, X.: Data allocation for embedded systems with hybrid on-chip scratchpad and caches. In: 2013 IEEE 10th International Conference on Embedded and Ubiquitous Computing (HPCC_EUC), pp. 366–373 (2013)

Wang, J., Dong, X., Xie, Y., Jouppi, N.P.: Endurance-aware cache line management for non-volatile caches. ACM Trans. Archit. Code Optim. (TACO) 11(1), 4 (2014)

Wu, X., Li, J., Zhang, L., Speight, E., Rajamony, R., Xie, Y.: Hybrid cache architecture with disparate memory technologies. In: ACM SIGARCH Computer Architecture News, vol. 37, pp. 34–45. ACM (2009)

Zhang, J., Deng, T., Gao, Q., Zhuge, Q., Sha, E.H.M.: Optimizing data placement of loops for energy minimization with multiple types of memories. J. Signal Process. Syst. 72(3), 151–164 (2013)

Acknowledgments

This work is partially supported by National Natural Science Foundation of China (NSFC) Nos. 61402157, 61502165, and U1405254, and the Science and Technology Research Foundation of Hunan Province No. 2014GK3043, and the Open Foundation of Jiangsu Engineering Center of Network Monitoring No. KJR1541, CICAEET fund and PAPD fund.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Du, J., Li, R., Xiao, Z. et al. Optimization of Data Allocation on CMP Embedded System with Data Migration. Int J Parallel Prog 45, 965–981 (2017). https://doi.org/10.1007/s10766-016-0436-3

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10766-016-0436-3