Abstract

In order to compensate for the non-linearity of an electronic device, an exponentiation conversion circuit that can change the power exponent to any value has been proposed. The exponentiation conversion circuit multiplies the logarithmically converted input signal by a power exponent value to perform exponential conversion. As a result, we can obtain the power function characteristic of a power exponent value. This circuit is a small-scale circuit that utilizes the exponential characteristics of the MOSFET subthreshold region. In a conventional circuit, expansion of the signal dynamic range and reduction of the power supply voltage have been an issue. In this paper, it was confirmed by simulation that the signal dynamic range has expanded by optimizing the current density of MOSFETs. In addition, the linearity of the multiplying circuit was improved by feedback produced by the operational amplifier circuits. We proposed reducing its power supply voltage from 6.0 to 3.3 V by a new multiplying circuit that can eliminate the restriction of maximum voltage gain. Our circuit expands its signal dynamic range from 17.5 to 42.7 dB in condition of the power exponent value from 0.50 to 2.0.

Similar content being viewed by others

Avoid common mistakes on your manuscript.

1 Introduction

Many devices that are used as input/output devices in electronic circuits have non-linear characteristics in wide signal range [1, 2]. In video signal processing field, to compensate these non-linearity, LUT (Look up table) using digital LSI circuit or line approximation using small scale circuit are used in general. However, LUT is not able to be mounted in low cost and line approximation cannot change their compensation characteristics [3,4,5,6]. Therefore, in circuits for nonlinearity compensation, the problems are the large circuit size and the compensation characteristics are not variable. In order to solve these problems, we have proposed a small-scale exponentiation conversion circuit that utilizes the non-linearity of semiconductor devices, and have fabricated a CMOS IC [7,8,9,10]. Figure 1 shows linearization concept of our exponentiation conversion circuit. Non-linear output signals from any sensers are approximately compensated by the exponentiation conversion circuit. Because of the power exponent value γ of the conversion circuit that is able to change to any values, this circuit can compensate wide range non-linearities. In previous research, we carried out confirmation of exponentiation conversion operation [7], electronic control of the compensation characteristics [8, 9] and expansion of signal dynamic range [9, 10]. These circuits are suitable for the interface circuit of AD converters because it can perform arbitrary non-linearity compensation by three-point adjustment [8]. The purpose of this study is to expand the signal dynamic range, and to reduce the supply voltage of this IC from 6.0 to 3.3 V, which allows it to be used in an MPU IC.

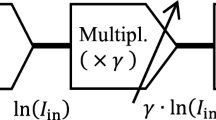

2 Principle of exponentiation conversion

A block diagram of the proposed exponentiation conversion circuit is shown in Fig. 2. In this circuit, a logarithmically transformed input signal ln(Iin) is multiplied by a power exponent value γ and then an exponential conversion is performed. By electronically arbitrarily changing the power exponent to any value used for multiplication, it is possible to compensate nonlinearity in input signals from various electronic devices.

3 Design of circuit

In the exponentiation conversion circuit, it is necessary to logarithmically/exponentially convert the signal, so the exponential transfer characteristic in the subthreshold operation of MOSFET is utilized. The subthreshold operation is obtained in the weak inversion region where the gate-source voltage Vgs is less than the threshold voltage Vt. The drain current Ids can be expressed by the Eq. (1) and shows the exponential characteristic with respect to Vgs [11,12,13,14].

where \(\mu_{{{\text{eff}}}}\) Effective mobility, \({ }C_{{{\text{ox}}}}\) Gate oxide capacitance, \(W\) Channel width, L Channel length, \(C_{{{\text{dm}}}}\) Maximum depletion capacitance, \(V_{{{\text{ds}}}}\) Drain-source voltage, \(m = 1 + \left( {C_{{{\text{dm}}}} /C_{{{\text{ox}}}} } \right)\).

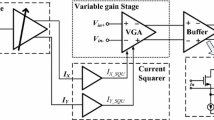

Figure 3 shows the circuit configuration of the exponentiation conversion IC. The omitted back gates of the NMOS are all connected to GND. In Fig. 3, the input signal Iin is converted to the differential signal voltage Vg109 by the logarithmic conversion circuit. In the multiplying circuit, the differential signal voltage Vg109 is multiplied by a constant value, controlled by the multiplication control currents Imni and Imi, and converted to the differential signal voltage Vg2824. The differential signal voltage Vg2824 is converted into the output signal current Iout in the exponential conversion circuit. The operation of each circuit is described below.

3.1 Logarithmic conversion circuit

We designed operational amplifier circuits to convert voltage and current to allow for voltage signal instead of current signal too. The relationship between the input voltage Vin and the input current Iin is expressed by the Eq. (2).

If the voltage to current conversion circuits is directly connected to the sources of M1 and M2 of the logarithmic conversion circuit, the maximum input voltage will be low due to lower the drain-source voltages of M31 and M32. Therefore, we obtained a wide input signal voltage range by flowing the converted signal current through the current mirror circuits CM1 to CM4 with low input voltage drop. CM1 to CM4 used four MOSFETs type current mirror circuits.

A differential voltage obtained by logarithmically converting the input signal current Iin flowing through M1 is input to the multiplying circuit. At that time, because the reference current Irin is flowing through M2, the input signal Vg109 to the multiplying circuit is expressed by the Eq. (3).

Here, S is called the subthreshold swing value, which is equal to the increase amount of the gate-source voltage Vgs when the drain current Id is increased ten times in the subthreshold region range, and is represented by the expression (4) [11], [15,16,17].

Also, subthreshold swing values of Pch and Nch MOSFETs are defined as S(p) and S(n), respectively.

3.2 Multiplying circuit

The multiplying circuit is shown in Fig. 4. Figure 4(a) and (b) show the conventional and the proposed circuit respectively [8]. The differential signal voltage Vg2824 output from the multiplying circuit is expressed by Eq. (5). It can be clarified that the multiplying value becomes larger when Imni is increased and smaller when Imi is increased.

3.3 Exponential conversion circuit

By distributing Vg2824 between the gates and sources of M24 and M25, and M28 and M29, the output signal current Iout of the exponential conversion circuit can be expressed by Eq. (6) using the reference current Irout.

Here, in order to obtain the output signal current Iout proportional to the γ power of the input signal current Iin, it is necessary to satisfy the expression (7), so that the power exponent value γ can be represented by expression (8).

Equation (8) shows that the power exponent value γ can be controlled electronically by varying at least one of Imni and Imi. When Imni = 1 μA and Imi = 0 A, the power exponent value γ is the maximum. Since the ratio of the subthreshold swing values Sn and Sp for Nch and Pch MOSFETs is relatively stable against wide temperature variance, the power exponent value γ is also highly stable [8].

4 Signal dynamic range expansion

We have made three improvements to expand the signal dynamic range. The improvements are described below.

4.1 Optimizing MOSFET current density

We examined the signal dynamic range in the subthreshold region of the MOSFETs. Figure 5 and Fig. 6 shows the transfer characteristic of Nch and Pch MOSFET. In this IC, the signal dynamic range in the subthreshold region is 46.5 dB over the current range from 109 pA to 23.1 nA for the Nch MOSFET, and 41.5 dB over the current range from 147 pA to 17.5 nA for the Pch MOSFET. In order to use the subthreshold region fully, we changed the parallel device number of M1 and M2 from 12 to 360 devices, the parallel device number of M24 and M28 from 30 to 150 devices, and the parallel device number of M25 and M29 from 32 to 160 devices. By increasing the number of parallel devices, the current density was optimized and the signal dynamic range was expanded.

4.2 Introduction of operational amplifier circuits into the multiplying circuit

In order to improve the linearity of the multiplying circuit, operational amplifier circuits OP3 and OP4 were introduced in the proposed circuit shown in Fig. 4(b). The signal dynamic range is expanded by matching the source differential voltage of the input MOSFETs to Vg109 through negative feedback using operational amplifier circuits.

4.3 Improvement of the exponential conversion circuit

The exponential conversion circuit is shown in Fig. 7. Figure 7(a) and (b) show the conventional and the proposed circuit respectively [8]. The signal dynamic range was expanded by adding the following innovations to the conventional circuit shown in Fig. 7(a) to improve the accuracy of the current ratio between Iout and Irout. Specifically, as shown in Fig. 7(b), we configured a circuit so local feedback is applied to the gate of M25 in order to improve the conversion accuracy by adjusting the voltage between the drain and source of M25 and M29 by adding M26 [18]. Although the gate voltage of M24 change according to the input current Iin, the output reference current Irout is kept at constant value by the negative feedback applied by OP5.

The signal dynamic range of the exponential conversion circuit was expanded by 0.8 dB by applying the proposed circuit.

5 Reducing power supply voltage

The conventional multiplying circuit shown in Fig. 4(a) has issue in reducing power supply voltage, because it is composed of M5 to M8, M9 to M10, and M12 to M13 stacked vertically. A folded cascode circuit is a general method for reducing the supply voltage. However, since the same signal current flows through the input and output portions of the circuit, the maximum voltage gain, which is determined by the ratio of the input voltage range to the output voltage range, cannot be increased by lowering the supply voltage. As a result, the maximum voltage gain of the multiplying circuit becomes small. The maximum exponent value γ decreases to 1.4 in a conventional folded cascode circuit. The proposed multiplying circuit shown in Fig. 4(b) achieves low supply voltage by parallelizing the input and output signal voltages with a current mirror circuit, and eliminates the restriction of the maximum voltage gain by setting the signal currents independently. In the proposed circuit, input bias current Ibi that decides input voltage range is obtained from each of M16 and M17. Also, output bias currents Ibo that decides output voltage range is obtained from each of M14 and M15. Differential signal current Vg109/Rs1 is added to input bias current Ibi, therefore drain current of M9 and M18 becomes (Ibi + Vg109/Rs1)/2 and drain current of M10 and M19 becomes (Ibi–Vg109/Rs1)/2. Because of synthesizing these currents by current mirror circuit consisting of M20 to M23, both of the differential signal current Vg109/Rs1 and output bias currents Ibo flows into the source terminals of the differential pairs M5 to M8 with input bias current Ibi eliminated. By applying the proposed circuit, even when the supply voltage is reduced to 3.3 V, the maximum exponent value γ can be obtained to 2.9.

In this circuit, the maximum input signal voltage Ibi × Rs1 can be freely expanded by increasing the input bias current Ibi, which does not appear in the differential signal current, so that the maximum voltage gain can be increased as much as necessary with a low Rs1. Negative feedback circuits are generally used to increase the voltage gain while keeping the DC operating point, but the higher cut-off frequency decreases as the voltage gain increases. In the case of this circuit, the higher cut-off frequency is determined by the circuit time constant, so its reduction can be suppressed.

6 Simulation results

We designed exponentiation conversion circuit as an integrated circuit in 0.6 μm CMOS process by using the SPICE circuit simulator “C3 (Circuit-Cube)” of JEDAT Inc. In this simulation, we used bsim3v3n model as N channel MOSFET and bsim3v3p model as P channel MOSFET. The characteristics obtained from the simulation are described below.

6.1 Logarithmic conversion circuit

The conversion characteristics of the logarithmic conversion circuit are shown in Fig. 8, where the signal dynamic range of the logarithmic conversion circuit has been expanded from 32.9 to 72.8 dB by optimizing the current density of MOSFETs M1 and M2.

6.2 Multiplying circuit

The input/output characteristics of the multiplying circuit are shown in Fig. 9. By using operational amplifier circuits with negative feedback, the ratio of signal dynamic range expanded from 34.3 to 91.6% when the voltage range that multiplying circuit is able to output is defined as 100%. The signal dynamic range is defined as the input voltage range in which the change in the slope of the characteristics shown in Fig. 9 is within ± 5%.

6.3 Exponential conversion circuit

The conversion characteristics of the exponential conversion circuit are shown in Fig. 10, where the signal dynamic range of the exponential conversion circuit is expanded from 61.4 to 69.7 dB by optimizing the current densities of MOSFETs M24 to M25 and M28 to M29 and the circuit shown in Fig. 7(b).

6.4 Signal dynamic range of the IC

Figure 11 shows the input/output characteristics when the power exponent value γ is set to 0.50, 1.0, and 2.0. In Fig. 11, the three characteristic lines pass through a single operating point determined by the reference current Irin.

The signal dynamic range is the input current range within which the change in the slope of both logarithmic graphs of the input–output characteristics of the exponentiation conversion circuit shown in Fig. 12 is within ± 5%. The signal dynamic range of the input signal at each power exponent value γ is shown in Table 1, where the signal dynamic range expands from 17.5 to 42.7 dB when the power exponent value γ is set from 0.50 to 2.0 by optimizing the current density of the MOSFETs and negative feedback by operational amplifier circuits.

6.5 Frequency characteristics of the IC

Table 2 shows higher cut-off frequency of each circuit block and whole exponentiation conversion circuit. In this simulation, the power exponent value γ is set to 1.0 and the input signal bias current Iin equals to the reference current Irin in order to fix the output signal bias current Iout to the operating point. Table 2 shows slowing down in operating of these circuits due to reducing current density in MOSFETs to utilize weak inversion operation.

7 Layout design of the IC

A layout diagram designed using a 0.6 μm CMOS process is shown in Fig. 13. Since the current density of the MOSFETs was optimized, a parallel configuration of 360 devices, which is the maximum, was used for M1 and M2 in the logarithmic conversion circuit.

8 Measured results

The measurement results of the prototype IC are described below. The measurement conditions were as follows. We used digital multimeter DT-4282 made by HIOKI Inc. for measurement.

Figures 14 and 15 show the measured results of the input/output characteristics when the power exponent value γ is set to 0.50, 1.0 and 2.0. In Fig. 14, the three characteristic lines pass through a single operating point determined by the reference current Irin. The signal dynamic range of the conventional circuit was 6.90 dB. However by optimizing the current density of the MOSFET and applying an operational amplifier to the circuit, the signal dynamic range was increased to 30.0 dB. These results are summarized in Table 3. The measured higher cut-off frequency was 3.40 kHz that is one-tenth of simulation result because of signal line parasitic capacitance increase in the measurement circuit board.

9 Conclusions

We expanded the signal dynamic range and reduced the power supply voltage of the exponentiation conversion IC. By optimizing the current density of MOSFETs in the IC and applying operational amplifier circuits, the signal dynamic range has expanded from 17.5 to 42.7 dB in the range of the power exponent value γ from 0.50 to 2.0. Furthermore, a ew multiplying circuit was proposed, in which the maximum voltage gain can be set to a large value independent of the supply voltage. By applying the proposed circuit, even when the supply voltage was reduced to 3.3 V, the maximum exponent value γ can be obtained at 2.9. The signal dynamic range of prototype IC expanded to 30.0 dB when the power exponent value γ is set from 0.50 to 2.0 as measured result.

In the future, we will evaluate the characteristics of the prototype IC of the proposed circuit to confirm issues in actual operation and further improve performance.

References

Omori T. (1998) Sensor technology popular ed,” Fuji Techno System Co. Ltd., (1998) (in Japanese)

Tiek, T., & Gennissen, P. T. J. (2009). Arrangement for linearizing a non-linear sensor. EP, 2, 128–579.

The Institute of Image Information and Television Engineers “Information display handbook,” Baifukan Co. Ltd., (2001) (in Japanese)

Motamed, A., Hwang, C., & Ismail, M. (1997). CMOS exponential current-to-voltage converter. Electronics Letters, 33(12), 998–1000.

Popa, C. (2005) Improved accuracy pseudo-exponential function generator with applications in analog signal processing. in EUROCON 2005 - The International Conference on “Computer as a Tool, Belgrade, Serbia, pp. 1594–1597.

Brannen, R. A., Elwan, H., & Ismail, M. (1999) A simple low-voltage all MOS linear-dB AGC/multiplier circuit. in Proceedings 1999 IEEE International Symposium on Circuits and Systems, 2, pp. 318–321.

Arai, M., & Sano, Y. (2018) Development of universal gamma collection IC composed of MOSFET operating in subthreshold region. IEEJ Electronics, Information and Systems, PS1–5 (2018) (in Japanese)

Arai, M., & Sano, Y. (2020). Exponentiation conversion circuit capable of changing the power exponent to any value. IEEJ Transactions on Electronics, Information and Systems, 140(1), 24–31.

Arai, M., & Sano, Y. (2021). Exponentiation conversion circuit capable of changing the power exponent to any value. Journal of Analog Integrated Circuits and Signal Processing, 19(7), 471–479.

Arai, M., Nishiyama, N., & Sano, Y. (2022). Signal dynamic range expansion for exponentiation conversion circuit capable of changing the power exponent to any value. IEEJ Transactions on Electronics, Information and Systems, 142(1), 15–24.

Taur, Y., & Ning, T. H. (1998). Fundamentals of Modern VLSI Devices (2nd ed., pp. 128–129). Springer.

Enz, C., Krummenacher, F., & Vittoz, E. (1995). An analytical MOS transistor model valid in all regions of operation and dedicated to low-voltage and low-current applications. Specail Issue of the Analog Integrated Circuits and Signal Processing Journal on Low-Voltage and Low-Power Design, 8, 83–114.

V. De, Y. Ye, A. Keshavarzi, S. Narenda, J. Kao, D. Somasekhar, R. Nair, and S. Borkar Techniques for leakage for power reduction. in Design of High-Performance Microprocessor Circuits, In: Ed. A. Chandrakasan, W. Bowhill, and F. Fox, ch.3, pp. 46–62, IEEE Press (2001)

Roy, K., Mukhopadhyay, S., & Mahmoodi-Meimand, H. (2003). Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proceeding of the IEEE, 91(2), 305–327.

Wang, A., Calhoun, B. H., & Chandrakasan, A. P. (2006). Sub-threshold design for ultra low-power systems (p. 31). Springer.

Weste, N. H., & Harris, D. (2013) CMOS VLSI design a circuits and systems perspective 4th ed. Japanese language edition. Mruzen Publishing Co. Ltd. (2013)

Wang et al. G. (2006) A 0.127μm2 high performance 65nm SOI based embedded DRAM for on-processor applications. In Proc. Intl. Electron Devices meeting, pp. 1–4.

Nishiyama, N., Arai, M., & Sano, Y. (2021) Reducing power supply voltage for CMOS exponentiation conversion IC that utilizes weak inversion operation. IEEJ Electronics, Information and Systems, GS9–5 pp. (2021) (in Japanese)

Author information

Authors and Affiliations

Contributions

Author Nishiyama carried out the experiments and analysis of the study and wrote the paper. Author Matsui performed only the experiments, and Sano provided research guidance. All authors reviewed the manuscript.

Corresponding author

Ethics declarations

Competing interests

The authors declare no competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Nishiyama, N., Matsui, F. & Sano, Y. Signal dynamic range expansion and power supply voltage reduction for an exponentiation conversion IC. Analog Integr Circ Sig Process 119, 185–194 (2024). https://doi.org/10.1007/s10470-023-02247-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-023-02247-8