Abstract

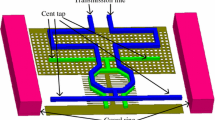

In this paper a four mode 130 nm RF CMOS power amplifier (PA) in a single propagation path topology is presented and evaluated with IEEE 802.11ax signals. Specifically, this configuration is supported by three main concepts: scaling of the supply voltage, consecutive voltage amplifications and selection of the operation modes of transistors (saturation or triode). The concept is tested at 2.4 GHz and the obtained post-layout simulation results are reported. The four efficiency profiles of the proof-of-concept are: N4S3A1 (common-source), low-power (N4S2A2), medium-power (N4S1A3), and high-power (N4S0A4). For each of those modes the 1 dB output compression point (OCP\(_\text {1dB}\)) and the power added efficiency (PAE) at OCP\(_\text {1dB}\) are evaluated with the following results, respectively: 17.5 dBm and 23 % (N4S3A1); 16.8 dBm and 28.1 % (N4S2A2), 18.1 dBm and 28.9 % (N4S1A3), and 19.9 dBm and 25.7 % (N4S0A4). In terms of process–voltage–temperature analysis, the worst and best performances obtained for OCP\(_\text {1dB}\) and PAE at OCP\(_\text {1dB}\) are: 13.9 dBm and 16.8 dBm, 13.6 % and 29.3 % (N4S3A1); 15.4 dBm and 19.3 dBm, 20.3 dBm and 40.7 % (N4S2A2); 16.7 dBm and 19.3 dBm, 21.7 % and 36.6 % (N4S1A3); 19.2 and 21.2, 18.9 % and 36 % (N4S0A4). As for IEEE 802.11ax signals under 16 QAM operation (MCS4), the PA performs an output power at limit EVM (-19 dB) for modes N4S3A1, N4S2A2, N4S1A3, and N4S0A4 of: 14.7 dBm, 15.3 dBm, 16.7 dBm, and 17.8 dBm.

Similar content being viewed by others

Notes

Graphically determined.

Analysis based on the low frequency, four terminal, simplified small-signal model for MOST [13] with \(C_{gd}\), \(C_{gb}\), \(C_{bd}\), \(C_{bs}\), and drain to source and body to source currents all equal to zero. Source and body terminals are shorted.

A cascode with stack height equals two

References

Bellalta, B. (2016). IEEE 802.11ax: High-efficiency WLANS. IEEE Wireless Communications, 23, 38–46.

Santos, F. G., de Almeida Leite, B. R. B., & Mariano, A. A. (2020). A novel single propagation path multimode PA. In 2020 33rd Symposium on Integrated Circuits and Systems Design (SBCCI), IEEE.

McCune, E. (2015). A technical foundation for RF CMOS power amplifiers: Part 2: Power amplifier architectures. IEEE Solid-State Circuits Magazine, 7(4), 75–82.

Modesto, A., Santos, F., Pereira, J., Leite, B., & Mariano, A. (2019). A CMOS power amplifier with reconfigurable power cells and matching network for 2.4 ghz wireless communications. AEU - International Journal of Electronics and Communications, 111, 152919.

Luong, G., Kerherve, E., Pham, J.-M., & Medrel, P. (2018). A 2.5-ghz multimode broadband bias-segmented power amplifier with linearity-efficiency tradeoff. IEEE Microwave and Wireless Components Letters, 28, 1038–1040.

Ou, W.-L., Tsai, Y.-K., Tseng, P.-Y., Lu, & L.-H. (2017) A 2.4-ghz dual-mode resizing power amplifier with a constant conductance output matching. In 2017 30th IEEE International System-on-Chip Conference (SOCC), IEEE.

Santos, F., Mariano, A., & Leite, B. (2016). 2.4 GHz CMOS digitally programmable power amplifier for power back-off operation. In 2016 IEEE 7th Latin American Symposium on Circuits & Systems (LASCAS), Institute of Electrical & Electronics Engineers (IEEE) .

Hsieh, C.-H., & Tsai, Z.-M. (2017). A k-band linear/normal/efficient tri-mode power amplifier in 0.18-um CMOS with body bias adoption. In 2017 IEEE Asia Pacific Microwave Conference (APMC), IEEE.

Kuang, L., Chi, B., Jia, H., Jia, W., & Wang, Z. (2015). A 60-GHz CMOS dual-mode power amplifier with efficiency enhancement at low output power. IEEE Transactions on Circuits and Systems II: Express Briefs, 62, 352–356.

Pornpromlikit, S., Jeong, J., Presti, C., Scuderi, A., & Asbeck, P. (2010). A watt-level stacked-FET linear power amplifier in silicon-on-insulator CMOS. IEEE Transactions on Microwave Theory and Techniques, 58, 57–64.

Dabag, H.-T., Hanafi, B., Golcuk, F., Agah, A., Buckwalter, J. F., & Asbeck, P. M. (2013). Analysis and design of stacked-FET millimeter-wave power amplifiers. IEEE Transactions on Microwave Theory and Techniques, 61, 1543–1556.

Tarar, M. M., Wei, M.-D., Khan, M. A., & Negra, R. (2016). A compact broadband stacked medium power amplifier in standard 65 nm CMOS technology. Analog Integrated Circuits and Signal Processing, 89, 327–335.

Tsividis, Y. (2013). The MOS transistor. New York Oxford: Oxford University Press.

Haghighat, M., & Nabavi, A. (2016). Fully integrated CMOS power amplifier with linearity and efficiency enhancement using 2nd harmonic injection technique. Analog Integrated Circuits and Signal Processing, 90, 81–91.

Acknowledgements

This work has been partially supported by CNPq and CAPES, Finance Code 001.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Santos, F.G., Leite, B.R.B.d.A. & Mariano, A.A. A multimode CMOS PA with a single propagation path. Analog Integr Circ Sig Process 108, 421–435 (2021). https://doi.org/10.1007/s10470-021-01886-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01886-z