Abstract

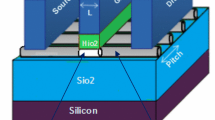

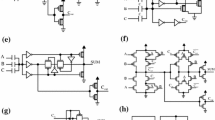

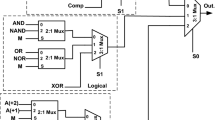

In recent years, there has been a growing interest in energy efficient VLSI designs for portable devices. Full adder cell is one of the most widely used and important blocks of arithmetic units that are in many digital signal processors. The quest to reach low energy consumption, and high noise immunity in the nanoscale regime, directed this work for discovering a new low-power and noise immune full adder cell. In this paper, a full adder with an innovative hybrid structure of pass-transistor and complementary styles is proposed based on carbon nanotube field effect transistor (CNFET). CNFET as one of the alternative nanodevices is the most feasible option to replace MOSFET technology for production by the early 2020, from industry perspective. The proposed full adder as well as the most relevant state-of-the-art designs are evaluated for different parameters, such as delay, power dissipation, and energy consumption over two different test-bed scenarios. In the first scenario, full adder cells are compared for different operating conditions such as different operating frequency, load capacitors, and supply voltages. In the second scenario, full adder cells are embedded and evaluated in 4-operands carry save adder with the final ripple carry adder in 4 and 8 bit lengths. These evaluations have been carried out using Synopsis HSPICE and the Stanford CNFET model for the 16 nm technology node. The proposed full adder leads to the average energy consumption improvements of 37% and 43% in 4-bit and 8-bit structures, respectively, as compared to the other existing designs. Also simulation results indicated that the proposed design is more immune against noises compared to the other designs.

Similar content being viewed by others

References

Johnson, L., Levine, A., Smith, R., & Stone, S. (2010). The 2010 Horizon report. ERIC.

Sarwar, M., & Soomro, T. R. (2013). Impact of Smartphone’s on society. European Journal of Scientific Research, 98, 216.

Chandrakasan, A. P., Sheng, S., & Brodersen, R. W. (1992). Low-power CMOS digital design. IEICE Transactions on Electronics, 75, 371–382.

Oklobdzija, V. G., & Krishnamurthy, R. K. (2007). High performance energy efficient microprocessor design. Berlin: Springer.

Rabaey, J. M., & Pedram, M. (2012). Low power design methodologies. Berlin: Springer.

Alioto, M., & Palumbo, G. (2002). Analysis and comparison on full adder block in submicron technology. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 10, 806–823.

Weste, N., Harris, D., & Banerjee, A. (2005). Cmos VLSI design: A circuits and systems perspective. Delhi: Pearson Education.

Chang, C. H., Gu, J., & Zhang, M. (2005). A review of 0.18 \(\mu\)m full adder performances for tree structured arithmetic circuits. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 13, 686–695.

Goel, S., Kumar, A., & Bayoumi, M. A. (2006). Design of robust, energy-efficient full adders for deep-submicrometer design using hybrid-CMOS logic style. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 14, 1309–1321.

Navi, K., Kavehei, O., Rouholamini, M., Sahafi, A., Mehrabi, S., & Dadkhahi, N. (2008). Low-power and high-performance 1-bit CMOS full adder cell. Journal of Computational Physics, 3, 48–54.

Aguirre-Hernandez, M., & Linares-Aranda, M. (2011). CMOS full adders for energy-efficient arithmetic applications. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 19, 718–721.

Bhattacharyya, P., Kundu, B., Ghosh, S., Kumar, V., & Dandapat, A. (2015). Performance analysis of a low-power high-speed hybrid 1-bit full adder circuit. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23, 2001–2008.

Kuhn, K. J. (2012). Considerations for ultimate CMOS scaling. IEEE Transactions on Electron Devices, 59, 1813–1828.

Marsh, G. (2003). Moore’s law at the extremes. Materials Today, 6, 28–30.

Thompson, S. E., & Parthasarathy, S. (2006). Moore’s law: The future of Si microelectronics. Materials Today, 9, 20–25.

Chau, R., Doyle, B., Datta, S., Kavalieros, J., & Zhang, K. (2007). Itegrated nanoelectronics for the future. Nature Materials, 6, 810–812.

Markov, I. L. (2014). Limits on fundamental limits to computation. Nature, 512, 147–154.

Cavin, R. K., Lugli, P., & Zhirnov, V. V. (2012). Science and engineering beyond Moore’s law. Proceedings IEEE, 100, 1720–1749 (Special Centennial Issue).

Franklin, A. D. (2013). Electronics: The road to carbon nanotube transistors. Nature, 498, 443–444.

Robertson, J. (2007). Growth of nanotubes for electronics. Materials Today, 10, 36–43.

Peng, L. M., Zhang, Z., & Wang, S. (2014). Carbon nanotube electronics: Recent advances. Materials Today, 17, 433–442.

Appenzeller, J. (2008). Carbon nanotubes for high-performance electronics—Progress and prospect. Proceedings IEEE, 96, 201–211.

Raychowdhury, A., Keshavarzi, A., Kurtin, J., De, V., & Roy, K. (2006). Carbon nanotube field-effect transistors for high-performance digital circuits. IEEE Transactions on Electron Devices, 53, 2718–2726.

Avouris, P., Chen, Z., & Perebeinos, V. (2007). Carbon-based electronics. Nature Nanotechnology, 2, 605–615.

Appenzeller, J., Knoch, J., Martel, R., Derycke, V., Wind, S. J., & Avouris, P. (2002). Carbon nanotube electronics. IEEE Transactions on Nanotechnology, 1, 184–189.

Bachtold, A., Hadley, P., Nakanishi, T., & Dekker, C. (2001). Logic circuits with carbon nanotube transistors. Science, 294, 1317–1320.

Chen, Z., Wong, H. S. P., Mitra, S., Bol, A., Peng, L., Hills, G., & Thissen, N. (2014). Carbon nanotubes for high-performance logic. MRS Bulletin, 39, 719–726.

Shulaker, M. M., Hills, G., Patil, N., Wei, H., Chen, H. Y., Wong, H. S. P., & Mitra, S. (2013). Carbon nanotube computer. Nature, 501, 526–530.

Kreupl, F. (2013). Electronics: The carbon-nanotube computer has arrived. Nature, 7468, 495–496.

Sharifi, F., Moaiyeri, M. H., Navi, K., & Bagherzadeh, N. (2015). Robust and energy-efficient carbon nanotube FET-based MVL gates; A novel design approach. Microelectronics Journal, 46, 1333–1342.

Moaiyeri, M. H., Khastoo, N., Nasiri, M., Navi, K., & Bagherzadeh, N. (2016). An efficient analog-to-digital converter based on carbon nanotube FETs. Journal of Low Power Electronics, 12, 150–157.

Sheng, L., Kim, Y., & Lombardi, F. (2012). Design of a ternary memory cell using CNTFETs. IEEE Transactions on Nanotechnology, 11, 1019–1025.

Bozorgmehr, A., Moaiyeri, M. H., Navi, K., & Bagherzadeh, N. (2017). Ultra-efficient fuzzy min/max circuits based on carbon nanotube FETs. IEEE Transactions on Fuzzy Systems, PP, 1–1.

Sharifi, F., Panahi, A., Sharifi, H., Navi, K., Bagherzadeh, N., & Thapliyal, H. (2016). Design of quaternary 4–2 and 5–2 compressors for nanotechnology. Computers & Electrical Engineering, 56, 64–74.

Moghaddam, M., Moaiyeri, M. H., & Eshghi, M. (2016). Design and evaluation of an efficient Schmitt trigger-based hardened latch in CNTFET technology. IEEE Transactions on Device and Materials Reliability, 17, 267–277.

Deng, J., & Philip Wong, H. S. (2007). A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—Part I: Model of the intrinsic channel region. IEEE Transactions on Electron Devices, 54, 3186–3194.

Deng, J., & Philip Wong, H. S. (2007). A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application—Part I: Model of the intrinsic channel region. IEEE Transactions on Electron Devices, 54, 3195–3205.

Frustaci, F., Pasquale, C., Stefania, P., & Giuseppe, C. (2008). High-performance noise-tolerant circuit techniques for CMOS dynamic logic. IET Circuits, Devices & Systems, 6, 537–548.

Katopis, G. A. (1985). Delta-I noise specification for a high-performance computing machine. Proceedings of IEEE, 73, 1405–1415.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Taheri, M., Shafiee, N., Sharifi, F. et al. Energy efficient hybrid full adder design for digital signal processing in nanoelectronics. Analog Integr Circ Sig Process 109, 135–151 (2021). https://doi.org/10.1007/s10470-021-01831-0

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-021-01831-0