Abstract

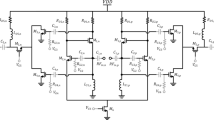

A bias stabilization scheme for inverter is introduced. The conventional inverter structure has lent itself as a power-efficient amplifier block for low-power, low-voltage applications. However, its application is restricted due to the limits in its biasing method. This letter introduces an efficient biasing scheme based on forward body bias technique. The proposed biasing scheme relaxes most of the problems associated with the unreliable conventional biasing method. Spectre simulation utilizing TSMC 180 nm technology are utilized to compare the performance of the proposed circuit with that’s of conventional inverter and also with well-known common-source amplifier. All three versions are biased with 0.4 V power supply and 3 µA bias current. In addition to the performance examination, full process, voltage, and temperature analysis is also conducted through Monte Carlo and corner simulations. The results validate the well-performance of the proposed structure under various operating conditions.

Similar content being viewed by others

References

Fahim, A. (2014). Challenges in low-power analog circuit design for sub-28 nm CMOS technologies. In 2014 IEEE/ACM international symposium on low power electronics and design (ISLPED), 11–13 August 2014 (pp. 123–126). https://doi.org/10.1145/2627369.2631639.

Sansen, W. (2007). Analog design challenges in nanometer CMOS technologies. In 2007 IEEE Asian solid-state circuits conference, 12–14 November 2007 (pp. 5–9). https://doi.org/10.1109/asscc.2007.4425792.

López-Martin, A., Carvajal, R. G., López-Morillo, E., Acosta, L., Sánchez-Rodriguez, T., Rubia-Marcos, C., et al. (2009). Low-voltage power-efficient amplifiers for emerging applications. In M. Steyaert, A. H. M. van Roermund, & H. Casier (Eds.), Analog circuit design: High-speed clock and data recovery, high-performance amplifiers, power management (pp. 147–165). Dordrecht: Springer.

Yuan, F. E., & Iniewski, K. (2019). Low power circuits for emerging applications in communications, computing, and sensing. Boca Raton: CRC Press.

Wilson, W., Chen, T., & Selby, R. (2013). A current-starved inverter-based differential amplifier design for ultra-low power applications. In 2013 IEEE 4th Latin American symposium on circuits and systems (LASCAS), 27 February–1 March 2013 (pp. 1–4). https://doi.org/10.1109/lascas.2013.6519040.

Jagadish, D. N., & Bhat, M. S. (2014). A low voltage inverter based differential amplifier for low power switched capacitor applications. In 2014 Fifth international symposium on electronic system design, 15–17 December 2014 (pp. 58–62). https://doi.org/10.1109/ised.2014.20.

Ng, K. A., & Xu, Y. P. (2016). A low-power, high CMRR neural amplifier system employing CMOS inverter-based OTAs with CMFB through supply rails. IEEE Journal of Solid-State Circuits, 51(3), 724–737.

Omran, H., Alhoshany, A., Alahmadi, H., Salama, K. N., & Papers, S. I. R. (2017). A 33fJ/Step SAR capacitance-to-digital converter using a chain of inverter-based amplifiers. IEEE Transactions on Circuits and Systems I: Regular Papers, 64(2), 310–321.

Chae, M., Kim, J., & Liu, W. (2008). Fully-differential self-biased bio-potential amplifier. Electronics Letters, 44(24), 1390–1391. https://doi.org/10.1049/el:20089097.

Baltolu, A., Albinet, X., Chalet, F., Dallet, D., & Begueret, J.-B. (2018). A robust inverter-based amplifier versus PVT for discrete-time integrators. International Journal of Circuit Theory and Applications, 46, 2160–2169. https://doi.org/10.1002/cta.2517.

Yeo, J., Choi, Y., Roh, J., Han, G., Chae, Y., & Ham, S. (2014). A current regulator for inverter-based massively column-parallel ΔΣ ADCs. IEEE Transactions on Circuits and Systems II: Express Briefs, 61(4), 224–228.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Faraji Baghtash, H. Bias-stabilized inverter-amplifier: an inspiring solution for low-voltage and low-power applications. Analog Integr Circ Sig Process 105, 243–248 (2020). https://doi.org/10.1007/s10470-020-01705-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01705-x