Abstract

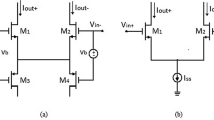

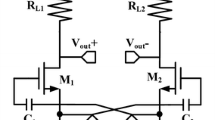

A tail-less, fully differential trans-conductance amplifier is presented in this paper. The proposed structure arranges the inverters as a core amplifier blocks in an elaborate manner to achieve fully differential function with tail-less power optimized elements. As the inverters are current push–pull structures, they reuse the bias current effectively to maximize the trans-conductance of block. The proposed amplifier structure exploits this to reduce the power consumption of proposed structure to 2.6 µW. Post-layout simulations with a load capacitance of 5 pF and power supply of 0.4 V have been performed to validate the performance of the proposed amplifier. The proposed amplifier exhibits a DC gain of 72.6 dB and a phase margin of 56° at unity-gain frequency of 327 kHz for a load of 5 pF. The proposed structure also delivers high common mode rejection ratio and power supply rejection ration values of 111 dB and 103 dB, respectively. To investigate the performance of the design over process and temperature variations, the Monte Carlo and corner simulations are performed, as well. The simulations are conducted with TSMC 180 nm CMOS technology file with Spectre simulation engine.

Similar content being viewed by others

References

Fahim, A. (2014). Challenges in low-power analog circuit design for sub-28nm CMOS technologies. In 2014 IEEE/ACM international symposium on low power electronics and design (ISLPED), 11–13 Aug. 2014 (pp. 123–126).

Sansen, W. (2007). Analog design challenges in nanometer CMOS technologies. In 2007 IEEE Asian solid-state circuits conference, 12–14 Nov. 2007 (pp. 5–9).

Veldandi, H., & Shaik, R. A. (2018). A 0.3-V Pseudo-differential bulk-input OTA for low-frequency applications. Circuits, Systems, Signal Processing,37(12), 5199–5221.

Lu, Y., & Yao, R. H. (2008). Low-voltage constant-gm rail-to-rail CMOS operational amplifier input stage. Solid-State Electronics,52(6), 957–961.

Zhao, X., Fang, H., Ling, T., & Xu, J. J. I. (2015). Transconductance improvement method for low-voltage bulk-driven input stage. Integration the VLSI Journal,49, 98–103.

Abdelfattah, O., Roberts, G. W., Shih, I., & Shih, Y. (2015). An ultra-low-voltage CMOS process-insensitive self-biased ota with rail-to-rail input range. IEEE Transactions on Circuits and Systems I: Regular Papers,62(10), 2380–2390. https://doi.org/10.1109/TCSI.2015.2469011.

Khateb, F. (2015). The experimental results of the bulk-driven quasi-floating-gate MOS transistor. AEU-International Journal of Electronics Communications,69(1), 462–466.

Khateb, F., Kulej, T., Veldandi, H., & Jaikla, W. (2019). Multiple-input bulk-driven quasi-floating-gate MOS transistor for low-voltage low-power integrated circuits. AEU-International Journal of Electronics Communications,100, 32–38.

Zuccarotto, C., Richelli, A., Kennedy, S., Rcdoute, & J.-M. (2018). Design of a self-cascoded miller amplifier with superior EMI immunity in UMC 180NM CMOS. In 2018 international symposium on electromagnetic compatibility (EMC EUROPE), (pp 425–428). IEEE.

Ansari, M.S., Sinha, R., & Khot, S. (2017) Ultra-low power 50/60Hz notch filter for biomedical signal acquisition using 32nm±0.15 V Bulk-Driven subthreshold CMOS OTAs. In 2017 4th international conference on electrical and electronic engineering (ICEEE) 2017 (pp 309–313). IEEE.

Grasso, A. D., Marano, D., Palumbo, G., & Pennisi, S. (2015). Design methodology of subthreshold three-stage CMOS OTAs suitable for ultra-low-power low-area and high driving capability. IEEE Transactions on Circuits and Systems I: Regular Papers,62(6), 1453–1462.

Webster, J. G. (2009). Medical instrumentation: Application and design. Hoboken: Wiley.

Lee, S.-Y., Wang, C.-P., & Chu, Y.-S. (2018). Low-voltage OTA–C filter with an area-and power-efficient OTA for biosignal sensor applications. IEEE Transactions on Biomedical Circuits and Systems,13(1), 56–67.

Akbari, M., Hashemipour, O., Moaiyeri, M. H., & Aghajani, A. (2017). An efficient approach to enhance bulk-driven amplifiers. Analog Integrated Circuits Signal Processing,92(3), 489–499.

Khateb, F., Kulej, T., & Vlassis, S. (2017). Extremely low-voltage bulk-driven tunable transconductor. Circuits, Systems, Signal Processing,36(2), 511–524.

Kulej, T., & Khateb, F. (2017). Sub 0.5-V bulk-driven LTA in 0.18μm CMOS. AEU - International Journal of Electronics and Communications,77, 67–75. https://doi.org/10.1016/j.aeue.2017.04.032.

Raikos, G., & Vlassis, S. (2011). Low-voltage bulk-driven input stage with improved transconductance. International Journal of Circuit Theory and Applications,39(3), 327–339. https://doi.org/10.1002/cta.637.

Kulej, T. (2015). 0.4-V bulk-driven operational amplifier with improved input stage. Circuits, Systems, Signal Processing,34(4), 1167–1185.

Wilson, W., Chen, T., & Selby, R. (2013). A current-starved inverter-based differential amplifier design for ultra-low power applications. In 2013 IEEE 4th latin American symposium on circuits and systems (LASCAS), 27 Feb.-1 March 2013 2013 (pp 1–4)

Jagadish, D.N., & Bhat, M.S. (2014) A low voltage inverter based differential amplifier for low power switched capacitor applications. In 2014 Fifth international symposium on electronic system design, 15–17 Dec. 2014, (pp 58–62)

Ng, K. A., & Xu, Y. P. (2016). A low-power, high CMRR neural amplifier system employing CMOS inverter-based OTAs with CMFB through supply rails. IEEE Journal of Solid-State Circuits,51(3), 724–737.

Kinget, P. R. (2005). Device mismatch and tradeoffs in the design of analog circuits. IEEE Journal of Solid-State Circuits,40(6), 1212–1224. https://doi.org/10.1109/JSSC.2005.848021.

Assaad, R. S., & Silva-Martinez, J. (2009). The recycling folded cascode: A general enhancement of the folded cascode amplifier. IEEE Journal of Solid-State Circuits,44(9), 2535–2542.

Akbari, M., Nazari, M., Sharifi, L., & Hashemipour, O. (2015). Improving power efficiency of a two-stage operational amplifier for biomedical applications. Analog Integrated Circuits and Signal Processing,84(2), 173–183.

Chen, Y.-P., Jeon, D., Lee, Y., Kim, Y., Foo, Z., Lee, I., et al. (2014). An injectable 64 nW ECG mixed-signal SoC in 65 nm for arrhythmia monitoring. IEEE Journal of Solid-State Circuits,50(1), 375–390.

Kulej, T., & Khateb, F. (2018). Design and implementation of sub 0.5-V OTAs in 0.18-μm CMOS. International Journal of Circuit Theory and Applications,46(6), 1129–1143. https://doi.org/10.1002/cta.2465.

Ferreira, L. H. C., & Sonkusale, S. R. (2014). A 60-dB Gain OTA Operating at 0.25-V Power Supply in 130-nm Digital CMOS Process. IEEE Transactions on Circuits and Systems I: Regular Papers,61(6), 1609–1617. https://doi.org/10.1109/TCSI.2013.2289413.

Trakimas, M., & Sonkusale, S. (2009). A 0.5 V bulk-input OTA with improved common-mode feedback for low-frequency filtering applications. Analog Integrated Circuits and Signal Processing,59(1), 83–89. https://doi.org/10.1007/s10470-008-9236-z.

Suda, N., Nishanth, P. V., Basak, D., Sharma, D., & Paily, R. P. (2014). A 0.5-V low power analog front-end for heart-rate detector. Analog Integrated Circuits and Signal Processing,81(2), 417–430. https://doi.org/10.1007/s10470-014-0402-1.

Akbari, M., & Hashemipour, O. (2016). A 0.6-V, 0.4-µW bulk-driven operational amplifier with rail-to-rail input/output swing. Analog Integrated Circuits Signal Processing,86(2), 341–351.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Faraji Baghtash, H. A 0.4 V, tail-less, fully differential trans-conductance amplifier: an all inverter-based structure. Analog Integr Circ Sig Process 104, 1–15 (2020). https://doi.org/10.1007/s10470-020-01662-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-020-01662-5