Abstract

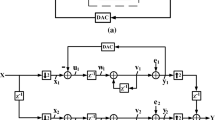

A novel and simple circuit technique to relax the feedback timing of input feed-forward ΔΣ analog-to-digital converter (ADC) is proposed for wideband and high-accuracy applications. The proposed method allows the use of low-speed comparator and DEM logic even for high-speed operation which helps to reduce the power consumption. A delta-sigma ADC with relaxed feedback timing was designed and simulated. The results verify the advantages of the proposed technique.

Similar content being viewed by others

References

Nam, K., Lee, S. M., Su, D. K., & Wooley, B. A. (2005). A low-voltage low power sigma-delta modulator for broadband analog-to-digital converter. IEEE Journal of Solid-State Circuits, 40(9), 1855–1864.

Zanbaghi, R., Saxena, S., Temes, G. C., & Fiez, T. S. (2012). A 75-dB SNDR, 5-MHz bandwidth stage-shard 2-2 MASH ΔΣ modulator dissipating 16 mW power. IEEE Transactions on Circuits Systems Ι: Regular Papers, 59(8), 1614–1625.

Silva, J., Moon, U., Steensgaard, J., & Temes, G. C. (2001). Wideband low-distortion ΔΣ ADC topology. Electronics Letters, 37(12), 737–738.

Gharbiya, A., & Johns, D. A. (2006). On the implementation of input-feedforward delta-sigma modulator. IEEE Transactions on Circuits Systems II: Express Briefs, 53(6), 453–457.

Kanazawa, Y., Fujimoto, Y., Re, P. L., & Miyamoto, M. (2006). A 100-MS/s 4-MHz bandwidth 77.3-dB SNDR ΔΣ ADC with a triple sampling technique. In IEEE Custom Integrated Circuits Conference (CICC), pp. 53–56.

Lee, K., Miller, M. R., & Temes, G. C. (2009). An 8.1 mW, 82 dB delta-sigma ADC with 1.9 MHz BW and −98 dB THD. IEEE Journal of Solid-State Circuits, 44(8), 2202–2211.

Fogleman, E., Welz, J., & Galton, I. (2000). An audio ADC delta-sigma modulator with 100 dB SINAD and 102 dB DR using a second-order mismatch-shaping DAC. In IEEE Custom Integrated Circuits Conference (CICC), pp. 17–20.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Jung, Y., Temes, G.C. A simple circuit technique to relax the feedback timing of ΔΣ ADC for high-speed and high-accuracy applications. Analog Integr Circ Sig Process 92, 219–223 (2017). https://doi.org/10.1007/s10470-017-0993-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-017-0993-4