Abstract

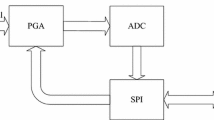

This paper presents a low power CMOS feedforward automatic gain control (AGC) amplifier based on an integrated received signal strength indicator (RSSI) with process-variation tolerance. Low ripple high dynamic RSSI and fast settling AGC are both achieved with a power-efficient implementation. Raised feedforward AGC amplifier also gets superior linearity to cascade ones due to its high dynamic range detection to input signals. No external component is needed and this design was fabricated in 0.18 μm CMOS process. The measurement results show that RSSI gains at least 60-dB log-linear range and the AGC convergence time is less than 7.8-μs for a 2 MHz signal. It draws 1.1 mA from a 1.5 V supply and obtains −52-dB THD with 0.7 Vpp output voltage.

Similar content being viewed by others

References

Khoury, J. M. (1998). On the design of constant settling time AGC circuits. IEEE Transactions on Circuits & Systems II Analog & Digital Signal Processing, 45(3), 283–294.

Mercy, D. V. (1981). A review of automatic gain control theory. Radio & Electronic Engineer, 51(11–12), 579–590.

Heydon, R. (2012). Bluetooth low energy: The developer’s handbook. Upper Saddle river: Prentice Hall.

Zhang, Y., Liu, Y. H., Bachman, C., Dolmans, G., de Groot Holst, H. 2014. A fast convergence two-stage AGC for a Bluetooth low energy radio with 84dB tuning range. In IEEE 25th Annual international symposium on personal, indoor, and mobile radio communication (PIMRC), 2014 (pp. 1921–1925). IEEE.

Liu, Y. H., Bachmann, C., Wang, X. X., Zhang, Y., Ba, A. A., Büsze, B. B., Ding, M. M., Harpe, P., Schaik, V. G., Selimis, G., et al. 2015. In International Solid-state Circuits Conference (pp. 22–26). IEEE.

Alegre, J. P., Celma, S., Calvo, B., Fiebig, N., & Halder, S. (2009). SiGe analog AGC circuit for an 802.11 a WLAN direct conversion receiver. IEEE Transactions on Circuits and Systems II: Express Briefs, 56(2), 93–96.

Perez, J. P. A., Calvo, B., & Celma, S. (2010). A high-performance CMOS feedforward AGC circuit for a WLAN receiver. IEEE Transactions on Industrial Electronics, 57(8), 2851–2857.

Cheng, X., Yang, H., Gao, T., Yin, T., Mu, W., & Zhang, H. (2013). A feed-forward AGC circuit with 48 dB-gain range, 1.2 \(\mu\)s minimum settling time for WiMAX receiver. Analog Integrated Circuits and Signal Processing, 76(1), 61–71.

Jeon, O., Fox, R. M., & Myers, B. A. (2006). Analog AGC circuitry for a CMOS WLAN receiver. IEEE Journal of Solid-State Circuits, 41(10), 2291–2300.

Khorram, S., Rofougaran, A., Abidi, A. 1995. A CMOS limiting amplifier and signal-strength indicator. In Symposium on VLSI Circuits, 1995. Digest of Technical Papers (pp. 95–96). IEEE.

Tian, X., Bai, C., Wu, J., Zhang, M., & Ji, X. (2014). A low power dB-linear RSSI based on logarithmic amplifier. IEICE Electronics Express, 11(12), 20140431.

Wu, C. P., & Tsao, H. W. (2005). A 110-MHz 84-dB CMOS programmable gain amplifier with integrated RSSI function. IEEE Journal of Solid-State Circuits, 40(6), 1249–1258.

Kimura, K. (1993). A CMOS logarithmic IF amplifier with unbalanced source-coupled pairs. IEEE Journal of Solid-State Circuits, 28(1), 78–83.

Calvo, B., Celma, S., & Sanz, M. (2006). Low-voltage low-power 100 MHz programmable gain amplifier in 0.35 \(mu\)m CMOS. Analog Integrated Circuits and Signal Processing, 48(3), 263–266.

Shi, Z., Yang, Y., & Li, D. (2015). A low-power ADC with compact AGC loop for LR-WPAN receivers. Analog Integrated Circuits and Signal Processing, 84(1), 9–18.

Acknowledgments

This work was supported by The Scientific Research Foundation of Graduate School of Southeast University under the Project Number of YBJJ1557, and The National Natural Science Foundation of China under the Project Numbers of 61401090 and 61574035.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bai, C., Wu, J. & Zhang, M. A CMOS low power fast-settling AGC amplifier based on integrated RSSI. Analog Integr Circ Sig Process 87, 379–387 (2016). https://doi.org/10.1007/s10470-016-0730-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0730-4