Abstract

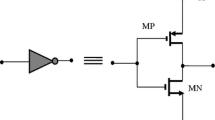

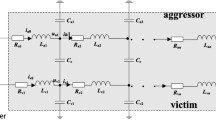

Ultra-low power designs extensively exploit the sub-threshold region of operation of Complementary metal-oxide semiconductor (CMOS) circuits. Though sub-threshold circuit operation shows huge potential towards satisfying the ultra-low power requirement, increased crosstalk and delay have become serious design challenges particularly for sub-threshold interconnects. In this paper, novel analytical time-domain models governing the output voltage and crosstalk-induced delay of CMOS gates driving coupled resistive–capacitive interconnect in sub-threshold domain are presented. Subsequently, the transient analysis of simultaneously switching two and three coupled interconnects is carried out. It is demonstrated that the modeling of driver by linear resistance can lead to about 38 % average error in the estimation of propagation delay. The numerical results illustrate that the proposed model quite accurately estimates the performance of coupled on-chip interconnects. An average error of less than 7 % is observed in estimation of waveform shape and delay.

Similar content being viewed by others

References

Agarwal, K., Sylvester, D., & Blaauw, D. (2006). Modeling and analysis of crosstalk noise in coupled RLC interconnects. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 25(5), 892–901.

Wang, A., Calhoun, B. H., & Chandrakasan, A. P. (2006). Sub-threshold design for ultra low-power systems. New York: Springer.

Calhoun, B.H., Wang, A., Chandrakasan, A. (2004) Device sizing for minimum energy operation in subthreshold circuits, in Proceedings of the IEEE Custom Integrated Circuits Conference, pp. 95–98.

Fathabadi, H. (2013). Ultra low power improved differential amplifier. Circuits, Systems, and Signal Processing, 32(2), 861–875.

Calhoun, B. H., & Chandrakasan, A. (2005). Modeling and sizing for minimum energy operation in subthreshold circuits. IEEE Journal of Solid-State Circuits, 40(9), 1778–1786.

Soeleman, H., & Roy, K. (2000) Digital CMOS logic operation in the subthreshold region, in Proceedings of the ACM Great Lakes VLSI Design Symposium, USA, pp. 107–112.

Bothra, S., Rogers, B., Kellam, M., & Osburn, C. M. (1993). Analysis of the effects of scaling on interconnect delay in ULSI circuits. IEEE Transactions on Electron Devices, 40(3), 591–597.

Ismail, Y., & Friedman, E. G. (2000). Effects of inductance on the propagation delay and repeater insertion in VLSI circuits. IEEE Transaction on Very Large Scale Integration Systems, 8(2), 195–206.

Guoqing, C., & Friedman, E. G. (2006). Low power repeaters driving RC and RLC interconnects with delay and bandwidth constraints. IEEE Transaction on Very Large Scale Integration Systems, 14(2), 161–172.

Gupta, S.K., Raychowdhary, A., Roy, K. (2010) in Proceedings of the IEEE Digital computation in subthreshold region for ultra low-power operation: A device-circuit-architecture codesign perspective, pp. 160–190.

Anderson, J. H., & Najm, F. N. (2009). Low power programmable FPGA routing circuitry. IEEE Transaction on Very Large Scale Integration Systems, 17(8), 1048–1060.

Kil, J., Gu, J., & Kim, C. H. (2008). A high-speed variation-tolerant interconnect technique for sub-threshold circuits using capacitive boosting. IEEE Transaction on Very Large Scale Integration Systems, 16(4), 456–465.

Ho, Y., Chen, H. K., & Su, C. (2012). Energy-effective sub-threshold interconnect design using high-boosting predrivers. IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 2(2), 307–313.

Nanua, M., & Blaauw D. (2007) Investigating crosstalk in sub-threshold circuits, in International Symposium on Quality Electronic Design, San Jose, pp. 639–646.

Chandel, R., Sarkar, S., & Agarwal, R. P. (2007). An analysis of interconnect delay minimization by low-voltage repeater insertion. Microelectronics Journal, 38(4–5), 649–655.

Alioto, M. (2010). Understanding DC behavior of subthreshold CMOS logic through closed-form analysis. IEEE Transactions on Circuits and Systems I, 57(7), 1597–1607.

Davis, J. A., & Meindl, J. D. (2000). Compact distributed RLC models, part II: Coupled line transient expressions and peak crosstalk in multilevel networks. IEEE Transactions on Electron Devices, 47(11), 2078–2087.

Dhiman, R., & Chandel, R. (2014). Crosstalk analysis of CMOS buffer driven interconnects for ultra-low power applications. Journal of Computational Electronics, 13(2), 360–369.

Predictive Technology Model (PTM), http://ptm.asu.edu. Accessed 21 March 2014.

Venkatesan, R., Davis, J. A., & Meindl, J. D. (2003). Compact distributed RLC interconnect models—Part III: Transients in single and coupled lines with capacitive load termination. IEEE Transactions on Electron Devices, 50(4), 1081–1093.

Cui, J., Zhao, W., Yin, W., & Hu, J. (2012). Signal transmission analysis of multilayer graphene nano-ribbon interconnects. IEEE Transactions on Electromagnetic Compatibility, 54(1), 126–132.

Tang, K.T., & Friedman, E.G. (2000) Delay and power expressions characterizing a CMOS inverter driving an RLC load, in Proceedings of the IEEE Circuits and Systems Symposium, Geneva, pp. 283–286.

Author information

Authors and Affiliations

Corresponding author

Appendix 1: one or more transistors operate in the sub-linear region

Appendix 1: one or more transistors operate in the sub-linear region

For a three-line coupled system, it is assumed that Inv1 leaves the sub-saturation region first, followed by Inv2 and finally Inv3 entering the sub-linear region. The solutions of the output voltage when one or more active transistors in each CMOS inverter enter into the sub-linear region are now derived.

1.1 Inv1 operates in the sub-linear region

When Inv1 begins operating in the sub-linear region, the discharge currents of Inv2 and Inv3 are constant, being equal to \(B_{n2}\) and \(B_{n3}\), respectively. Therefore, the differential equations in a three-line coupled system become,

Applying a Laplace transform to (72), (73) and (74), following set of equations are produced,

Let the various coefficients be defined as,

Eqs. (75–77), thus are of the type,

Eqs. (88–90) are solved to obtain,

1.2 Both Inv1 and Inv3 operate in the sub-linear region

When Inv1 and Inv3 operate in the sub-liner region, the discharge current of Inv2 is a constant i.e. dI2/dt = 0. Therefore, the differential Eqs. (72–74) become,

Applying a Laplace transform to (94), (95) and (96), a solution of the output voltages V1(s), V2(s) and V3(s) is produced. These expressions maintain the same formulation as (A.17)-(A.19). The various coefficients obtained are,

1.3 Inv1, Inv2 and Inv3 all operate in the sub-linear region

When Inv1, Inv2 and Inv3 operate in the sub-liner region, the differential Eqs. (72–74) become,

Applying a Laplace transform to (107)–(109), a solution of the output voltages V1(s), V2(s) and V3(s) is produced. The various coefficients obtained are,

Rights and permissions

About this article

Cite this article

Dhiman, R., Sharma, R. & Chandel, R. Compact models and delay computation of sub-threshold interconnect circuits. Analog Integr Circ Sig Process 84, 53–65 (2015). https://doi.org/10.1007/s10470-015-0557-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0557-4