Abstract

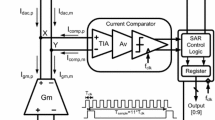

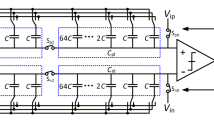

This paper presents a 10b 100 MS/s monotonic switching SAR ADC with system-level error correction of offset and noise tolerant technique. The error-correction structure involves a noise and offset controllable comparator and a redundant comparison cycle. The comparator operates in faster but larger offset and noise mode in MSB conversions, which is adjusted to slower but smaller offset and noise mode in LSB conversion after redundant cycle. At 10b resolution, the system is able to tolerate \(\pm 16\) LSB offset and noise errors with different transistor mismatches in the comparator. The designed 0.13 \(\upmu\)m 10b 100 MS/s SAR ADC incorporates an asynchronous control logic with manually controllable current source and speed acceleration technique. 9.54b ENOB is achieved at 100 MS/s under 3\(\sigma\) offset mismatch condition while only 8.36b ENOB is achieved without error correction. The post-layout simulated ENOB and power consumption is 9.37b and 1.7 mW under 1.2 V supply, resulting in a 25.7 fJ/conversion-step figure of merit.

Similar content being viewed by others

References

Giannini, V., Nuzzo, P., Chironi, V., Baschirotto, A., der Plas, G.V., & Craninckx, J. (2008). An 820\(\mu\)W 9b 40MS/s noise-tolerant dynamic-SAR ADC in 90nm digital CMOS. Proceedings IEEE ISSCC Tech. Dig., (pp. 238–239).

Yoshioka, M., Ishikawa, K., Takayama, T., & Tsukamoto, S. (2010). A 10-b 50-MS/s 820-\(\mu\)W SAR ADC with on-chip digital calibration. IEEE Transactions on Biomedical Circuits Systems, 4(6), 410–416.

Cho, Y. K., Jeon, Y. D., Nam, J. W., & Kwon, J. K. (2010). A 9-bit 80 MS/s successive approximation register analog-to-digital converter with a capacitor reduction technique. IEEE Transactions on Circuits and Systems II: Express Briefs, 57(7), 502–506.

Liu, C. C., Chang, S. J., Huang, G. Y., & Lin, Y. Z. (2010). A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE Journal of Solid-State Circuits, 45(4), 731–740.

Zhu, Y., Chan, C. H., Chio, U. H., Sin, S. W., Seng-Pan, U., Martins, R. P., et al. (2010). A 10-bit 100-MS/s Reference-Free SAR ADC in 90 nm CMOS. IEEE Journal Solid State Circuits, 45(6), 1111–1121.

Liu, C.C., Chang, S.J., Huang, G.Y., Lin, Y.Z., Huang, C.M., Huang, C.H., Bu, L., & Tsai, C.C. (February 2010). A 10b 100MS/s 1.13mW SAR ADC with binary-scaled error compensation. Proceedings IEEE ISSCC Tech. Dig., (pp. 386–387).

Vitek, R., Gordon, E., Maerkovich, S., & Beidas, A. (September 2012). A 0.015mm\(^2\) 63fJ/conversion-step 10-Bit 220MS/s SAR ADC with 1.5b/step redundancy and digital metastability correction. |textitProceedings IEEE Custom Integr. Circuits Conf., (pp. 1–4).

Fredenburg, J., & Flynn, M. (February 2012). A 90MS/s 11MHz bandwidth 62dB SNDR noise-shaping SAR ADC. Proceedings IEEE ISSCC Tech. Dig., (pp. 468–469).

Lin, Y. Z., Liu, C. C., Huang, G. Y., Shyu, Y. T., Liu, Y. T., & Chang, S. J. (2013). A 9-bit 150-MS/s subrange ADC based on SAR architecture in 90-nm CMOS. IEEE Transactions on Circuits and Systems I: Regular Papers, 60(3), 570–581.

Morie, T., Miki, T., Matsukawa, K., Bando, Y., Okumoto, T., Obata, K., Sakiyama, S., & Dosho, S. (February 2013). A 71dB-SNDR 50MS/s 4.2mW CMOS SAR ADC by SNR enhancement techniques utilizing noise. Proceedings IEEE ISSCC Tech. Dig., (pp. 273–274).

Huang, G. Y., Chang, S. J., Liu, C. C., & Lin, Y. Z. (2013). 10-bit 30-MS/s SAR ADC using a switchback switching method. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 21(3), 584–588.

Wong, S. S., Chio, U. F., Zhu, Y., Sai-Weng Sin, S. P. U., & Martins, R. P. (2013). A 2.3 mW 10-bit 170 MS/s two-step binary-search assisted time-interleaved SAR ADC. IEEE Journal Solid State Circuits, 48(8), 1783–1794.

Hariprasath, V., Guerber, J., Lee, S. H., & Moon, U. K. (2010). Merged capacitor switching based SAR ADC with highest switching energy-efficiency. Electronics Letters, 46(9), 620–621.

Schinkel, D., Mensink, E., Klumperink, E., van Tuijl, E., & Nauta, B. (February 2007). A double-tail latch-type voltage sense amplifier with 18ps setup+hold time. Proceedings IEEE ISSCC Tech., (pp. 314–315).

Acknowledgments

This work was supported by the National Natural Science Foundation of China (61006027), the New Century Excellent Talents Program of China (NCET-10-0297), the National Program for Support of Top-Notch Young Professionals (1st Batch), and the National Key Laboratory of Analog Integrated Circuits (9140C090102130C09039).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gao, J., Li, G. & Li, Q. A monotonic SAR ADC with system-level error correction. Analog Integr Circ Sig Process 84, 1–8 (2015). https://doi.org/10.1007/s10470-015-0543-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0543-x