Abstract

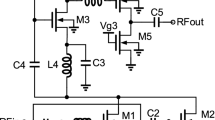

A triple cascaded current-reuse CMOS low noise amplifier for 3.5 GHz WiMAX application is presented. Three common-source amplifiers are stacked and reuse the same current. This triple cascaded topology is able to enhance power gain but needs two coupling networks which costs enormous chip size. In order to have reasonable chip size, two coupling methods are investigated. For obtaining simultaneous input and noise matching, an additional capacitor is employed to adjust quality factor and reduce the gate induced current noise. The measurement results show a maximum power gain of 21.7 dB and minimum noise figure of 3.11 dB. The chip size is 1.05 mm \(\times\) 0.93 mm including all pads and the power consumption is 5.16 mW with a supply voltage of 1.5 V. A figure-of-merit of 49.7 is reached.

Similar content being viewed by others

References

IEEE Standard for Local and Metropolitan Area Networks Part 16: (2004) Air Interface for Fixed Broadband Wireless Access Systems, IEEE 802.16-2004 Std.

Razavi, B. (1997). RF Microelectronics. New Jersey, NJ: Prentice-Hall.

Wang, Y., & Lu, L.-H. (2005). 5.7 GHz low-power variable-gain LNA in 0.18 \(\mu\)m CMOS. Electronics Letters, 41(2), 66–68.

Cha, C.-Y., & Lee, S.-G. (2003). A 5.2-GHz LNA in 0.35-\(\mu\)m CMOS utilizing inter-stage series resonance and optimizing the substrate resistance. IEEE Journal of Solid-State Circuits, 38(4), 669–672.

Liao, C.-H., & Chuang, H.-R. (2003). A 5.7-GHz 0.18-\(\mu\)m CMOS gain-controlled differential LNA with current reuse for WLAN receiver. IEEE Microwave and Wireless Components Letters, 13(12), 526–528.

Wei, M.-D., Chang, S.-F., & Liu, Y.-C. (2008). A low-power ultra-compact CMOS LNA with shunt-resonating current-reused topology. In Proceeding of the European Microwave Integrated Circuits Conference (EuMIC), pp. 350–353.

Shaeffer, D., & Lee, T. (1997). A 1.5-V, 1.5-GHz CMOS low noise amplifier. IEEE Journal of Solid-State Circuits, 32(5), 745–759.

Kim, Y. M., Han, H., & Kim, T. W. (2013). A 0.6-V +4 dBm IIP3 LC folded cascode CMOS LNA with gm linearization. IEEE Transaction on Circuits and Systems II, 60(3), 122–126.

Andreani, P., & Sjöland, H. (2001). Noise optimization of an inductively degenerated CMOS low noise amplifier. IEEE Transactions on Circuits and Systems II, 48(9), 835–841.

Nguyen, T.-K., Kim, C.-H., Ihm, G.-J., Yang, M.-S., & Lee, S.-G. (2004). CMOS low-noise amplifier design optimization techniques. IEEE Transactions and Microwave Theory and Techniques, 52(5), 1433–1442.

Chang, C.-P., Chen, J.-H., & Wang, Y.-H. (2009). A fully integrated \(5\) GHz low-voltage LNA using forward body bias technology. IEEE Microwave and Wireless Components Letters, 19(3), 176–178.

Walling, J., Shekhar, S., & Allstot, D. (2007). A \(g_m\)-boosted current-reuse LNA in 0.18 \(\mu\)m CMOS. In Proceedings of the RFIC Symposium, pp. 613–616.

Lee, H., & Mohammadi, S. (2006). A 3 GHz subthreshold CMOS low noise amplifier. In Proceedings of the RFIC Symposium.

Hsiao, Y.-W., & Ker, M.-D. (2008). An ESD-protected 5-GHz differential low-noise amplifier in a 130-nm CMOS process. In Proceedings of the IEEE Custom Integrated Circuits Conference, pp. 233–236.

Rashtian, H., & Mirabbasi, S. (2014). Applications of body biasing in multistage CMOS low-noise amplifiers. IEEE Transactions on Circuits and Systems I, 99, 1–10.

Lai, M.-T., & Tsao, H.-W. (2013). Ultra-low-power cascaded CMOS LNA with positive feedback and bias optimization. IEEE Transactions on Microwave Theory and Techniques, 61(5), 1934–1945.

Acknowledgments

The authors would like to thank the German Federal Ministry of Education and Research (BMBF) under Grant No. 03V023 “LeiCMOS”, National Science Council (NSC), Taiwan, and Chip Implementation Center (CIC), Taiwan for funding and implementing this work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wei, MD., Chang, SF. & Negra, R. Triple cascaded current-reuse low noise amplifier. Analog Integr Circ Sig Process 80, 327–333 (2014). https://doi.org/10.1007/s10470-014-0334-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-014-0334-9