Abstract

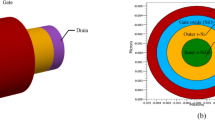

Increasing demand for low power consumption with faster operating speed at nanoscale while overpowering the issue of mobility degradation due to short channel effects, strained silicon technology based devices proved to be a promising substitute for future nano-device applications. The strain induced quantum well (QW) based nano-system device is developed deploying ultrathin strained HOI structure comprising of s-SiGe QW sandwiched between two s-Si layers, thus instigating biaxial strain in the channel region. With introduction of strain mechanism and band-bending, bandgap modification occurs resulting in formation of quantum well-barrier system in narrow channel, thereby confining charge carriers and sufficing ballistic transport via quantum tunneling with high electron velocity. Hence, a fundamental physical phenomenon of succumbing of quantum charge carriers that initiate in carrier transport within the strained induced QW based nano-system device is estimated. The electrostatic potential, electric field and mobility are calculated analytically, analyzed and compared for 10 nm and 22 nm tri-layered channel nano-system devices. The resulting drain current of the novel 10 nm strain induced QW nano-system device when compared with 22 nm strained DG FET and with existing conventional 10 nm DG SOI FET an enormous enrichment of 97.7% and 40.3%, respectively, is perceived. Hence the novel device instituted, demonstrates its competence to accomplish the technological requirement at nano regime.

Similar content being viewed by others

Data availability

All authors certify that they have no affiliations with or involvement in any organization or entity with any financial interest or non-financial interest in the subject matter or materials discussed in this manuscript.

Code availability

The authors have no financial or proprietary interests in any material discussed in this article.

References

Basak A, Chanda M, Sarkar A (2019) Drain current modelling of unipolar junction dual material double-gate MOSFET (UJDMDG) for SoC applications. Microsyst Technol. https://doi.org/10.1007/s00542-019-04691-x

Chakrabarti H, Maity R, Maity NP (2019) Analysis of surface potential for dual-material-double-gate MOSFET based on modeling and simulation. Microsyst Technol 25(12):4675–4684. https://doi.org/10.1007/s00542-019-04386-3

Dhar RS, Khiangte L, Kumar K (2019) Strain engineering analysis for nanoscaled tri-layered heterostructure-on-insulator. Int J Nanosci. https://doi.org/10.1142/S0219581X20400013

Hariharan V, Vasi J, Rao VR (2008) Drain current model including velocity saturation for symmetric double-gate MOSFETs. IEEE Trans Electron Devices 55(8):2173–2180. https://doi.org/10.1109/TED.2008.926745

Karazhanov SZ, Davletova A, Ulyashin A (2008) Strain-induced modulation of band structure of silicon. J Appl Phys 104(2):024501. https://doi.org/10.1063/1.2940135

Kasturi P, Saxena M, Gupta M, Gupta RS (2007) Dual material double-layer gate stack SON MOSFET: a novel architecture for enhanced analog performance—part I: impact of gate metal workfunction engineering. IEEE Trans Electron Device 55(1):372–381. https://doi.org/10.1109/TED.2007.910564

Khiangte L, Dhar RS (2018) Development of tri-layered s-Si/s-SiGe/s-Si channel heterostructure-on-insulator MOSFET for enhanced drive current. Phys Stat Solidi b 255(8):1800034. https://doi.org/10.1002/pssb.201800034

Kumar MJ, Singh TV (2008) Quantum confinement effects in strained silicon mosfets. Int J Nanosci 7(02n03):81–84. https://doi.org/10.1142/S0219581X08005195

Kumar K, Khiangte L, Dhar RS (2020) Design of DG MOSFET with tri-layered strained silicon channel. J Phys ConfSer 1478:012002. https://doi.org/10.1088/1742-6596/1478/1/012002

Li Y, Chou H-M (2005) A comparative study of electrical characteristic on sub-10-nm double-gate MOSFETs. IEEE Trans Nanotechnol 4(5):645–647. https://doi.org/10.1109/TNANO.2005.851440

Li G, Yao K, Gao G (2017) Strain-induced enhancement of thermoelectric performance of TiS2 monolayer based on first-principles phonon and electron band structures. Nanotechnology 29(1):015204

Lin HN, Chen HW, Ko CH, Ge CH, Lin HC, Huang TY, Lee WC (2006) Correlating drain-current with strain-induced mobility in nanoscale strained CMOSFETs. IEEE Electron Device Lett 27(8):659–661. https://doi.org/10.1109/LED.2006.878035

Nowak EJ, Alle I, Ludwig T, Kim K, Joshi RV, Chuang CT, Bernstein K, Puri R (2004) Turning silicon on its edge. IEEE Circuits Devices Mag 20(1):20–31. https://doi.org/10.1109/MCD.2004.1263404

Patrick R, Hans R (2002) High-speed heterostructure devices: from device concepts to circuit modeling. Cambridge University Press, Cambridge

Saha P, Kumari T, Sarkar SK (2019) Analytical modelling and performance analysis of dielectric pocket-induced double-gate tunnel field-effect transistor. IETE Tech Rev 36(117):26. https://doi.org/10.1080/02564602.2017.1381049

Sanuki T, Oishi A, Morimasa Y, Aota S, Kinoshita T, Hasumi R, Takegawa Y, Isobe K, Yoshimura H, Iwai M, Sunouchi K (2003) Scalability of strained silicon CMOSFET and high drive current enhancement in the 40 nm gate length technology. In: IEEE international electron devices meeting, IEEE, pp 3–5. https://doi.org/10.1109/IEDM.2003.1269167

Taur Y (2000) An analytical solution to a double-gate MOSFET with undoped body. IEEE Electron Device Lett 21(5):245–247. https://doi.org/10.1109/55.841310

Taur Y, Ning TH (1998) Fundamentals of modern VLSI devices. Cambridge University Press, Cambridge

Vaidyanathan S (2010) Multiple gate field-effect transistors for future CMOS technologies. IETE Tech Rev 27(6):446–454. https://doi.org/10.4103/02564602.2010.10876778

Wakabayashi H, Yamagami S, Ikezawa N, Ogura A, Narihiro M, Arai KI, Ochiai Y, Takeuchi K, Yamamoto T, Mogami T (2003) Sub-10-nm planar-bulk-CMOS devices using lateral junction control. In: IEEE international electron devices meeting, 7–10 Dec, pp 20.7.1–20.7.4. https://doi.org/10.1109/IEDM.2003.1269446

Wang EX, Matagne P, Shifren L, Obradovic B, Kotlyar R, Cea S, Stettler M, Giles MD (2006) Physics of hole transport in strained silicon MOSFET inversion layers. IEEE Trans Electron Devices 53(8):1840–1851. https://doi.org/10.1109/TED.2006.877370

Yan L, Olsen SH, Kanoun M, Agaiby R, O’Neill AG (2006) Gate leakage mechanisms in strained Si devices. J Appl Phys 100(10):104507. https://doi.org/10.1063/1.2374191

Yuan T, Liang X, Wang W, Lu H (2004) A continuous, analytic drain-current model for DG MOSFETs. IEEE Electron Device Lett 25(2):107–109. https://doi.org/10.1109/LED.2006.878035

Acknowledgements

The authors thank Dept of ECE, NIT Mizoram for providing facilities and support to carry out this work.

Funding

The authors have no relevant financial or non-financial interests to disclose.

Author information

Authors and Affiliations

Contributions

K.K. conducted the modeling and simulation, analyzed the data, and prepared the figures as first author. R.S.D. being Supervisor of K.K. initiated the research and studied and also contributed to the modeling and developing the novel idea and improvements in the manuscript. R.S.D. is the corresponding author who planned and coordinated the study, contributed to data analysis and wrote to develop the manuscript. S.B. and R.D. supported the theory of the manuscript. All the authors discussed the results and contributed to the manuscript at various stages.

Corresponding author

Ethics declarations

Conflict of interest

The authors declare no conflicts of interest financial or otherwise that are relevant to the content of this article.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Kumar, K., Dhar, R.S., Bhattacharya, S. et al. Performance analysis and development of strain induced quantum well based nano-system device technology. Microsyst Technol 27, 3703–3710 (2021). https://doi.org/10.1007/s00542-020-05143-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-020-05143-7