Abstract

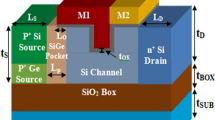

This paper presents the comparative study on linearity and analog/radio frequency presentation of an III–V staggered hetero-junction nanowire (NW) TFET with Si and InAs based NW TFET of same dimension. The device parameter of analog/RF performance for low power application such as transconductance (gm), output resistance (RO), intrinsic gain (gmR0), cut-off frequency (fT), maximum frequency of oscillation (fmax), gain bandwidth product (GBW), VIP2, VIP3 as well as 1-dB compression point has been explored. There is a better improvement in analog/radio frequency presentation obtained from heterojunction NW TFET over Si and InAs TFET. The result reveals that heterojunction TFET provides superior intrinsic gain, higher cutoff frequency, higher GBW better linearity performance as compared to Si and InAs TFET.

Similar content being viewed by others

References

Biswas A, Alper C, De Michielis L, Ionescu AM (2012) New tunnel-FET architecture with enhanced Ion and improved millar effect for energy efficient switching. In: Device research conference (DRC), 2012 70th Annual, pp 131–132

Chakraborty A, Sarkar A (2015) Investigation of analog/RF performance of staggered hetero-junction based nano wire tunneling field-effect transistor. Superlattices Micro Struct 80:125–135

Choi WY, Park B-G, Lee JD, King Liu T-J (2007) Tunneling field -effect transistors (TFETs) with sub threshold swing (SS) less than 60mv/dec. IEEE Electron Dev Lett 28:743–745

Ganjipour B, Wallentin J, Borgström MT, Samuelson L, Thelander C (2012) ACS Nano 6:3109–3113

Gautam R, Saxena M, Gupta RS, Gupta M (2012) Microelectron Reliab 52:989–994

Ghosh P, Haldar S, Gupta RS, Gupta M (2012) An investigation of linearity performance and intermodulation distortion of GME CGT MOSFET for RFIC design. Electron Dev IEEE Trans 59(12):3263–3268

Ionescu AM, Riel H (2011) Tunnel field-effect transistors as energy efficient electronic switches. Nature 479(7373):329–337

Kaya S, Ma W (2004) Optimization of RF linearity in DG MOSFET. IEEE Electron Dev Lett 25(5):308–310

Koswatta SO, Lundstrom MS, Nikonov DE (2009) Performance comparison between p-i-n tunneling transistors and conventional MOSFETs. Electron Dev IEEE Trans 56(3):456–465

Koswatta SO, Koester SJ, Haensch W (2010) IEEE Trans Electron Dev 57:3222–3230

Kumar SP, Agrawal A, Chaujar R, Gupta RS, Gupta M (2011) Microelectron Reliab 51:587–596

Lu H, Seabaugh A (2014) Tunnel field-effect transistors: state-of the-art. IEEE J Electron Dev Soc 2(4):44–49

Mallik A, Chattopadhyay A (2012) Electron Dev IEEE Trans 59:888–894.

Mohankumar N, Syamal B, Sarkar CK (2010) IEEE Trans Electron Dev 57:820–826

Mohata D, Mookerjea S, Agrawal A, Li Y, Mayer T, Narayanan V, Liu A, Loubychev D, Fastenau J, Datta S (2011) Appl Phys Express 4:024105–1–024105-3

Mohata D, Rajamohanan B, Mayer T, Hudait M, Fastenau J, Lubyshev D, Liu AWK, Datta S (2012) IEEE Electron Dev Lett 33:1568–1570

Mookerjea S, Krishnan R, Datta S, Narayanan V (2009) IEEE Electron Dev Lett 30:1102–1104

Pala MG, Esseni D (2013) IEEE Trans Electron Dev 60:2795–2801

Sarkar A, Das AK, De S, Sarkar CK (2012) Microelectron J 43:873–882

Sedighi B, Hu XS, Liu H, Nahas JJ, Niemier M (2014) Circuits and systems I: regular papers. IEEE Trans (4):1–10

Senale-Rodriguez B, Lu Y, Fay P, Jena D, Seabaugh A, Xing HG et al (2012) Perspective of TFETs for low power analog ICs. In: Proceedings IEEE subthreshold microelectronics conference, pp 1–3

Shenoy RS, Saraswat KC (2003) Nanotechnol IEEE Trans 2(4):265–270

Tomioka K, Yoshimura M, Fukui T (2012) Proc VLSI Symp Technol Dig 47–48

Yang Y, Tong X, Yang L-T, Guo P-F, Fan L, Yeo Y-C (2010) Electron Device Lett IEEE 31:752–754

Zhao H, Chen Y, Wang Y, Zhou F, Xue F, Lee J (2011) IEEE Trans Electron Dev 58:2990–2995

Zhu Y, Jain N, Mohata DK, Datta S, Lubyshev D, Fastenau JM, Liu AK, Hudait MK (2012) Appl Phys Lett 101:112106–1–112106-4

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Biswal, S.M., Baral, B., De, D. et al. Simulation and comparative study on analog/RF and linearity performance of III–V semiconductor-based staggered heterojunction and InAs nanowire(nw) Tunnel FET. Microsyst Technol 25, 1855–1861 (2019). https://doi.org/10.1007/s00542-017-3642-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-017-3642-z