Abstract

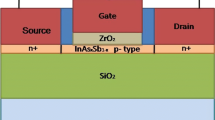

In this paper, we develop the low frequency noise (LFN) model for symmetric double gate InAsSb channel n-MOSFETs and report noise performance of such devices as well as amplifier circuits built using them. Our noise model relies on the drain current Id which is obtained from the carrier concentration and Pao-Sah’s current formulation taking into account field dependent electron mobility and interface trapped-charge density Dit. The drain current model is calibrated with reported experimental data. The calculated values of Id and transconductance gm are utilized to find power spectral density of drain current as a function of drain and gate bias voltages, channel length, channel thickness, equivalent oxide thickness and also Dit. Moreover, we have studied the performance of low noise amplifiers (LNAs) with simultaneous noise and input matching (SNIM) topology using both InAsSb and Si channel devices, and computed the minimum noise figure and output noise power density and compared the results. Our investigation reveals that InAsSb MOSFETs exhibit better low noise performance in the strong inversion region of operation at which devices are biased to operate usually for analog circuit applications. Furthermore, the LNA with InAsSb channel MOSFET exhibits noise figure of 1.38 dB in strong inversion region enabling the amplifier suitable for many applications.

Similar content being viewed by others

References

Ali A, Madan H, Barth MJ, Boos JB, Bennett BR, Datta S (2013a) Effect of interface states on the performance of Antimonide nMOSFETs. IEEE Trans Electron Devices 34(3):360–362

Ali A, Madan H, Misra R, Agrawal A, Schiffer P, Boos JB, Bennett BR, Datta S (2013b) Experimental determination of quantum and centroid capacitance in arsenide–antimonide quantum-well MOSFETs incorporating nonparabolicity effect. IEEE Trans Electron Devices 58(5):1397–1403

Bhattacherjee S, Biswas A (2011) Performance analysis of long Ge channel double gate (DG) p MOSFETs with high-k gate dielectrics based on carrier concentration formulation. Microelectron Reliab 51(8):1105–1112

Bhattacherjee S, Biswas A (2014) Analog circuit performance of high ultrathin-body InAsSb-on-insulator MOSFETs. In: Proceedings of IEEE Students' Technology Symposium (TechSym). doi:10.1109/TechSym.2014.6808084

Datta S et al (2005) 85 nm gate length enhancement and depletion mode InSb quantum well transistors for ultra high speed and very low power digital logic applications. In: Proceedings of conference on international electron devices meeting (IEDM) technical digest. doi:10.1109/IEDM.2005.1609466

del Alamo JA (2011) Nanometre-scale electronics with III–V compound semiconductors. Nature 479:317–323

Fang H, Chuang S, Takei K, Kim HS, Plis E, Liu CH, Krishna S, Javey A (2012) Ultrathin-body high-mobility InAsSb-on insulator field effect transistors. IEEE Electron Device Lett 33(4):504–506

Fellas K, Mavredakis N, Pflanzl W, Seebacher E, Bucher M (2014) Simple 1/f noise parameter extraction method for high-voltage MOSFETs. In: 29th international conference on microelectron proceedings-MIEL. doi:10.1109/MIEL.2014.6842092

Guo W, Nicholas G, Kaczer B, Todi RM, De Jaeger B, Claeys C, Mercha A, Simoen E, Cretu B, Routoure J-M, Carin R (2007) Low-frequency noise assessment of silicon passivated Ge pMOSFETs with TiN/TaN/HfO2 gate stack. Electron Device Lett 28(4):288–291

Haartman MV, Osting M (2007) Low frequency noise in advanced MOS devices. Springer, Netherlands

Liu W, Padovani A, Larcher L, Raghavan N, Leong Pey K (2014) Analysis of correlated gate and drain random telegraph noise in post-soft breakdown TiN/HfLaO/SiOnMOSFETs. IEEE Trans Electron Device Lett 35(2):157–159

Magnone P, Crupi F, Giusi G, Pace C, Simoen E, Claeys C, Pantisano L, Maji D, Rao VR, Srinivasan P (2009) 1/f noise in drain and gate current of MOSFETs with high-k gate stacks. IEEE Trans Device Mater Reliab 9(2):180–189

Mondal C, Biswas A (2012) Studies on halo implants in controlling short-channel effects of nanoscale Ge channel pMOSFETs. IEEE Trans Electron Devices 59(9):2338–2344

Mondal C, Biswas A (2013) 2-D compact model for drain current of fully depleted nanoscale GeOI MOSFETs for improved analog circuit design. IEEE Trans Electron Devices 60(8):2525–2531

Nguyen TK, Kim CH, Ihm GH, Yang MS, Lee SG (2004) CMOS low noise amplifier design optimization technique. IEEE Trans Microw Theory Tech 52(5):1433–1442

Sakong SH, Lee SH, Rim T, Jo YW, Lee JH, Jeong YH (2015) 1/f noise characteristics of surface-treated normally-off Al2O3/GaN MOSFETs. IEEE Trans Electron Device Lett 36(3):229–231

Scarpino M, Gupta S, Lin D, Alian AR, Crup F, Collaert N, Thean A, Simoen E (2014) Border traps in InGaAs nMOSFETs assessed by low-frequency noise. IEEE Trans Electro Device Lett 35(7):720–722

Shaeffer DK, Lee TH (1997) A 1.5-V, 1.5-GHz CMOS low noise amplifier. IEEE J Solid-State Circuits 32(5):745–759

Shi M, Martin JS, Bournel A, Querlioz D, Wichmann N, Bollaert S, Danneville F, Dollfus P (2013) Monte Carlo analysis of the dynamic behavior of III–V MOSFETs for low-noise applications. Solid-State Electron 8(6):51–57

Simoen E, Claeys C, Chung TM, Flandre D, Raskin J-P (2007) On the origin of the excess low-frequency noise in graded-channel silicon-on-insulator nMOSFETs. IEEE Electron Device Lett 28(10):919–921

Taur Y, Ning TH (2004) Fundamentals of modern VLSI devices. Cambridge University Press, Cambridge

Tewari S, Biswas A, Mallik A (2012) Study of InGaAs-channel MOSFETs for analog/mixed-signal system-on-chip applications. IEEE Electron Device Lett 33(3):372–374

Tewari S, Biswas A, Mallik A (2013) Impact of different barrier layers and indium content of the channel on the analog performance of InGaAs MOSFETs. IEEE Trans Electron Devices 60(5):1584–1589

Tewari S, Biswas A, Mallik A (2016) Impact of a spacer layer on the analog performance of asymmetric InP/InGaAs n-MOSFETs. IEEE Trans Electron Devices 63(6):2313–2320

Wang BC et al (2013) Comparison of the trap behavior between ZrO2 and HfO2 gate stack nMOSFETs by 1/f noise and random telegraph noise. IEEE Electron Device Letts. 34(2):151–153

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Bhattacherjee, S., Biswas, A. Development of noise model for InAsSb MOSFETs and their application in low noise amplifiers. Microsyst Technol 25, 1555–1562 (2019). https://doi.org/10.1007/s00542-017-3466-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00542-017-3466-x