Abstract

Under the traditional hybrid modulation strategy, the output powers of the hybrid cascaded H-bridge inverter are not balanced between the cascaded units. With a hybrid cascaded H-bridge 13-level inverter with a DC side voltage ratio of 1:1:1:3 (referred to as III-inverter in the paper) as the research object, a hybrid modulation power equalization strategy based on carrier rotation is proposed. Under the control of which, the output voltage of inverters is formed by superposition of multiple basic voltage waveforms. Firstly, the hybrid modulation strategy is adopted to modulate the inverter so that the high- and low-voltage units, respectively, operate in the low-frequency and high-frequency states. Then, the pulse sequence within the 3/2 output voltage cycle is made to circulate among all the cascaded units by carrier rotation. Finally, the output voltage of each cascaded units is made to contain all the basic voltage waveforms, thus implementing the output power balance between all the cascaded units. Based on simulation and experiment, the effectiveness of the strategy is verified, and it is shown that under the control of this power balance modulation strategy, the output voltage waveform quality of the inverter is high, there is no current backflow, and the output power can be balanced within 3/2 cycles.

Similar content being viewed by others

1 Introduction

In the electric power industry, the demand of medium and high voltages and high power inverter is increasing. Cascaded H-bridge inverters have obvious advantages such as simple structure, easy modularization, small voltage stress of switching transistors, large output power and good waveform quality of output voltage and have been the research hotspots of multi-level inverters in recent years [1,2,3]. Compared with the traditional cascaded H-bridges, the hybrid cascaded H-bridges can greatly reduce the number of DC power supplies and switching transistors under the condition of the same output levels [4,5,6]. Up to now, the modulation methods of the hybrid cascaded H-bridge inverter mainly include carrier phase-shifting PWM (PS-PWM) and level-shifted PWM (LS-PWM), in which PS-PWM can achieve power balance between cascaded units in the cascaded H-bridge. Compared with the PS-PWM, in-phase disposition PWM(IPD-PWM) can make the inverter output line voltage harmonic characteristics better. In [7,8,9,10,11,12], several hybrid cascaded H-bridge inverters use such modulation strategies as multilayer carrier stacking and hybrid frequency carrier PWM. However, when the number of hybrid cascaded units continues to increase, the modulation method will become more complex and output power between the same cascaded units will be unbalanced.

The output power unbalance between the same cascaded units will not only affect the service life of switching transistors and DC power supplies in H-bridge, but also hinder the maintenance and mass production of inverters in the later stage [13, 14]. In [15], with 1/4 output cycle as a unit, the power balance of the three-unit cascaded, seven-level H-bridge inverter is realized by exchanging the output voltage waveform of each unit H-bridge. In [16,17,18,19,20,21], the power balance between the cascaded H-bridge units is implemented by employing PD and carrier cycle, carrier reconstruction, pulse rotation and other power balance strategies, but the above research objects are all symmetrical cascaded H-bridge inverters. In [22, 23], for different types of hybrid cascaded H-bridges, selected harmonic elimination PWM (SHEPWM), step wave and carrier hybrid modulation are, respectively, applied to a three-unit 15-level inverter and two-unit 7-level inverter, and the output power balance between the units is implemented, but the output voltage waveform quality of the inverters will be affected by the power balance strategies.

In this paper, the III-hybrid cascaded H-bridge inverter is taken as the research object. First of all, in order to make the high-voltage and low-voltage units operate in low-frequency and high-frequency states, respectively, the III-inverter is modulated by the hybrid modulation method of the nearest level control (NLC) to the high-voltage unit and IPD-PWM to the low-voltage unit. Then, the state average method is used to analyze the output power distribution of the inverter under the hybrid modulation strategy and prove that the output powers between cascaded units are imbalanced. Finally, by performing a certain regular rotation cycle on the carrier, the output voltage of the cascaded unit is made to contain all the basic voltage waveforms, and the output power balance of the low-voltage unit is realized on the premise of maintaining the advantages of the modulation for the nearest level control and the in-phase disposition PWM to the III-inverter. Simulation and experiment verify the effectiveness of the proposed power balance strategy in this paper.

2 Modulation strategy of the III-inverter

2.1 Inverter topology and its operating principle

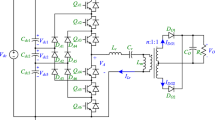

The topology of the III-hybrid cascaded H-bridge inverter is shown in Fig. 1. The DC side voltage of the high-voltage unit H1 is 3E, and the DC side voltage of the low-voltage units L1, L2 and L3 is all E; the output voltages of each H-bridge unit are, respectively, uH1, uL1, uL2, uL3, and the inverter output voltage is a sine wave of u0; the output current is a sine wave of i0. i0 can be expressed as:

where u0 = uH1 + uL1 + uL2 + uL3, I is the amplitude of current i0, ω is the angular frequency of the output voltage and δ is the phase difference between voltage and current.

The output voltage of the high-voltage unit is ± 3E, and the output voltages of the three low-voltage units are all ± E. Thirteen levels of inverter output can be achieved by controlling the on and off of the switch transistor: ± 6E, ± 5E, ± 4E, ± 3E, ± 2E, ± E,0, of which the level ± 5E, ± 4E, ± 3E, ± 2E, ± E, 0 has voltage redundancy.

In order to avoid current backflow between cascaded units, when the inverter outputs a positive voltage, the cascaded unit only outputs a positive voltage of 3E or E or 0, while when the inverter outputs a negative voltage, the cascaded unit only outputs a negative voltage − 3E or − E or 0 (Table 1).

2.2 Hybrid modulation strategy

Hybrid modulation is a modulation method that combines the advantages of the nearest level control and the in-phase disposition PWM, in which the nearest level control is used to modulate the high-voltage unit and the in-phase disposition PWM is used to modulate the low-voltage unit. The purpose of this modulation strategy is to make the high-voltage and low-voltage units operate in low-frequency and high-frequency states, respectively.

The modulation strategy can be described as follows: Firstly, in the positive and negative half cycles, the high-voltage unit modulation wave vH is compared with the two potentials of 3E and − 3E to obtain the high-voltage unit initial driving signal QH1x (x = 1,2,3,4) and make the corresponding switch transistor on, thus obtaining the output voltage waveform of the high-voltage unit in one cycle. Then the low-voltage unit modulation wave vm is compared with the triangular carrier vL1 and vL6, vL2 and vL5, vL3 and vL4 to obtain the initial drive signal QLxy (x = 1,2,3, y = 1,2,3,4) and make the corresponding switch transistor on, thus obtaining the output voltage waveform of the low-voltage unit in one cycle. Finally, the output voltages of the high-voltage and low-voltage units are added to obtain a 13-level output voltage waveform u0. The modulation wave can be expressed as:

where m is the modulation ratio.

Figure 2 shows the modulation principle of the high- and low-voltage units of the III-inverter. It can be seen from the figure in the positive half cycle of the output voltage, the output levels of each unit are + 3E, + E, 0, respectively, while in the negative half cycle, the output levels are − 3E, − E, 0. Therefore, there is no current backflow during the whole cycle.

When vH ≥ 3E, the Fourier expansion of the square wave signal output by the high-voltage unit is:

The Fourier expansion of the output voltage waveform of the high-voltage unit is:

The Fourier expansion of the pulse signal output by the entire low-voltage unit is:

Since the total voltage amplitude on the DC side of the inverter is 6E, the fundamental wave expressions of the total output voltage of the inverter and the output voltages of the high-voltage and low-voltage units can be obtained as:

When E is fixed, the fundamental wave of the total output voltage of inverter only varies with the modulation ratio m. At the same time, the fundamental wave amplitude of the output voltage of the high- and low-voltage units is always smaller than that the total output voltage of the inverter. Therefore, this modulation strategy does not have the problem of current backflow.

3 Power analysis based on the hybrid modulation strategy

3.1 Low-voltage unit power analysis

Assuming that the average output voltage of the low-voltage unit in a switching cycle is uLx, and the duty cycle is dx (x = 1, 2, 3), the average output voltage of the low-voltage unit during a switching cycle can be expressed as:

In practical applications, the frequency of the modulating wave is usually much smaller than the carrier frequency, and it can be considered that the modulating wave in a switching period is a fixed value. Therefore, the duty cycle dx of the low-voltage unit can be expressed as:

Thus, the average output voltage in the positive half cycle can be obtained as:

It can be seen that the average value of the output voltage of the low-voltage unit in the positive half cycle is equal to the instantaneous value of the modulation wave vm. According to the symmetry of the inverter output voltage, the low-voltage unit modulation wave vm can be divided into four regions I, II, III and IV in one cycle. Then, the vm can be divided into 12 basic voltage waveforms uL11 ~ uL34 according to the different cascaded unit. uLx1 ~ uLx4 (x = 1,2,3) are the output voltage waveforms of the four segments of the xth low-voltage unit in one cycle. α1 ~ α5 are the angles corresponding to the intersection of the modulation wave vm with each voltage level within 0 ~ π/2, of which α1 = arcsin(1/6 m), α2 = arcsin(1/3 m), α3 = arcsin(1/2 m), α4 = arcsin(2/3 m), α5 = arcsin(5/6 m).

Figure 3 shows the partitioning principle of the modulation voltage waveform of each low-voltage unit. From the figure, the expressions of the voltages uL11 ~ uL34 in each area in a period can be, respectively, obtained.

In Eqs. (13), (14) and (15) are, respectively, given the voltage expressions of uL11, uL21 and uL31 in area I:

The voltage expressions and principles of the other three regions are the same as them.

Combining Eq. (1),we can get the average output power PLxy of each low-voltage unit under the basic voltage of each area:

where α and β are the end points of each interval of the segmented voltage.

According to Eq. (16) and the expressions of the basic voltage waveforms uL11 ~ uL34, the two-dimensional coordinate curve of PLxy with respect to the variation of power factor angle δ can be drawn, as shown in Fig. 4. By inspecting the relationship between the output power average values PLxy and δ in the positive half cycle and negative half cycle, it can be seen that the average power of each basic voltage area has the following relationship:

In particular, when the power factor angle δ is 0, the power of each area has the following relationship:

From Fig. 2, it can be drawn that the low-voltage unit outputs the total average power PLx (x = 1, 2, 3) in one cycle, which can be expressed by Eq. (19). Figure 5 shows the variation of the output power PLxy of the low-voltage unit with the power factor δ. It can be seen that the output powers of each low-voltage unit are unbalanced.

3.2 Implementation of power equalization based on hybrid modulation

From the above analysis, it can be known that the root cause for the output powers to be unbalanced in the low-voltage unit is that the output voltage of each unit does not contain all the basic voltage waveforms. In order to make the output powers of each low-voltage unit to be balanced, the output of the low-voltage unit should be made to include all the basic voltage waveforms within a certain period of time. According to Eq. (17), the output voltage includes 6 segments at least in a certain period of time, u11 or u13, u21 or u23, u31 or u33, u12 or u14, u22 or u24, u32 or u34, and it takes 3/2 cycles to cover the 6 kinds of basic voltage waveforms.

Next, the basic voltage waveforms covered by each unit in 3/2 cycles are replaced in the way as shown in Fig. 6.

A replacement of the basic voltage waveforms of the connected units is performed to make each unit cover 6 basic voltage waveforms in a 3/2 cycle. In this way, the output power of each unit can be balanced.

And then, an improvement of the modulation mode of the inverter is made by changing the carrier according to Fig. 6. The modulation principle can be stated as shown in Figs. 7 and 8.

As shown in Figs. 7 and 8, after adjusting the carrier, each low-voltage unit contains 6 basic voltage waveforms after 3/2 cycles, thus implementing the balance of the power in the low-voltage unit.

4 Comparative analysis of simulation and experimental results

In order to verify the effectiveness of the modulation strategy proposed in this paper, a simulation model of the hybrid cascaded H-bridge 13-level inverter is established in MATLAB 2019b/Simulink, and its experimental platform (Fig. 15) is constructed. The parameters utilized by simulation and experiment are: the DC side voltage in high-voltage unit VH = 36 V, the DC side voltage in low-voltage unit, VL = 12 V, carrier frequency fc = 5 kHz, modulation ratio m = 0.7 and 0.9, load resistance R = 10Ω, filter inductance L = 4mH. The results obtained by simulation are shown in Figs. 9, 10 and 11, and the results obtained by experiment are shown in Figs. 12, 13 and 14.

4.1 Comparison of simulation results

Figures 9,10 and 11 show a 13-level simulation voltage waveforms output by the inverter for m = 0.9 and m = 0.7 and the frequency spectrum distribution for m = 0.9 before and after the power balance is not reached. From Fig. 9, it can be seen that the fundamental voltage is 64.75 V and THD = 9.93%, and in the low-voltage unit, the average powers of the inverter present a stepwise increasing distribution, which are, respectively, 7.74 W, 32.7 W and 44.9 W. When m = 0.7, the inverter outputs an 11-level voltage waveform, and the output powers of the low-voltage unit are, respectively, 3.73 W, 10.3 W and 31.4 W. Obviously, there all exists the problem of the unbalanced output power in the low-voltage cascaded unit for the two modulation ratios.

After the carrier in the low-voltage unit is changed according to the method proposed in the paper, the situation is completely different. Through the theoretical calculation, the output powers of the low-voltage unit can be, respectively, obtained as 28.32 W, 28.32 W and 28.35 W when the modulation ratio m = 0.9. Figure 10 shows the output voltage and power simulation waveforms of the inverter after the powers balance, and Fig. 11 shows the output voltage frequency spectrum distribution before and after the power balance. From the figures, it can be seen that none of the output voltage waveforms, THD and fundamental voltage value are changed, which shows that the quality of the output voltage waveform of the inverter is not affected after the carrier is changed. At the same time, the output power of each unit is balanced, which proves that the power balance can be indeed achieved by replacing the basic voltage waveforms of the cascaded units.

4.2 Experimental verification

Figures 12,13 and 14, respectively, show a 13-level experimental voltage waveforms output by the inverter for m = 0.9 and m = 0.7 and the frequency spectrum distribution for m = 0.9 before and after the power balance is not reached.

Before the power balance is not reached, when the modulation ratio m = 0.9 and m = 0.7, the output voltage uLx of the connected unit, the output current i0, the output power PLx of the low-voltage unit and the total output voltage waveform u0 of the inverter are shown in Fig. 12. (Since the oscilloscope has only four output channels, the output voltage of the high-voltage unit is measured separately.) It can be seen from the figure that the measured results of the output voltage and output power of each unit are consistent with the simulation results, the output voltage is stable, and there is no current backflow. However, the output power of the low-voltage unit is unbalanced, which proves that the hybrid modulation strategy is correct and effective for the hybrid cascaded H-bridge 13-level inverter and that the power unbalance exists between the low-voltage units.

From Fig. 13, it can be seen that after the power is balanced, the output voltage waveform of each low-voltage unit is no longer symmetrical within a single cycle, and on replacing the output voltage of each low-voltage unit according to a certain rule, the output power will be also no longer symmetrical, but the output powers between the low-voltage units are balanced within 3/2 cycles. Furthermore, it can be seen from Fig. 14 that when m = 0.9, the measured frequency spectrum of the output voltage is consistent with the simulation result before and after the inverter power balance is reached. These results fully prove the correctness and effectiveness of the power balance modulation strategy proposed in this paper (Fig. 15).

5 Conclusion

In this paper, the modulation strategy of the hybrid cascaded H-bridge thirteen-level inverter is studied, and a power balance modulation strategy is proposed. Firstly, the output power relationship expressions of each low-voltage unit are theoretically derived. Then, according to the theoretical analysis results, the carrier of the hybrid modulation strategy is regularly rotated. Finally, on the premise of ensuring the quality of the output voltage waveform of the inverter, the balance of the output power of each low-voltage cascaded unit is realized. Both simulation and experimental results show that under the control of the power balance modulation strategy, the output voltage waveform quality of the system is good, there is no current backflow, and the powers between the low-voltage units are balanced, which fully verifies the reasonability and effectiveness of the power balance strategy.

References

Adam GGP, Abdelsalam I, Ahmed K et al (2014) Hybrid multilevel converter with cascaded H-bridge cells for HVDC applications: Operating principle and scalability. IEEE Trans Power Electron 30(1):65–77

Li Y, Wang Y, Li BQ (2015) Generalized theory of phase-shifted carrier PWM for cascaded H-bridge converters and modular multilevel converters. IEEE Journal of Emerging and Selected Topics in Power Electronics 4:589–605

Townsend CD, Summers TJ, Betz RE (2015) Phase-shifted carrier modulation techniques for cascaded H-bridge multilevel converters. IEEE Trans Industr Electron 62(11):6684–6696

Ren L, Gong C, He K et al (2016) A modified hybrid modulation scheme with even switch thermal distribution for H-bridge hybrid cascaded inverters. IET Power Electronics 10(2):261–268

Wu X, Xiong C, Yang S et al (2020) A simplified space vector pulsewidth modulation scheme for three-phase cascaded H-bridge inverters. IEEE Trans Power Electron 35(4):4192–4204

Kumar A (2019). A modified seven level cascaded H bridge inverter. In: 2018 5th IEEE Uttar Pradesh Section International Conference on Electrical, Electronics and Computer Engineering (UPCON). IEEE.

Kaiyi He, Lei R, Xiang D et al (2016) Modified modulation of H-bridge cascaded inverters. Transactions of China Electrotechnical Society 31(014):193–209

Qingli H, Wuming G (2007) Simulation study of a new type of seven-level hybrid cascade inverter. Inverter Technology and Electric Transaction 04:40–43

Atkar D, Udakhe PS, Chiriki S, et al. Control of seven level cascaded H-Bridge inverter by hybrid SPWM technique. In: 2016 IEEE international conference on power electronics, drives and energy systems (PEDES). IEEE

Du Z, Tolbert LM, Ozpineci B et al (2009) Fundamental frequency switching strategies of a seven-level hybrid cascaded H-bridge multilevel inverter. IEEE Trans Power Electron 24(1):25–33

Yi W, Xinchun S, Ling Z et al (2004) Research on the hybrid frequency carrier-based multilevel PWM control strategy. Proceedings of the CSEE 11:190–194

Hu W, Liu J (2019) A new scheme of hybrid cascaded inverter. Proc CSEE 39(20):6044–6055

Zhao T, Wang G, Bhattacharya S et al (2013) Voltage and power balance control for a cascaded H-bridge converter-based solid-state transformer. IEEE Trans Power Electron 28(4):1523–1532

Manyuan Ye, Yunhunag X, Xiang K et al (2017) Power balance control scheme of cascaded multilevel inverter with five switches for each H-bridge units. Electric Machines and Control 29(02):27–31

Sun Y, Ruan X (2006) Power balance control schemes for cascaded multilevel inverters. Proceedings of the CSEE 4:126–133

Chen Z, Xu Y, Yuan T et al (2017) Power balance control method with phase disposition for cascaded H-bridge inverter based on control degrees of freedom combination. Proceedings of the CSEE 37(23):6951–6961

Chen ZX, Yaming YT et al (2018) Power balance control methods and comparative study using carrier rotation technique for the cascaded inverter. Transactions of China Electrotechnical Society 33(20):4802–4812

Yu Y, Konstantinou G, Hredzak B et al (2015) Power balance optimization of cascaded H-bridge multilevel converters for large-scale photovoltaic integration. IEEE Trans Power Electron 31(2):1108–1120

Chen Z, Xu Y, Na X et al (2018) Power balance control and optimization methods with output voltage rotation for cascaded multilevel inverter. Proceedings of the CSEE 38(04):1132–1142

Yaming X, Zhong C, Xianlong N et al (2018) Power balance modulation strategy based on carrier reconstruction for cascaded inverter. Trans China Electrotech Soc 33(12):2831–2840

Sanmin W (2003) A new power balancing method for cascaded H-bridge multilevel inverter. Trans China Electrotech Soc

Ye M, Song G, Kang X et al (2020) Type II asymmetric CHB multilevel inverter SHEPPWM power balance control strategy. Electric Machines and Control 1–11[2020–11–21]

Manyuan Y, Yunhuang X, Xiang K et al (2018) Power balance control scheme of cascaded multilevel inverters with hybrid H-bridge units. Electric Machines and Control 22(12):54–61

Acknowledgements

This work was supported by the National Natural Science Foundation of China under Grant 61561007 and in part by the Natural Science Foundation of Guangxi Province, China, under Grant 2017GXNSFAA198168.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons licence, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons licence, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons licence and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this licence, visit http://creativecommons.org/licenses/by/4.0/.

About this article

Cite this article

Gong, R., Xue, B., Liu, J. et al. Power balance modulation strategy for hybrid cascaded H-bridge multi-level inverter. Electr Eng 104, 753–762 (2022). https://doi.org/10.1007/s00202-021-01337-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00202-021-01337-y