Abstract

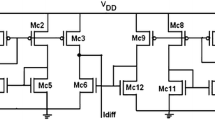

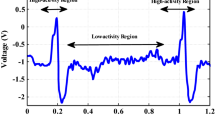

This paper proposes an energy-efficient fully differential difference integrating analog-to-digital converter (ADC) for image sensors and biomedical recording systems where the variation of the input analog signal is usually much smaller than the full-scale range of the signal. In order to find the digital code of the input analog sample, the proposed structure digitizes the voltage difference between the new analog sample and the previous one, leading to power saving. The proposed ADC not only improves the rounding problem existing in the previous structures, but also its sampling rate is doubled by employing two auxiliary comparators. Moreover, using a segmented architecture for the employed capacitive-array digital-to-analog converter reduces the capacitor switching activity and therefore the power consumption of the ADC. The proposed ADC is designed and simulated in TSMC 0.18-µm CMOS process. Post-layout simulation results of a 1-V, 8-bit, 40-kS/s ADC show that for low-varying input signals, the proposed circuit achieves a signal-to-noise-plus-distortion of 49.3 dB while consuming 220 nW power dissipation, leading to a figure of merit of 23 fJ/c-step. The silicon area occupied by the circuit is 300 µm × 215 µm.

Similar content being viewed by others

References

D.G. Chen, F. Tang, M.-K. Law, X. Zhong, A. Bermak, A 64 fJ/step 9-bit SAR ADC array with forward error correction and mixed-signal CDS for CMOS image sensors. IEEE Trans. Circuits Syst. I Regul. Pap. 61(11), 3085–3093 (2014)

S.-L. Chen, J.F. Villaverde, H.-Y. Lee, D.W.-Y. Chung, T.-L. Lin, C.-H. Tseng, K.-A. Lo, A power-efficient mixed-signal smart ADC design with adaptive resolution and variable sampling rate for low-power applications. IEEE Sens. J. 17(11), 3461–3469 (2017)

H.-J. Kim, S.-I. Hwang, J.-H. Chung, J.-H. Park, S.-T. Ryu, A dual-imaging speed-enhanced CMOS image sensor for real-time edge image extraction. IEEE J. Solid-State Circuits 52(9), 2488–2497 (2017)

Y. Kim, C. Yoo, A 100-kS/s 8.3-ENOB 1.7-µW time-domain analog-to-digital converter. IEEE Trans. Circuits Syst. II: Express Briefs 61(6), 408–412 (2014)

J.-Y. Lin, C.-C. Hsieh, A 0.3 V 10-bit SAR ADC with first 2-bit guess in 90-nm CMOS. IEEE Trans. Circuits Syst. I: Regul. Pap. 64(3), 562–572 (2017)

C.-C. Liu, S.-J. Chang, G.-Y. Huang, Y.-Z. Lin, A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 45(4), 731–740 (2010)

E. Rahiminejad, R. Lotfi, A low-power architecture for integrating analog-to-digital converters, in 2009 16th IEEE International Conference on Electronics, Circuits and Systems (2009), pp. 411–414

E. Rahiminejad, M. Saberi, R. Lotfi, A power-efficient signal-specific ADC for sensor-interface applications. IEEE Trans. Circuits Syst. II Express Briefs 64(9), 1032–1036 (2017)

M. Saberi, R. Lotfi, Segmented architecture for successive approximation analog-to-digital converters. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 22(3), 593–606 (2014)

M. Saberi, H. Sepehrian, R. Lotfi, K. Mafinezhad, A low-power successive approximation ADC for biomedical applications. IEICE Electron. Express 8(4), 195–201 (2011)

M. Sadollahi, K. Hamashita, K. Sobue, G.C. Temes, An 11-bit 250-nW 10-kS/s SAR ADC with doubled input range for biomedical applications. IEEE Trans. Circuits Syst. I Regul. Pap. 65(1), 61–73 (2018)

H. Sepehrian, M. Saberi, R. Lotfi, A signal-specific successive-approximation analog-to-digital converter, in 2011 IEEE International Symposium of Circuits and Systems (2011), pp. 1624–1627

F. Shakibaee, F. Sajedi, M. Saberi, Low-power successive approximation ADC using split-monotonic capacitive DAC. IET Circuits Devices Syst. 12(2), 203–208 (2018)

M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E.A.M. Klumperink, B. Nauta, A 10-bit charge-redistribution ADC consuming 1.9 µW at 1 MS/s. IEEE J. Solid-State Circuits 45(5), 1007–1015 (2010)

J. Wang, S. Liu, Y. Shen, Z. Zhu, Low-power single-ended SAR ADC using symmetrical DAC switching for image sensors with passive CDS and PGA technique. IEEE Trans. Circuits Syst. I Regul. Pap. 65(8), 2378–2388 (2018)

Q. Wang, S. Chen, A low power prediction SAR ADC integrated with DPCM data compression feature for WCE application, in 2016 IEEE Biomedical Circuits and Systems Conference (2016), pp. 107–110

R. Xu, B. Liu, J. Yuan, A 1500 fps highly sensitive 256 × 256 CMOS imaging sensor with in-pixel calibration. IEEE J. Solid-State Circuits 47(6), 1408–1418 (2012)

F.M. Yaul, A.P. Chandrakasan, A 10 bit SAR ADC with data-dependent energy reduction using LSB-first successive approximation. IEEE J. Solid-State Circuits 49(12), 2825–2834 (2014)

S. Yim, Y. Park, H. Yang, S. Kim, Power efficient SAR ADC adaptive to input activity for ECG monitoring applications, in 2017 IEEE International Symposium on Circuits and Systems (2017), pp. 7–10

H. Yu, W. Tang, M. Guo, S. Chen, A two-step prediction ADC architecture for integrated low power image sensors. IEEE Trans. Circuits Syst. I Regul. Pap. 64(1), 50–60 (2017)

H. Zhuang, W. Guo, J. Liu, H. Tang, Z. Zhu, L. Chen, N. Sun, A second-order noise-shaping SAR ADC with passive integrator and tri-level voting. IEEE J. Solid-State Circuits 54(6), 1636–1647 (2019)

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Ghanavati, A., Saberi, M. A Fully Differential and Power-Efficient Difference Integrating ADC. Circuits Syst Signal Process 39, 3804–3818 (2020). https://doi.org/10.1007/s00034-020-01360-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01360-7