Abstract

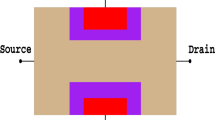

This work investigated the electrical performances of a single gate (SG) and double gate (DG) metal oxide semiconductor field-effect transistors (MOSFETs) by varying the gate length. The electrical characteristics are analyzed and parameters like ON-state current, OFF-state current, and transconductance are considered. A similar study was conducted by changing the oxide material to high-k material (HfO2). It is perceived that for gate length below 25 nm, overall channel potential starts decreasing due to increased source-drain resistance and velocity saturation owing to short channel effects. The drain current decreases as the gate length are decreased for both the SG and DG MOSFET. The transconductance also decreases inversely with the gate length for SG with the graded channel, SG with graded channel using a high-k dielectric, DG with the graded channel, and DG with graded channel using high-k dielectric.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Moore G (1965) Cramming more components onto integrated circuits. Electron 38:114–117

Rana V, Ahmed G, Ramesh A, Das S, Singh P (2020) Diameter depended piezoresistive sensing performance of junctionless Gate-All-Around Nanowire FET. IEEE Trans Electron Dev 67(7):2884–2889

Li W, Woo J (2020) Vertical P-TFET with a P-Type SiGe Pocket. IEEE Trans Electron Devices 67(4):1480–1484

Maity NP, Maity R, Baishya S (2019) An analytical model for the surface potential and threshold voltage of a double-gate heterojunction tunnel FinFET. J Comput Electron 18:65–75

Ma J, Matioli E (2017) Slanted tri-gates for high-voltage GaN power devices. IEEE Electron Device Lett 38(9):1305–1308

Chakraborty H, Maity R, Maity NP (2019) Analysis of surface potential for dual-material-double-gate MOSFET based on modeling and simulation. Microsyst Technol 25:4675–4684

Maity NP, Maity R, Baishya S (2019) A tunneling current model with practical barrier for ultra thin high-k dielectric ZrO2 material based MOS devices. Silicon 10:1645–1652

Maity NP, Maity R, Baishya S (2017) Influence of image force effect on tunneling current density for high-k material ZrO2 ultra thin films based MOS devices. J Nanoelectron Optoelectron 12:67–71

Maity NP, Maity R, Thapa RK, Baishya S (2014) Study of interface charge Ddensities for ZrO2 and HfO2 based Metal-Oxide Semiconductor devices. Adv Mat Sci Eng Article ID 497274, 1–6

Chaudhry A, Kumar MJ (2004) Controlling short-channel effects in deep submicron SOI MOSFETs for improved reliability: A review. IEEE Trans Dev Mater Rel 4:99–109

Maity NP, Maity R, Baishya S (2017) Voltage and Oxide Thickness Dependent Tunneling Current Density and Tunnel Resistivity Model: Application to High-k Material HfO2 Based MOS Devices. Superlattices Microstruct 111:628–641

Jelodar MS, Ilatikhameneh H, Kim S, Ng K, Klimeck G (2016) Optimum high-k oxide for the best performance of ultrascaled double-gate MOSFETs. IEEE Trans Nanotechnol 15:904–910

Choi J, Mao Y, Chang J (2011) Development of hafnium based high-k materials-a review. Mater Sci Eng R72:97–136

Chakraborty H, Maity R, Baishya S, Maity NP (2020) An accurate model for threshold voltage analysis of dual material double gate metal oxide semiconductor field effect transistor. Silicon, Online published in 9 July 2020https://doi.org/10.1007/s12633-020-00553-8

Basak R, Maiti B, Mallik A (2015) Analytical model of gate leakage current through bilayer oxide stack in advanced MOSFET. Supperlattices and Microstructures 80:20–31

Jelodar M, Ilatikhameneh H, Kim S, Ng K, Klimeck G (2016) Optimum high-k oxide for the best performance of ultrascaled double-gate MOSFETs. IEEE Trans Nanotechnol 15:904–910

Maity N, Maity R, Maity S, Baishya S (2019) Comparative analysis of the quantum FinFET and trigate FinFET based on modeling and simulation. J Comput Electron 18:492–499

Narang R, Saxena M, Gupta RS, Gupta M (2013) Impact of temperature variations on the device and circuit performance of tunnel FET: a simulation study. IEEE Trans. Nanotechnol. 12:951–957

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Lalthlamuana, J., Maity, N.P., Singh, L.L.K., Maity, R. (2021). Electrical Performance of Single Gate and Double Gate MOSFET to Optimize the Gate Length. In: Bindhu, V., Tavares, J.M.R.S., Boulogeorgos, AA.A., Vuppalapati, C. (eds) International Conference on Communication, Computing and Electronics Systems. Lecture Notes in Electrical Engineering, vol 733. Springer, Singapore. https://doi.org/10.1007/978-981-33-4909-4_52

Download citation

DOI: https://doi.org/10.1007/978-981-33-4909-4_52

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-33-4908-7

Online ISBN: 978-981-33-4909-4

eBook Packages: EngineeringEngineering (R0)