Abstract

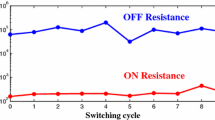

Memories, which act as data storage devices, are crucial to computer systems. These are extensively used in application-specific integrated circuits and in other microprocessor-based systems where millions of transistors are integrated on a single chip. Since the memories generally account for a large portion of the chip area, these components suffer more space radiation than others. The sensitivity to radiation of semiconductor memories has become a critical issue to ensure the reliability of electronic systems. Recently, memristor emerges as a newly fabricated device that is becoming popular among researchers for its immune to radiation, non-volatility, and good switching behavior. However, research on soft error tolerance in memristor-based memories is still negligible. This paper presents a new method to tolerate soft errors in memristor-based memory. The proposed method can correct single, and double-bit soft errors with lesser information overhead concerning existing techniques.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Siddiqui MSM, Ruchi S, Van Le L, Yoo T, Chang I, Kim TT (2020) SRAM radiation hardening through self-refresh operation and error correction. IEEE Transa Device Mater Reliab 20(2):468–474

Patnaik A et al (2018) An on-chip detector of transient stress events. IEEE Trans Electromagn Compat 60(4):1053–1060

Zhirnov VV, Cavin RK, Hutchby JA, Bourianoff GI (2003) Limits to binary logic switch scaling—a gedanken model. Proc IEEE 91(11):1934–1939

Yang S, Adeyemo A, Bala A, Jabir A (2017) Novel techniques for memristive multifunction logic design. Integration, 65:219–230

Hamdioui S, Taouil M, Haron NZ (2015) Testing open defects in memristor-based memories. IEEE Trans Comput 64(1):247–259

Pouyan P, Amat E, Rubio A (2018) Memristive crossbar memory lifetime evaluation and reconfiguration strategies. IEEE Trans Emerg Top Comput 6(2):207–218

Benoist A et al (2014) 28nm advanced CMOS resistive RAM solution as embedded non-volatile memory. In: IEEE international reliability physics symposium, pp 2E.6.1–2E.6.5

Zandevakili H, Mahani A (2019) Memristor-Based hybrid fault tolerant structure with concurrent reconfigurability. IEEE Embedded Syst Lett 11(3):73–76

Leroux et al (2014) Design of an MGy radiation-tolerant resolver-to-digital converter IC for remotely operated maintenance in harsh environments. Fusion Eng Des 89(9–10):2314–2319

Manem H, Rose GS, He X, Wang W (2010) Design considerations for variation tolerant multilevel CMOS/Nano memristor memory. In: Proceedings of 20th great lakes symposium VLSI (GLSVLSI), pp 287–292

Liu C et al (2017) Rescuing memristor-based neuromorphic design with high defects. In: 4th ACM/EDAC/IEEE design automation conference (DAC), pp 1–6

Zhang S et al (2020) Lifetime enhancement for RRAM-based computing in-memory engine considering aging and thermal effects. In: 2nd IEEE international conference on artificial intelligence circuits and systems (AICAS), pp 11–15

Chen CY, ChakrabartyK (2021) Pruning of deep neural networks for fault-tolerant memristor-based accelerators. In: 58th ACM/IEEE design automation conference (DAC), pp 889–894

Eshraghian JK et al (2019) Analog weights in ReRAM DNN accelerators. In: Proceedings of IEEE international conference on artificial intelligence circuits systems (AICAS), pp 267–271

Rahimi M et al (2020) Complementary metal-oxide semiconductor and memristive hardware for neuromorphic computing. Adv Intell Syst 2(5)

Cassuto Y, Kvatinsky S, Yaakobi E (2013) Sneak-path constraints in memristor crossbar arrays. In: IEEE international symposium on information theory, pp 156–160

Sotiriadis PP (2006) Information capacity of nanowire crossbar switching networks. IEEE Trans Inf Theory 52 (7):3019–3032

Cassuto Y, Kvatinsky S, Yaakobi E (2014) On the channel induced by sneak-path errors in memristor arrays. In: International conference on signal processing and communications (SPCOM), pp 1–6

Fieback M et al (2019) Device-aware test: a new test approach towards DPPB level. In IEEE international test conference (ITC), pp 1–10

Hamming RW (1950) Error detecting and error correcting codes. Bell Syst Tech J 26(2):147–160

Argyrides C, Pradhan DK, Kocak T (2011) Matrix codes for reliable and cost-efficient memory chips. IEEE Trans Very Large Scale Integr (VLSI) Syst 19(3)

Acknowledgements

We, the authors, are grateful to the Institute of Information and Communication (IICT), Bangladesh University of Engineering and Technology (BUET) for providing all possible support to perform this research.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2023 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Sadi, M.S., Sumon, M.M.H., Ali, M.L. (2023). Soft Error Tolerant Memristor-Based Memory. In: Ahmad, M., Uddin, M.S., Jang, Y.M. (eds) Proceedings of International Conference on Information and Communication Technology for Development. Studies in Autonomic, Data-driven and Industrial Computing. Springer, Singapore. https://doi.org/10.1007/978-981-19-7528-8_33

Download citation

DOI: https://doi.org/10.1007/978-981-19-7528-8_33

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-19-7527-1

Online ISBN: 978-981-19-7528-8

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)