Abstract

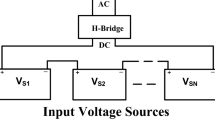

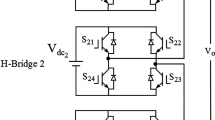

The utilization of multilevel inverter since the last decade has been increased. Due to the ability of these novel inverters to synthesize, the waveforms with better harmonic profile and output are used in number of high voltage and high power applications This paper depicts an asymmetrical 23-level multilevel inverter, using sinusoidal pulse width modulation technique. With increased steps in output voltage, the total harmonic distortion (THD) is reduced. This topology is anticipated to get 23 levels. Simulation results are shown and compared with theoretical results. This topology is proposed to give more number of levels with minimum possible switches, which is more efficient.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Kamaraja AS, Priyadharshini K (2019) Solar-powered multilevel inverter with a reduced number of switches. Int J Sci Technol Res 8(10):1545–1550

Omer P, Kumar J, Surjan BS (2020) A review on reduced switch count multilevel inverter topologies. IEEE Access 8:22281–22302

Gupta KK, Ranjan A, Bhatnagar P, Sahu LK, Jain S (2016) Multilevel inverter topologies with reduced device count: a review. IEEE Trans Power Electron 31(1):135–151

Siddique MD, Mekhilef S, Shah NM, Ali JSM, Meraj M, Iqbal A, Al-Hitmi MA (2019) A new single phase single switched-capacitor based nine-level boost inverter topology with reduced switch count and voltage stress. IEEE Access 7:174178–174188

Siddique MD, Mekhilef S, Shah NM, Memon MA (2019) Optimal design of a new cascaded multilevel inverter topology with reduced switch count. IEEE Access 7:24498–24510

Siddique MD, Mekhilef S, Shah NM, Sarwar A, Iqbal A, Tayyab M, Ansari MK (2019) Low switching frequency based asymmetrical multilevel inverter topology with reduced switch count. IEEE Access 7:86374–86383

Sadigh AK, Abarzadeh M, Corzine KA, Dargahi V (Dec 2015) A new breed of optimized symmetrical and asymmetrical cascaded multilevel power converters. IEEE J Emerg Sel Topics Power Electron 3(4):1160–1170

Jain S, Sonti V (2017) A highly efficient and reliable inverter configuration based cascaded multilevel inverter for PV systems. IEEE Trans Ind Electron 64(4):2865–2875

Jayabalan M, Jeevarathinam B, Sandirasegarane T (2017) Reduced switch count pulse width modulated multilevel inverter. IET Power Electron 10(1):10–17

Babaei E, Laali S, Bayat Z (2015) A single-phase cascaded multi-level inverter based on a new basic unit with reduced number of power switches. IEEE Trans Ind Electron 62(2):922–929

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2023 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Revathi, M., Rama Sudha, K. (2023). A New Cascaded H-bridge Multilevel Inverter Using Sinusoidal Pulse Width Modulation. In: Gupta, D., Khanna, A., Bhattacharyya, S., Hassanien, A.E., Anand, S., Jaiswal, A. (eds) International Conference on Innovative Computing and Communications. Lecture Notes in Networks and Systems, vol 473. Springer, Singapore. https://doi.org/10.1007/978-981-19-2821-5_22

Download citation

DOI: https://doi.org/10.1007/978-981-19-2821-5_22

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-19-2820-8

Online ISBN: 978-981-19-2821-5

eBook Packages: EngineeringEngineering (R0)