Abstract

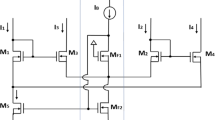

In this paper, a low-voltage one-quadrant squarer–divider (SD) circuit based on level shifted flipped voltage follower (LSFVF) has been proposed. The proposed squarer–divider circuit utilizes low-voltage SD based on MOS translinear (MTL) principle. In the proposed design, flipped voltage follower (FVF) configuration used for biasing of MTL transistors has been replaced by LSFVF configuration. This proposed LSFVF-based squarer–divider circuit not only maintains the low supply voltage requirement of the FVF-based squarer–divider but it reduces the error present in output current significantly. To validate the working of proposed SD circuit, it has been simulated in LTspice using 0.18 µm CMOS technology. These simulations show that result shows, that a significant improvement is achieved at low values of input current in the proposed LSFVF SD circuit as compared to FVF-based SD circuit.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Agrawal Y, Dhiman R, Chandel R (2012) Superiority of current mode over voltage mode interconnects. IJSET 1(2):59–64

Ramírez-Angulo J, Gupta S, Padilla I, Carvajal RG, Torralba A, Jimenez M, Munoz F (2005) Comparison of conventional and new flipped voltage structures with increased input/output signal swing and current sourcing/sinking capabilities. In: IEEE 48th Midwest symposium on circuits and systems, pp 1151–1154

Ramirez-Angulo J, Carvajal RG, Torralba A, Galan JAGJ, Vega-Leal AP, Tombs JATJ (2002) The flipped voltage follower: a useful cell for low-voltage low-power circuit design. In: IEEE International symposium on circuits and systems. Proceedings (Cat. No. 02CH37353), vol 3, pp III–III

Aggarwal B, Gupta M, Gupta AK (2013) A low voltage wide swing level shifted FVF based current mirror. In: IEEE International conference on advances in computing, communications and informatics (ICACCI), pp 880–885

Tangsrirat W, Pukkalanun T, Mongkolwai P, Surakampontorn W (2011) Simple current-mode analog multiplier, divider, square-rooter and squarer based on CDTAs. AEU-Int J Electron Commun 65(3):198–203

Seevinck E, Wiegerink RJ (1991a) Generalized translinear circuit principle. IEEE J Solid-State Circ 26(8):1098–1102

López-Martín AJ, Carlosena A (2001) Current-mode multiplier/divider circuits based on the MOS translinear principle. Analog Integr Circ Sig Process 28(3):265–278

Huang CY, Liu BD (1997) Current-mode defuzzifier circuit to realise the centroid strategy. IEE Proc Circ Dev Syst 144(5):265–271

Seevinck E, Vittoz EA, Plessi MD, Joubert TH, Beetge W (2000) CMOS translinear circuits for minimum supply voltage. IEEE Trans Circ Syst II Analog Digit Sig Process 47(12):1560–1564

Wiegerink RJ (1992) Analysis and synthesis of MOS translinear circuits. PhD thesis

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Yadav, S., Aggarwal, B. (2021). Low-Voltage Squarer–Divider Circuit Using Level Shifted Flipped Voltage Follower. In: Singari, R.M., Mathiyazhagan, K., Kumar, H. (eds) Advances in Manufacturing and Industrial Engineering. ICAPIE 2019. Lecture Notes in Mechanical Engineering. Springer, Singapore. https://doi.org/10.1007/978-981-15-8542-5_100

Download citation

DOI: https://doi.org/10.1007/978-981-15-8542-5_100

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-8541-8

Online ISBN: 978-981-15-8542-5

eBook Packages: EngineeringEngineering (R0)