Abstract

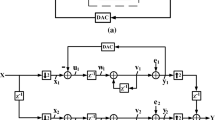

The delta-sigma modulator is used as an oversampling ADC, which processes the signal input and the quantization noise by two distinct transfer functions, thus, separating the signal and noise into two distinct frequency bands. The resulting output of the modulator is digitally processed to separate the signal from noise. The performance of the ADC can be improved by increasing the order of the modulator, which imposes constraints on the system stability and on the input signal range. This paper examines the issues related to the design of a stable fourth-order MultistAge noise SHaping architecture(MASH) ADC, using two second-order delta-sigma modulators in cascade. The architecture achieves second-order Signal Transfer Function (STF) with fourth-order noise shaping . The modulator employs 32 MHz—clock, to obtain 8-bit sample sequence at 128 kHz sample rate. The resulting output is processed by a digital low pass filter to separate the signal from noise. The FIR filter is implemented using frequency sampling technique.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Jacob Baker R, CMOS circuit design, layout and simulation. IEEE Press

Jacob Baker R, CMOS mixed signal circuit design. IEEE Press

Parihar RS, Gupta A, Design of a fully differential two-stage CMOS Op-Amp for high gain, high bandwidth applications. IEEE J Microchip Technol Inc 40(1):32–38

Sumanen L, Waltari M, Hakkarainen V, Halonen K, CMOS Dynamic Comparators for Pipeline ADC. Helsinki University of Technology, Electronic Circuit Design Laboratory P.O.Box 3000, FIN-02015 HUT, Finland

Pavan S, Schreier R, Themes G, Understanding delta-sigma converters, 2nd edn. IEEE Press, Wiley-Interscience.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2021 The Editor(s) (if applicable) and The Author(s), under exclusive license to Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Kotabagi, S.S., Subbanna Bhat, P. (2021). Design and Simulation of Fourth-Order Delta-Sigma Modulator-MASH Architecture. In: Nath, V., Mandal, J. (eds) Nanoelectronics, Circuits and Communication Systems. Lecture Notes in Electrical Engineering, vol 692. Springer, Singapore. https://doi.org/10.1007/978-981-15-7486-3_54

Download citation

DOI: https://doi.org/10.1007/978-981-15-7486-3_54

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-15-7485-6

Online ISBN: 978-981-15-7486-3

eBook Packages: EngineeringEngineering (R0)