Abstract

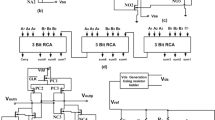

Foremost leading-edge integrated circuit applications like microprocessors, digital signal processors, RF processors, and mixed-signal processors need low power and less area of die utilization. This paper presents entirely a different method of designing and analyzing the primary modules of four-bit ripple carry adders, multiplexers of various sizes, full adders, and full subtractors based on decomposite Shannon’s expansions and MGDI techniques. The proposed systems are modules in nature indicating that it can easily be upgraded to various leading-edge ICs. The core benefit is less transistors and less power consumption. The implementation and analysis of these digital systems are done by using Microwind and Digital Schematic at 0.12 µm technology and analyzed area and total power consumption with different technologies and power supply voltages.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Saravanan, S., Madheswaran, M.: Design of low power, high performance area efficient Shannon based adder cell for neural network training. In: Control, Automation, Communication and Energy Conversation, INCACEC (2009)

Lee, J.D., Yoony, Y.J., Leez, K.H., Park, B.-G.: Application of dynamic pass-transistor logic to an 8-bit multiplier. J. Kor. Phys. Soc. 38(3), 220–223 (2001)

Purnima, K., AdiLakshmi, S., Sahithi, M., Rani, A.J., Poornima, J.; Design of modified Shannon based full adder cell using PTL logic for low power applications

Rawat, S., Sah, A., Pundir S.: Implementation of Boolean functions through multiplexers with the help of Shannon expansion theorem

Jiang, Y., Al-Sheraidah, A., Wang, Y., Sha, E., Chung, J.-G.: A novel multiplexer-based low-power full adder. IEEE Trans. Circuits Syst. II: Express Briefs 51(7), 345 (2004)

Singh, M., Pandit, M.K., Jana, A.K.: Economic full adder circuit in VLSI using Shannon expansion

Aliotoa, M., Di Cataldob, G., Palumbob, G.: Mixed full adder topologies for high-performance low-power arithmetic circuits. Microelectron. J. 38 (2007). Received in revised form 4 Sept 2006; Accepted 11 Sept 2007

Vishalatchi, S., Dhanam, B., Ramasamy, K.: Design, analysis and implementation of various full adder using GDI and MGDI technique

Bhattachatyya, P., Kundu, B., Ghosh, S., Kumar, V., Dandapat, A.: Performance analysis of a low-power high-speed hybrid 1-bit full adder circuit. IEEE Trans. VLSI Syst. 19(4) (2015)

Mohanty, B.K., Patel, S.K.: Area–delay–power efficient carry-select adder. IEEE Trans. Circuits Syst. II: Express Briefs 61(6) (2014)

Ruiz, G.A., Granda, M.: An area-efficient static CMOS carry-select adder based on a compact carry look-ahead unit. Microelectron. J. Received in revised form 23 Aug 2004; Accepted 2 Sept 2004

Ramkumar, B., Kittur, H.M.: Low-power and area-efficient carry select adder. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 20(2) (2012)

Chang, C.H., Gu, J.M., Zhang, M.: A review of 0.18 µm full adder performances for tree structured arithmetic circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 13(6) (2005)

Hassoune, I., Flandre, D., O’Connor, I.: ULPFA: a new efficient design of a power-aware full adder. IEEE Trans. Circuits Syst. I: Regul. Pap. 57(8) (2010)

Navia, K., Moaiyeri, M.H., Mirzaeem, R.F.: Two new low-power full adders based on majority-not gates. Microelectron. J. (2009)

Goel, S., Kumar, A., Bayoumi, M.A.: Design of robust, energy efficient full adders for deep submicrometer design using hybrid CMOS logic style. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 14(12) (2006)

Aguirre-Hernandez, M., Linares-Aranda, M.: CMOS full adders for energy-efficient arithmetic applications. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 19(4) (2011)

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2019 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Syed, S., Thriveni, R., Khan, P.V.A. (2019). A Novel Approach of Low Power, Less Area, and Economic Integrated Circuits. In: Wang, J., Reddy, G., Prasad, V., Reddy, V. (eds) Soft Computing and Signal Processing . Advances in Intelligent Systems and Computing, vol 898. Springer, Singapore. https://doi.org/10.1007/978-981-13-3393-4_49

Download citation

DOI: https://doi.org/10.1007/978-981-13-3393-4_49

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-13-3392-7

Online ISBN: 978-981-13-3393-4

eBook Packages: Intelligent Technologies and RoboticsIntelligent Technologies and Robotics (R0)