Abstract

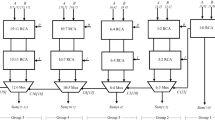

The binary adders are the most essential and fundamental circuit element to perform the arithmetic operations in digital computers. These binary adder circuits are widely used in integrated circuits (IC) such as processors, and their usage does not limit inside arithmetic logic unit (ALU) of a processor. In fact these binary adders are also playing key role in various applications like digital filters, digital transformation cores, signal processing elements, digital modulators and demodulators, digital image/video processing, and cryptographic applications. The small performance metric of the binary adder circuit will yield significant advantage in larger computations. Designing of faster, smaller, and more powerful efficient binary adder has been the ultimate challenge for many researchers. To succeed in this challenge, numerous architectures were proposed in past, which results in various architectures for the binary adder. In recent times, the carry select adder (CSLA) architecture was considered as one of the best suitable architectures which showed better performance among the others. Several new architectures were introduced in CSLA to improve its performance further. The area occupied by the CSLA adder is one of the performance metrics to evaluate the efficiency of the CSLA adder. This is because the CSLA adder uses two ripple carry adders for the both states of single carry input. Thus, the adders use two times more circuit elements than necessary. Several approaches like binary-to-excess-1 converter (BEC-1), common boolean logic (CBL), and SQRT architectures were proposed to reduce the area of the CSLA architecture. This article introduced a new approach in SQRT–CSLA adder using modified CBL. The common Boolean logic performs the evaluation of carry-based selection with less area than other design techniques. The design proposed in this article introduced a new CBL architecture which succeeded in reduction of area compared to the previous architectures. The CSLA adders with the proposed CBL architecture were implemented for the various word sizes like 8-bit, 16-bit, and 32-bit. The reduction of area has been clearly observed in the results. These results prove that the proposed CSLA scheme exhibits better performance than the regular SQRT–CSLA.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

Ramkumar, B., Harish, K.: ASIC Implementation of modified faster carry save adder. Eupro. J. Sci. & Res. 42 53–58 (2010).

Kanchana Bhaaskram, V.S.,: Modified Carry Select Adder using Binary Adder as a BEC-1. Eupro. J. Sci. & Res. 103 156–164 (2013).

I-chyn, W., Cheng-chen, Yi-Sheng, L., Chien Chang, P.: An Area-Efficient Carry Select Adder Design by Sharing Common Boolean Logic Term. In IEEE Int. symposium circuit systems, (2005).

Manju, S., Sornagopal, V.: An Efficient SQRT architecture of carry select adder design by Common Boolean Logic. In Int. Con. VLSI Emb. Sys. Nano Ele. & Telcom. Sys (ICEVENT) (2013).

Sakthi Kumaran., Samiappa., Salivahanan, S., Kanchana Bhaaskaran. V.S., Vinoth, C.: A Very Fast and Low Power Carry Select Adder Circuit 3rd Int. Con. on Ele. & Com. Tech - ICECT (2011).

Rabaey., Jan M.: Digt. Intg. Cirt - A Design Perspective, Upper Saddle River, NJ: Prentice - Hall, (2001).

Bedrij, O.J.: Carry-Select Adder. IRE Trans. on Elec. and Comm., 340–344, (1962).

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2018 Springer Nature Singapore Pte Ltd.

About this paper

Cite this paper

Jujjuru, J.L., Mallavarapu, R. (2018). Improved SQRT Architecture for Carry Select Adder Using Modified Common Boolean Logic. In: Satapathy, S., Bhateja, V., Chowdary, P., Chakravarthy, V., Anguera, J. (eds) Proceedings of 2nd International Conference on Micro-Electronics, Electromagnetics and Telecommunications. Lecture Notes in Electrical Engineering, vol 434. Springer, Singapore. https://doi.org/10.1007/978-981-10-4280-5_36

Download citation

DOI: https://doi.org/10.1007/978-981-10-4280-5_36

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-4279-9

Online ISBN: 978-981-10-4280-5

eBook Packages: EngineeringEngineering (R0)