Abstract

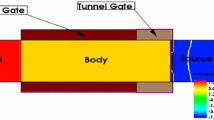

The performance of dual metal-double gate tunnel field effect transistor (DMG-DGTFET) with different dielectric gate materials is discussed. The dual metal gate technique (DMG) when applied to a DGTFET boosts the I ON current and simultaneously decreases the OFF state current, which results in a substantial increase in the I ON/I OFF ratio. In DMG-DGTFET, gate consists of two different metals with different work function which can be used to modulate the width of tunneling barrier at the source to body junction. It is shown in this paper that by appropriately engineering the work function of the metals at the gate the good performance can be achieved for low-power design applications. All the simulations were done in 2-D TCAD. Nonlocal tunneling model is been used to calculate band-to-band tunneling (BTBT) tunneling current across the junction.

Access this chapter

Tax calculation will be finalised at checkout

Purchases are for personal use only

Similar content being viewed by others

References

C. Hu, et al., “Prospect of tunneling green transistor for 0.1 V CMOS.” IEDM Tech. Dig., pp. 387–390, 2010.

Q. Zhang, W. Zhao, and A. Seabaugh, “Low-subthreshold-swing tunnel transistors,” IEEE Electron Device Lett., vol. 27, no. 4, pp. 297–300, Apr. 2006.

M. Luisier, G Klimeck, “Performances comparisons of tunneling field effect transistors made of InSb, Carbon and GaSb-InAs broken gap heterostructures,” IEDM Tech. Dig., pp. 913–916, 2009.

Semiconductor Industry Association (SIA), International Technology Roadmap for Semiconductors, 2009 Edition.

P.-F. Wang, K. Hilsenbeck, T. Nirschl, M. Oswald, C. Stepper, M. Weis, D. Schmitt-Landsiedel, and W. Hansch, “Complementary tunneling transistor for low power application,” Solid StateElectron., vol. 48, no. 12, pp. 2281–2286, Dec. 2004.

K. Boucart and A. M. Ionescu, “Double-gate tunnel FET with high-κ gate dielectric,” IEEE Trans. Electron Devices, vol. 54, no. 7, pp. 1725–1733, Jul. 2007.

W. Long, H. Ou, J. M. Kuo, and K. K. Chin, “Dual-material gate (DMG) FET,” IEEE Trans. Electron Devices, vol. 46, no. 5, pp. 865–870, May 1999.

A. Chaudhary and M. J. Kumar, “Investigation of the novel attributes of a fully depleted dual-material gate SOI MOSFET,” IEEE Trans. Electron Devices, vol. 51, no. 9, pp. 1463–1467, Sep. 2004.

Synopsys, TCAD Sentaurus device, ver. D2010-03, 2010.

W. Long, H. Ou, J. M. Kuo, and K. K. Chin, “Dual-material gate (DMG) TFET,” IEEE Trans. Electron Devices, vol. 46, no. 5, pp. 865–870, May 1999.

K. Y. Na and Y. S. Kim, “Silicon CMOS with dual work function gate,” Jpn. J. Appl. Phys., vol. 45, no. 12, pp. 9033–9036, Dec. 2006.

P. Ranade, Y. C. Yeo, Q. Lu, H. Takeuchi, T. J. King, and C. Hu, “Molybdenum as a gate electrode for deep sub-micron CMOS technology,” in Proc. MRS Symp., 2000, vol. 611, pp. C3.2.1–C3.2.6.

M. Hasan, H. Park, H. Yang, H. Hwang, H. S. Jung, and J. H. Lee, “Ultralow work function of scandium metal gate with tantalum nitride interface layer for n-channel metal oxide semiconductor application,” Appl. Phys. Lett., vol. 90, no. 10, pp. 103 510-1–103 510-3, Mar. 2007.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 Springer Science+Business Media Singapore

About this paper

Cite this paper

Deepak Kumar, Prateek Jain (2017). Performance of Dual Metal-Double Gate Tunnel Field Effect Transistor with Different Dielectrics. In: Singh, R., Choudhury, S. (eds) Proceeding of International Conference on Intelligent Communication, Control and Devices . Advances in Intelligent Systems and Computing, vol 479. Springer, Singapore. https://doi.org/10.1007/978-981-10-1708-7_108

Download citation

DOI: https://doi.org/10.1007/978-981-10-1708-7_108

Published:

Publisher Name: Springer, Singapore

Print ISBN: 978-981-10-1707-0

Online ISBN: 978-981-10-1708-7

eBook Packages: EngineeringEngineering (R0)