Abstract

This paper presents a comparative analysis of the bidirectional qZS-based dc-dc converter for storage application with a traditional solution based on the boost dc-dc converter. The analysis estimates the energy stored in the capacitors and inductors, blocking voltage across semiconductors, and conduction losses. The comparison is based on the mathematical and simulation analysis.

You have full access to this open access chapter, Download conference paper PDF

Similar content being viewed by others

Keywords

1 Introduction

Renewable energy sources are increasingly important today. European Commission has set a target to raise the share of renewable energy to 20% before 2020 [1,2,3,4,5,6,7]. The topic of power electronics converters for renewable applications is extremely popular. Growing number of renewable energy installations leads to an increase in the storage systems installations. The technologies devised require bidirectional power interface with minimum losses between two dc busses or a dc bus and an energy storage device (battery, supercapacitor, etc.). For these purposes, Bidirectional DC-DC Converters (BDCs) should be used. In applications with lower step-up or step-down ratio, a common solution is a non-isolated type [8,9,10,11,12,13,14]. Many research papers focus on optimal solutions of the bidirectional energy transfer for applications where galvanic isolation is not required.

Recent solutions based on the Impedance-Source (IS) networks have been extended to various fields of application. IS-based converters have much higher boost capability than traditional boost converters. Also, they have no forbidden switching states. As a result, the proven advantages of IS-based converters consist in wide-range input voltage regulation along with enhanced reliability [15,16,17,18,19,19,16,17,18,]. At the same time, it has been clearly demonstrated that the proposed solutions have drawbacks in dc-ac applications in terms of power density and efficiency [15].

Though many studies focus on the IS-based converter, no comparative analyses of the bidirectional dc-dc converter based on any IS network have been reported. Due to the enhanced boost functionality, it can be an attractive and competitive solution.

This paper provides a comparative analysis of the proposed bidirectional quasi-Z-Source converter based on the criteria of passive volume, voltage stress on semiconductors and conduction losses.

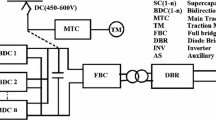

2 Relation to Smart Systems

The concept of the “smart grid” is very popular and well known and can be considered as a part of the future “smart system”. It includes an electrical grid that has a variety of operational and energy measures, including smart meters, smart appliances, renewable energy resources and storage systems. Electronic power conditioning and control of the production and distribution of electricity are important aspects of the smart grid. The issue of communication is a very important element of the smart system and smart grid in particular, many researchers focus on that topic. At the same time, new standards of communication technologies such as 5G or IPV6 and their further development may satisfy a very high level of requirements and true obstacles lie in the “muscles” of the future smart system. It is evident that power electronics converters are present in any key module of the smart energy distributed systems. They are providing energy conversion and transfer and can be considered like “muscles” of the system. Such parameters like power density, weight, efficiency, reliability and cost of power electronics facilities define the feasibility of the abovementioned modern concept. Research and development of the power electronics facilities is a contribution to the future smart system.

3 Calculation Approach

This section focuses on the calculation of the passive elements of the circuit. To calculate the voltage drop and currents that flow through electrical components, the steady state analysis is used. Switches are assumed as ideal (Fig. 1).

3.1 qZS

The qZS converter in a boost mode is controlled by a single switch T 2 (T 1 and T 3 are OFF). To reduce the conduction losses in the diode, T 1 and T 3 are opened when freewheeling diodes of these switches are conducting.

A period of switching consists of two time intervals: when the switch T 2 is opened (time interval T 0 ) and when the transistor is not conducting (time interval T 1 ).

Assuming that, energy flows from the battery, and the output source can be replaced by a load, or simply, by a resistor.

When the switch T 2 is opened (transistor is conducting), T 1 and T 3 are OFF (Fig. 2a). In this case, it possible to determine the voltage drop across the inductors L 1 and L 2 , the output current (current of discharging the capacitor C 3 ). Since voltage drop across the passive components equals the voltage source, it can be expressed for a circuit that consists of the inductor L 1 , the capacitor C 2 , and the input voltage source (battery):

When the switch T 2 is close (transistor is not conducting), freewheeling diodes conductivity of switches T 1 and T 3 is present (Fig. 2b). In the passive mode of operation, it is possible to determine voltages drop across the inductors L 1 and L 2 , voltages across the capacitors C 1 and C 2 :

Taking into account that the average voltage of the inductors over one switching period is zero and the average current of the capacitors over one switching period also equals zero, we obtain

Considering the above, it is possible to derive voltages across the capacitors C 1 and C 2 and the output voltage, through input source voltage and duty cycle for the boost converter qZS [15, 16]:

During the period, currents through the inductor vary linearly (Fig. 3). Thus, the input current can be linearized as well. It is well known that the input ripple factor is the ratio of the input current ripple to a steady component of the current:

Taking into account that capacitor voltage change during the period is negligible, the ripple current along with the steady state component can be expressed as:

Thus, based on Eqs. (4)–(6), the values of the inductances \( L_{1} \) and \( L_{2} \) are completely identical and can be estimated as:

The output ripple factor is determined as the ratio of the output voltage ripple to a steady component of the output voltage:

Similar to the input current, during the period, output voltage varies linearly (Fig. 3); thus, the output voltage can be linearized:

Thus, based on Eqs. (4), (8) and (9), and considering that a load resistor can be expressed through power, required output capacitance can be obtained as:

Similarly, capacitance of the capacitors C 1 and C 2 can be found where the ripple factors are equal (K C1 = K C2 = K OUT ):

To further simplify analysis, it is assumed that both passive elements are equal and that the voltage of the inductors and the capacitors corresponds to \( V_{IN} = V_{OUT} /2 \):

3.2 Traditional Boost Converter

A traditional converter is calculated by the same approach [8]. Table 1 shows the results of calculation for both converters.

4 Simulation Results

Figure 4 shows the ripple of the input current and the output voltage for two converters. It can be seen that the steady state current and steady state voltage are the same in the two cases. But it is also shown that the ripple of the output voltage qZS converter is not of a linear character like that of a conventional converter. But absolute peak values correspond to the expected and coincide with the calculation part. Thus, it can be implemented in the experiment.

In the simulation (for both converters), the following parameters were taken into account: P = 100 W, f = 50 kHz, V IN = 6 V, V OUT = 12 V, K OUT = 1.2%, K IN = 20%.

5 Comparative Analysis

The theoretical equations (Table 1) and simulation results presented in previous sections can be represented graphically. Figure 5 shows the curves for passive elements estimated in relative units as a function of the input voltage.

To estimate the contribution of power switches and passive elements to the volume of the converter, the following criteria were taken into consideration. First of all, voltage stress on semiconductors and conduction losses in semiconductors were considered:

Energy stored in the inductors and maximum energy stored in the capacitors is proportional to their volume:

Based on the above formulas (13) and (14), results for each considered topology are presented in Table 2. The acquired expressions is valid only for the CCM operation mode.

Numeric representation in relative units for boost coefficients 1.1 and 4 are shown in Fig. 6 (RMS current for the calculation of conduction losses was taken from the modeling results). Radial diagrams were built at constant output power for the boost operational mode. From the diagrams can be concluded that qZS converter by comparison to the conventional bidirectional dc-dc topology has larger volume of passive components and also larger losses in semiconductor devices. That is so due to the double quantity of passive elements and an additional switching element. Thus, larger size and volume are needed to store extra energy and in addition, total voltage stress is increasing slightly.

Figure 6c shows that at high boost coefficients, the qZS converter shows even worse results than at low coefficients (Figs. 6a and b). Also, the losses in the qZS converter is higher. Though the duty cycle of the conducting transistor is twice reduced, the peak value of current is twice larger, and as a result, the RMS value of the current is larger.

6 Conclusions

This paper presents the comparative analysis of qZS and conventional bidirectional dc-dc topologies. In the analysis, four parameters were taken into account: energy stored in the inductive and capacitive passive elements (which are reflected in their volumes), voltage stress on the semiconductor devices and conduction losses.

The comparison shows that the characteristics of the qZS topology are worse than those for the conventional solution in almost all cases in the boost mode of operation. Only when the boost coefficient dropped close to 1.1, the topologies showed similar results. The reason lies in the larger number of passive components and semiconductors. As a result, the cost, volume and complexity are higher, which restricts the use of that topology in real applications. The conventional solution seems to be preferable in the application discussed.

References

Renewables 2016 Global Status Report. Renewable Energy Policy Network for the 21st Century, REN21, France (2016)

Solar Energy White Paper, Where we are Now and What’s Ahead, Natcore Technology. New Orleans (2012)

The Future of Solar Energy, An Interdisciplinary MIT Study. Massachusetts Institute of Technology (2015)

IEA PVPS International Energy Agency Photovoltaic Power Systems Programme. IEA PVPS Report: 2014 Snapshot of Global PV Markets, March 2015. http://www.iea-pvps.org/fileadmin/dam/public/report/technical/PVPS_report_-_A_Snapshot_of_Global_PV_-_1992-2014.pdf

Carbone, R.: Energy Storage in the Emerging Era of Smart Grids. InTech, Rijeka (2011)

Howey, D.A., Mahdi Alavi, S.M.: Rechargeable Battery Energy Storage Systems Design. Wiley, Hoboken (2015)

Fernao Pires, V., Romero-Cadaval, E., Vinnikov, D., Roasto, I., Martins, J.F.: Power converter interface for electrochemical energy storage systems – a review. Energy Convers. Manag. 86, 453–475 (2014)

Basic calculation of a boost converter’s power stage, Application report SLVA372C – November 2009 – revised January 2014

Liu, S.-I., Liu, J., Zhang, J.: Research on output voltage ripple of boost DC/DC converters. Int. MultiConference Eng. Comput. Scientists 2, 1–5 (2008)

Chao, K.-H., Tseng, M.-C., Huang, C.-H., Liu, Y.-G.: Design and implementation of a bidirectional DC-DC converter for stand-alone photovoltaic systems. Int. J. Comput. Consum. Control 2(3), 44–55 (2013)

Tytelmaier, K., Husev, O., Veligorskyi, O., Yershov, R.: A Review of non-isolated bidirectional DC-DC converters for energy storage systems. In: II International Young Scientists Forum on Applied Physics and Engineering, pp. 1–7 (2016)

Ardi, H., Ajami, A., Kardan, F., Nikpour, S.: Analysis and implementation of a non-isolated bidirectional DC-DC converter with high voltage gain. IEEE Trans. Power Electron. 63(8), 4878–4888 (2016)

Mohammadi, M.R., Farzanehfard, H.: A new family of zero-voltage-transition nonisolated bidirectional converters with simple auxiliary circuit. IEEE Trans. Industr. Electron. 63(3), 1519–1527 (2015)

Eichhorn, T.: Boost converter efficiency through accurate calculation. In: Power Electronics Technology (2008)

Siwakoti, Y.P., Peng, F.Z., Blaabjerg, F., Loh, P.C., Town, G.E.: Impedance-source network for electric power conversion Part I: a topological review. IEEE Trans. Power Electron. 30(2), 699–716 (2015)

Zakis, J., Vinnikov, D., Roasto, I., Ribickis, L.: quasi-Z-Source inverter based bi-directional DC/DC converter: analysis of experimental result. In: 7th International Conference-Workshop Compatibility and Power Electronics, pp. 394–399 (2011)

Vinnikov, D., Roasto, I., Zakis, J.: New bi-directional DC/DC converter for supercapacitor interfacing in high-power application. In: 14th International Power Electronics and Motion Control Conference, pp. 38–43 (2010)

Husev, O., Blaabjerg, F., Roncero-Clemente, C., Romero-Cadaval, E., Vinnikov, D., Siwakoti, Y.P., Strzelecki, R.: Comparison of impedance-source networks for two and multilevel buck-boost inverter applications. IEEE Trans. Power Electron. 31(11), 7564–7579 (2016)

Panfilov, D., Husev, O., Blaabjerg, F., Zakis, J., Khandakji, K.: Comparison of three-phase three-level voltage source inverter with intermediate DC-DC boost converter and quasi-Z-Source inverter. IET Power Electronics 9(6), 1238–1248 (2016)

Liu, Y., Abu-Rub, H., Ge, B., Blaabjerg, F., Ellabban, O., Loh, P.C.: Impedance Source Power Electronics Converters. Wiley, IEEE Press, Hoboken (2016)

Acknowledgments

This research work has been supported by Latvian National Research Programme “LATENERGI”, Latvian Council of Science (Grant 673/2014) and co-supported by Ukrainian Ministry of Education and Science (Grant № 0116U004695 and № 0116U006960).

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Copyright information

© 2017 IFIP International Federation for Information Processing

About this paper

Cite this paper

Matiushkin, O., Husev, O., Tytelmaier, K., Kroics, K., Veligorskyi, O., Zakis, J. (2017). Comparative Analysis of qZS-Based Bidirectional DC-DC Converter for Storage Energy Application. In: Camarinha-Matos, L., Parreira-Rocha, M., Ramezani, J. (eds) Technological Innovation for Smart Systems. DoCEIS 2017. IFIP Advances in Information and Communication Technology, vol 499. Springer, Cham. https://doi.org/10.1007/978-3-319-56077-9_40

Download citation

DOI: https://doi.org/10.1007/978-3-319-56077-9_40

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-319-56076-2

Online ISBN: 978-3-319-56077-9

eBook Packages: Computer ScienceComputer Science (R0)