Abstract

The increasing demand for performance improvements in radiation detectors, driven by cutting-edge research in nuclear physics, astrophysics and medical imaging, is causing not only a proliferation in the variety of the radiation sensors, but also a growing necessity of tailored solutions for the front-end readout electronics. Within this work, novel solutions for application specific integrated circuits (ASICs) adopted in high-resolution X and \(\upgamma \) ray spectroscopy applications are studied. In the first part of this work, an ultra-low noise charge sensitive amplifier (CSA) is presented, with specific focus on sub-microsecond filtering, addressing the growing interest in high-luminosity experiments. The CSA demonstrated excellent results with Silicon Drift Detectors (SDDs), and with room temperature Cadmium-Telluride (CdTe) detectors, recording a state-of-the-art noise performance. The integration of the CSA within two full-custom radiation detection instruments realized for the ELETTRA (Trieste, Italy) and SESAME (Allan, Jordan) synchrotrons is also presented. In the second part of this work, an ASIC constellation designed for X-Gamma imaging spectrometer (XGIS) onboard of the THESEUS space mission is described. The presented readout ASIC has a highly customized distributed architecture, and integrates a complete on-chip signal filtering, acquisition and digitization with an ultra-low power consumption.

You have full access to this open access chapter, Download chapter PDF

Similar content being viewed by others

1 Introduction

Semiconductor radiation detectors (SRDs) are indispensable elements in a large variety of scientific, industrial and medical instruments. Since 1980 they have experienced a rapid development not only as part of large-scale high-energy physics experiments and in space missions aimed at universe observation for astrophysics studies, but also in multidisciplinary facilities, such as synchrotron light sources, pushing the frontier of the research in a multitude of areas, especially in material and life sciences. Despite the diversification of the design focus required in each application, one can always identify three main functional blocks in a radiation detection system; the sensor, or the detector, is the first element, where the radiation physically undergoes an interaction that will produce an electric charge Q proportional to the photon deposited energy. This charge is collected by the front-end electronics (FEE) or readout electronics, and converted into a voltage or a current signal, which constitutes the second functional block in the radiation detection chain; since its invention in 1955 [1], the charge sensitive amplifier (CSA) is the most used solution for the realization of the first amplification stage of charge signals generated by the sensor, which basically consists of a low-noise amplifier operated with a capacitive negative feedback. Finally the back-end electronics (BEE) is responsible for the additional signal processing, digitization and data transmission of the desired information (energy, time-stamping, position of interaction, etc.), which completes the application. By all means, the border which separates the FEE from the BEE can be subject to different interpretations, according to the specific design cases. Within this text we will refer to the BEE as the electronics that can be considered to be more robust to noise issues—thanks to the beneficial processing of the FEE—and typically more relaxed in terms of area occupation, signal routing and power consumption, so that the BEE will be more likely to be placed further from the detection plane.

When in 1984 Emilio Gatti and Pavel Rehak proposed a novel ingenious charge transport mechanism for silicon detectors, which took the name of semiconductor drift chambers or silicon drift detectors (SDD) [2], a revolution in the performance of semiconductor detectors started; these detectors allowed to obtain the same spatial resolution of microstrip detectors using a much reduced number of preamplifiers, showed an architecture which could make the detector’s capacitance independent of the detector’s active area, with an unprecedented improvement in the noise performances, and was based on the planar technology, which, at the time, was already well consolidated. Due to the delicate inter-operation between the sensor and the FEE, this innovation leap pushed the development of tailored readout electronics and, with the advent of integrated circuits (IC), a new world of possibilities in terms of customization and integration for both the FEE and BEE, whose extreme performances in nuclear microelectronics are still topic of research and investigation.

Within this work the latest results of the state of the art ICs for low capacitance (<0.2 pF) X and \(\upgamma \) ray detectors are presented. In the first part of this chapter, an ultra-low noise CSA for synchrotron radiation facilities will be shown: the paramount requirement of a high-resolution performance, and the relaxed constraints on the power budget and area occupation, represent a golden opportunity to realize a preamplifier with state-of-the-art characteristics in terms of noise and speed. On the other hand, in the second part, the design of a complete readout chain of an X/\(\upgamma \) imaging spectrometer for astrophysics radiation instrumentation will be described, which is an example of a highly customized application specific integrated circuit (ASIC) with a complex multi-channel distributed architecture.

2 SIRIO-6: A New Generation of CSAs for High-Rate, High-Resolution X-/\(\upgamma \)-ray Spectroscopy

The quest for a minimum noise solution for the amplification of charge signals produced by SRDs mostly relies on the correct choice of a front-end device, capable of assuring a high gain and a low noise.Footnote 1 For CSAs realized in CMOS technology, proposed for the first time in 1997 [3], the optimal noise performance can be reached at the so-called capacitive matching condition on the total gate capacitance, which has a different expression according to the dominant noise component [4], that, in turn, is subject to the desired (or available) processing time in the acquisition chain. Among the main challenges in the realization of CSAs, the balance between the noise performance, and the processing speed is surely a topic of recent interest; indeed, new generation detection systems are often required to withstand high input photon rates (up to several million-counts per second), keeping an adequate spectroscopic resolution. In the framework of the realization of two new custom radiation detection systems for the Elettra synchrotron in Trieste (Italy) and the SESAME synchrotron in Allan (Jordan) a new family of fast, pulsed-reset preamplifiers, named SIRIO-6, has been developed. The main aim of this project is to move the design-focus toward sub-microsecond processing times, allowing such research-grade systems to move toward the million-counts per second range (Mcps). In this section the SIRIO-6 experimental characterization will be presented showrly presented, together with the integration on the complete detection systems at the Elettra and SESAME synchrotrons.

2.1 SIRIO for High Resolution Silicon Drift Detectors

Being optimized for low capacitance SRDs, SIRIO-6 finds its ideal application in combination with SDDs, that, due to their excellent noise performance at non-cryogenic temperatures, are among the most widely used devices in energy dispersive spectroscopy (EDS). With respect to previous designs, SIRIO-6 has been concieved with the specific goal of optimizing the noise performance at fast processing times—generally identified in terms of the peaking-time (\(\tau _{peak}\)) of the following filtering stages—and to have a rapid transient response and low reset dead-time [5]. In Fig. 3.1 a comparison between the spectroscopic resolution on the 55Fe 5.9 keV line using the new SIRIO CSA with respect to a previous generation is shown at different peaking times, when connected to a 10 mm\(^2\) SDD with similar leakage performance. The measurement, reported at a moderate cooling of \(-35\,^\circ \)C shows a drastic improvement in the noise performance, especially at the lowest peaking times, with an excellent full width half-maximum (FWHM) of 138.4 eV on the Mn-\(\mathrm{K}_{\alpha }\) line at the peaking time of 0.1 \(\upmu \)s, corresponding to an ENC of 8.1 el. r.m.s., which is among the best found in literature for such a fast shaping at the time of writing [6]. The optimum resolution is achieved at 5.6 \(\upmu \)s, where a FWHM of 122.7 eV at 5.9 keV is recorded, corresponding to an electronic noise of 3.4 el. r.m.s. (29.9 eV FWHM).

In the upper part, the 5.9 keV Mn-\(\mathrm{K}_{\alpha }\) FWHM measured with the new SIRIO-6 (in red) with respect to the best performance of the previous SIRIO generation (in blue), using a silicon drift detector at moderate cooling (\(-35\,^\circ \)C). The bottom lines represent the estimated electronic noise as obtained by subtracting the Fano noise contribution

2.2 SIRIO for CdTe Detectors at Deep Sub-microsecond Signal Processing Times

Due to their low detection efficiency, silicon detectors are not suited for high-energy photons (>20 keV). With this respect, thanks to their excellent absorption efficiency and their wide bandgap voltage which allows room temperature operation, CdTe and CdZnTe detectors are attracting a growing interest in the scientific and industrial community. The SIRIO-6 CSA specifications well match the needs of these kind of compound semiconductor detectors, especially at high fluxes of radiations, which are required to minimize the acquisition time in high-throughput X-/\(\upgamma \)-ray scanners used for medical diagnostic, quality control and homeland security. Using SIRIO-6 and a custom array of CdTe pixels, we were able to achieve at \(\tau _{peak}=50\) ns an electronic noise of around 37.6 el. r.m.s., with negligible contribution from the leakage current shot noise. The optimum performance is obtained at 1 \(\upmu \)s where an electronic noise of approximately 19.7 el. r.m.s. allows the acquisition of an unprecedented high-resolution spectrum for CdTe detectors, shown in Fig. 3.2: on the 59.5 keV line the resolution of \(\sim \)0.78% recorded using the new SIRIO-6 preamplifier improves by a factor of two the state-of-the-art performance previously reported in literature under similar experimental conditions [7]. The usage of the SIRIO-6 CSA with the described detector array demonstrated the feasibility of high-resolution spectroscopy with CdTe detectors at room temperature and at deep sub-microsecond processing times, potentially opening the path for new applications of CdTe detectors in those systems requiring a high detection efficiency and high count-rate capability in the soft-\(\upgamma \) energy range, without sacrificing the spectroscopic resolution.

2.3 Detection Systems for the Elettra and SESAME Synchrotrons

As part of the INFN-ReDSoX project, the SIRIO CSA is currently being integrated into two newly designed detection systems dedicated to the TwinMic beamline at the Elettra synchrotron in Trieste (Italy) and to the XAFS beamline at the SESAME synchrotron in Allan (Jordan) (Fig. 3.3).

The 32-channel low-energy X-ray fluorescence (LEXRF) detector for the TwinMic system, a first of its kind to integrate a microscopic imaging and spectroscopic capability, uses a high-gain version of the SIRIO preamplifier, to achieve the best results on low-energy photons. The complete detector has a noticeable total area of 12 300 mm\(^2\), and thanks to a multi-element SDD architecture allows a wide solid angle coverage of 1.57 steradiants around the specimen, that largely increases the detection efficiency with respect to the previously adopted detection system, and measured a best energy resolution of 125 eV FWHM on the 5.9 keV line [8]. The X-ray absorption and fine structure (XAFS) detector for SESAME, on the other hand, adopts SIRIO to realize a high-count-rate detection system with 64 channels; the detector is capable of reaching 15.5 Mcps, a significant improvement with respect to commercially available systems for similar applications, and the best performing pixels registered a resolution below 150 eV FWHM on the 5.9 keV at moderate cooling [9]. The achieved results on the TwinMic/XRF and on the SESAME/XAFS detectors realized by the ReDSoX collaboration, have shown that the SIRIO preamplifier is sufficiently mature to be integrated in complex multi-channel applications. On the other hand, the development of new XAFS detection system at the Elettra synchrotron, based on the one realized for SESAME, but with the possibility of in-vacuum operation, is scheduled in the next few years, which will most likely encourage the realization of a low-power version of the SIRIO-6 preamplifier.

3 Application Specific Integrated Circuits for Satellite Instrumentation

The observation of the high energy transients coming from the deep space is a fundamental tool for the understanding of a multitude of astrophysical phenomena. Especially since 2017—when for the first time the simultaneous detection of gravitational waves (GWs) and short gamma ray bursts (GRBs) generated by the same binary neutron star merger has been observed—a new era of multi-messenger astrophysics started: observing the sky with a wide field of view and covering a large frequency range can be extremely useful to trigger the observation and accurate localization of GRBs, which, in turn, enable the search of GWs associated with these high-energy electromagnetic emissions. However, due to the absorption of X and \(\upgamma \) photons in the atmosphere, satellite instrumentation is needed for such specific purpose.

Within the THESEUS (Transient High Energy Sky and Early Universe Surveyor) space mission concept, the design of a low-power low-noise ASIC for the readout of the on-board X-\(\upgamma \) imaging spectrometer (XGIS) has been carried out. The ASIC, organized in a chipset constellation named ORION, features a dual dynamic range for separate X-ray (2−20 keV) and \(\upgamma \)-ray (20–20 000 keV) processing based on a double detection mechanism which combines the usage of SDDs and Thallium activated Cesium-Iodide scintillators. The small power budget, typical of battery operated systems, moved the ASIC toward ultra-low current solutions. On the other hand, the necessity of the XGIS instrument to detect and process with high resolution a wide energy range of incoming photons led to the implementation of a smart on-chip discrimination between X and \(\upgamma \) events, which are conveniently processed by two independent channels of the ORION ASIC.

3.1 The X and \(\upgamma \) Imaging Spectrometer for the THESEUS Space Mission Concept

The on-board XGIS is composed by two cameras, each one based on a large (\(\sim \)50\(\times \)50 cm\(^2\)) highly segmented detection plane of 6 400 CsI(Tl) crystal scintillator bars (4.5 \(\times \) 4.5 \(\times \) 30 mm\(^3\)) optically coupled to 12 800 SDD pixels, realizing a wide field deep sky monitor in the 2 keV–20 MeV energy band [10]. The single detection element, shown in Fig. 3.4, is composed by a scintillator crystal, optically isolated with respect to its neighbours by means of a reflective wrapping, and two SDDs, one at the top and one at the bottom of the bar. The reconstruction of both low energy (<20 keV) and high energy (up to 20 MeV) photons information (energy, position and timing) is possible through appropriate processing of the charge generated by coincident illumination of the top and bottom SDDs.

The XGIS double detection operating principle, composed by on CsI(Tl) bar and two SDDs. In such configuration, the radiation entrance window is facing the top SDD of each CsI(Tl) crystal, so that low-energy photons (<20 keV) are absorbed by the SDD at the top interface, while high-energy photons (up to 20 MeV) pass through the top SDD and are absorbed in the CsI(Tl) crystal whose scintillation light illuminates both the SDDs

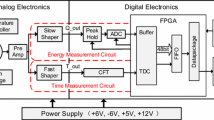

Among the main challenges faced in the presented ASIC, it must be mentioned the large number of pixels, of relatively large area, present in the concept of the XGIS-camera (12 800 pixels of 25 mm\(^2\) each for the complete system), which oriented the design in a chipset, or chip constellation, architecture where a large number of front-end ASICs, placed a few millimeters from the detectors, send a partially shaped signal to a limited number of multi-channel back-end ASICs, which are responsible for the final processing and digitization of the front-end signals. With an on-chip photon discrimination, filtering, analog-to-digital conversion and time-stamping capability, the ORION-BE, realized in collaboration with University of Pavia, can interact directly with an on-board FPGA via SPI protocol.

3.2 The ORION Circuit Architecture

A schematic representation of the pixel readout strategy with the ORION chipset is shown in Fig. 3.5, and includes 2\(\times \)ORION-FE chips and 1\(\times \)ORION-BE channel. The charge generated by each pixel on the top SDD (in case of a low-energy X event) or by both top and bottom SDDs (in case of a \(\upgamma \) event) is processed independently by the ORION-FEs, glued in close proximity of the SDD anodes. The ORION-FE provides the fundamental amplification and processing to the charge signal, and integrates a charge sensitive amplifier in continuous reset configuration—required by timing applications as in the case of THESEUS −, a pole-zero compensation network, and a current conveyor, which is responsible for the first CR shaping and for signal transmission to the ORION-BE. The signals are transmitted in current mode, in an approach already successfully tested on the LYRA chipset, on board the HERMES nanosatellites, which minimizes the cross-talk in multi-channel architectures [11]. The current outputs of the ORION-FE top and bottom channels of the same pixel are delivered to two current receivers in the ORION-BE channel, positioned up to \(\sim \)4–5 cm far from the respective FE. Internally, the ORION-BE includes an X-channel, which takes only the signal coming from the top FE, and a \(\upgamma \)-channel, which processes the signals coming from both the top and bottom channels.

The X-channel shaping amplifier is a first-order semi Gaussian-Shaper. The shaped signal is compared by an amplitude discriminator with an internally programmable X-threshold; when the amplitude discriminator toggles the peak stretcher is enabled and a peak discrimination block (not shown) recognizes that the peak amplitude of the signal has been reached. The peak detector thus flags to the logic to disconnect the input line, to reduce the probability of pile-up events, and assigns to the photon a unique time-stamp. The ASIC waits a programmable time interval before registering the trigger status, in order to give sufficient time to other channels to settle to a stable value. The stretched output voltage is then over-sampled by a second order 12 bit incremental A/D converter, designed by University of Pavia. When the acquisition at the BE is completed, the central logic sends an end-of-conversion flag, to properly reset the channel for a new acquisition.

At the same time, the signal from the top current receiver is processed also by the \(\upgamma \)-channel. In this case, the \(\upgamma \)-shaper realizes a third order semi-Gaussian shaping, which is more suitable for the long scintillation time-constants of CsI(Tl) bars, and is replicated also on the bottom channel. The outputs on the top and bottom channels, are summed in current mode to eventually trigger the amplitude discriminator and start the digital processing by the \(\upgamma \) channel logic, that operates similarly to the X-channel one. If the \(\upgamma \) amplitude discriminator toggles, meaning that a high-energy signal has been detected, the X-channel output is discarded. Two independent stretchers and ADCs are then used to digitize the outputs of the \(\upgamma \) shapers, which are eventually summed in the digital domain for a more accurate reconstruction, until an end-of-conversion signal is sent back to reset the analog BE.

3.3 Experimental Results

The performances and functionalities of the ORION ASIC coupled to a silicon drift detector have been tested and extensively characterized using a dedicated board designed by INAF-IASF (Milan), shown in Fig. 3.6. The spectroscopic resolution of the prototype was tested using \(^{241}\)Am and \(^{55}\)Fe calibration sources to acquire different energy spectra across the expected operating temperature range (\(+20\,^{\circ }/-20\,^{\circ }\) C). The optimum ENC at \(-20\,^{\circ }\)C on the X-channel is 24.3 el. r.m.s. (corresponding to 212 eV FWHM on Si), and 39.6 el. r.m.s. on the \(\upgamma \)-channel (corresponding to 3.7 keV FWHM on CsI(Tl)). At the nominal operating temperature of the XGIS module (+10 \(^{\circ }\)C) an ENC of 27.8 el. r.m.s. (241 eV FWHM on Si) on the X-channel, and 43.6 el. r.m.s. (4.1 keV FWHM on CsI(Tl)) \(\upgamma \)-channel are recorded.

First prototype of the test-board used for the ORION-ASIC experimental measurements. The board includes two ORION-FE, one ORION-FE and one multi-element SDD with 4 pixels of 25 mm\(^2\) each, designed by INFN and produced by Fondazione Bruno Kessler (FBK). The spectra have been acquired sampling the output waveform of the ORION pulse-shaper with a commercial multi-channel analyzer by Amptek

At the nominal operating temperature of +10 \(^{\circ }\)C, the measured energy threshold of the internal pulse-amplitude discriminator is 563 eV, for X-ray events, and 42 keV for \(\upgamma \)-ray events. The analog-processor is able to correctly shape and stretch the input pulses with the designed peaking times (1 \(\upmu \)s for X-channel, 3 \(\upmu \)s for \(\upgamma \)-channel) and producing a look-at-me signal for the ADC when the peak level is reached with a delay between 0.7 and 1 \(\upmu \)s. The linearity error of the ASIC in the operative energy range has been measured to be ±1% for the X-channel (over an input charge range of \(\sim \)10 000 el.) and ±1.5% for the \(\upgamma \)-channel (over an input charge range of \(\sim \)100 000 el.), a performance which will guarantee an accurate reconstruction of the acquired spectra over the complete 4 decades energy band.

4 Concluding Remarks

It is a common misconception to consider nuclear microelectronics only as a supportive and subsidiary mean to the advancement of radiation instrumentation; on the contrary, it should be unmistakable that even mature detection technologies can still reap the fruits of recent progress in microelectronics research. The development of integrated circuits for semiconductor radiation detectors described within this work highlights such an important remark, showing in several applications, how a dedicated electronics can help reaching the ultimate performance limits of silicon drift chambers, set-up new challenges for the room temperature detection, and, eventually, allow the integration of complex processing architectures on-board satellite instrumentation, for the advancement of astrophysics and space science.

Notes

- 1.

The noise figure (also known as the excess noise ratio) is historically the most common quality factor for low-noise amplifier designs. Nevertheless, this parameter, whose definition is based on the assumption of a conventional fixed noise at the input source, is not suitable for the description of CSA, which are rather characterized by their equivalent noise charge (ENC).

References

C. Cottini, E. Gatti, G. Giannelli, G. Rozzi, Minimum noise pre-amplifier for fast ionization chambers. Il Nuovo Cimento (1955-1965) 3(2), 473–483 (1956)

E. Gatti, P. Rehak, Semiconductor drift chamber—an application of a novel charge transport scheme. Nucl Instrum Meth A (1984). https://doi.org/10.1016/0167-5087(84)90113-3

G. Gramegna, P. O’connor, P. Rehak, S. Hart, CMOS preamplifier for low-capacitance detectors. Nucl. Instrum. Meth. A (1997). https://doi.org/10.1016/S0168-9002(97)00390-2

G. Bertuccio, S. Caccia, Noise minimization of MOSFET input charge amplifiers based on \(\Delta \)\(\mu \) and \(\Delta \)N 1/f models. IEEE T Nucl Sci (2009). https://doi.org/10.1109/TNS.2008.2012347

F. Mele, J. Quercia, G. Bertuccio, Analytical model of the discharge transient in pulsed-reset charge sensitive amplifiers. IEEE T. Nucl. Sci. (2021). https://doi.org/10.1109/TNS.2021.3087420

F. Mele, M. Gandola, G. Bertuccio, SIRIO: a high-speed CMOS charge-sensitive amplifier for high-energy-resolution X-\(\gamma \) ray spectroscopy with semiconductor detectors. IEEE T. Nucl. Sci. (2021). https://doi.org/10.1109/TNS.2021.3055934

M. Sammartini, M. Gandola, F. Mele et al., A CdTe pixel detector-CMOS preamplifier for room temperature high sensitivity and energy resolution X and \(\upgamma \) ray spectroscopic imaging. Nucl. Instrum. Meth. A (2018). https://doi.org/10.1016/j.nima.2018.09.025

J. Bufon, S. Schillani, M. Altissimo et al., A new large solid angle multi-element silicon drift detector system for low energy X-ray fluorescence spectroscopy. J. Instrum. (2018). https://doi.org/10.1088/1748-0221/13/03/C03032

A. Rachevski, M. Ahangarianabhari, G. Aquilanti et al., The XAFS fluorescence detector system based on 64 silicon drift detectors for the SESAME synchrotron light source. Nucl. Instrum. Meth. A (2019). https://doi.org/10.1016/j.nima.2018.09.130

C. Labanti et al., The x/gamma-ray imaging spectrometer (XGIS) on-board THESEUS: design, main characteristics, and concept of operation, in Space Telescopes and Instrumentation 2020: Ultraviolet to Gamma Ray (2020). https://doi.org/10.1117/12.2561012

M. Gandola, M. Grassi, F. Mele et al., LYRA: a multi-chip ASIC designed for HERMES X and gamma ray detector, in IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC) (2019). https://doi.org/10.1109/NSS/MIC42101.2019.9059616

Acknowledgements

This work was carried out within the ReDSoX project of INFN and the THESEUS project of INAF-ASI. The contribution of universities and research institutes taking part in the collaboration is acknowledged: Polytechnic of Milan, University of Pavia, University of Trieste, University of Udine, University of Bologna, Fondazione Bruno Kessler, Elettra Sincrotrone di Trieste, Italian Space Agency (ASI), Italian National Institute of Astrophysics (INAF), Trento Institute for Fundamental Physics and Applications and Karlsruher Institut für Technologie.

Author information

Authors and Affiliations

Corresponding author

Editor information

Editors and Affiliations

Rights and permissions

Open Access This chapter is licensed under the terms of the Creative Commons Attribution 4.0 International License (http://creativecommons.org/licenses/by/4.0/), which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license and indicate if changes were made.

The images or other third party material in this chapter are included in the chapter's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the chapter's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder.

Copyright information

© 2022 The Author(s)

About this chapter

Cite this chapter

Mele, F. (2022). Application Specific Integrated Circuits for High Resolution X and Gamma Ray Semiconductor Detectors. In: Piroddi, L. (eds) Special Topics in Information Technology. SpringerBriefs in Applied Sciences and Technology(). Springer, Cham. https://doi.org/10.1007/978-3-030-85918-3_3

Download citation

DOI: https://doi.org/10.1007/978-3-030-85918-3_3

Published:

Publisher Name: Springer, Cham

Print ISBN: 978-3-030-85917-6

Online ISBN: 978-3-030-85918-3

eBook Packages: EngineeringEngineering (R0)