Abstract

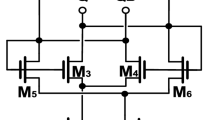

This paper presents a fully integrated Integer-N Phase Locked Loop (INPLL) for ZigBee applications. In this paper the effects of delay in the reset path of Phase and Frequency Detector (PFD) and current gain mismatch in the Charge Pump (CP) on the spectral purity of the Local Oscillator (LO) signal of INPLL is studied theoretically. Then a linearization technique is introduced for a conventional CP to minimize the current gain mismatch and also a modified PFD is presented to achieve a fully symmetrical structure in order to simplify physical verification. The proposed linearization technique of the CP leads to minimize the current gain mismatch from 8.5 to 2.5 µA and the linearity range enhanced 7 times more than conventional structure. Finally, an INPLL is implemented in 0.18 µm CMOS standard to use in ZigBee applications. Reference spurs of the LO signal of the designed INPLL are suppressed more than 8 dBc/Hz when the linearization technique is incorporating in the INPLL. The power consumption of the whole INPLL with a 1.8 V DC supply is 9.15 mW.

Similar content being viewed by others

References

Bhattacharyya, T. K., & Mandal, D. (2007). 7.95 mW 2.4 GHz fully-integrated CMOS integer N frequency synthesizer. In 20th International conference on IEEEVLSI design. Held jointly with 6th international conference on embedded systems, 2007.

Sahafi, A., Aghdam, E. N., & Azadbakht, M. (2018). A dual band fractional-N frequency synthesizer with aself-calibrated charge pump for WLAN standards. Journal of Circuits, Systems, and Computers, 27, 1850131.

Bhattacharyya, T. K., Mandal, D., & Singh, S. K. (2005). Fully integrated CMOS frequency synthesizer for ZigBee applications. In Proceedings of the 18th international conference on VLSI design held jointly with 4th international conference on embedded systems design (VLSID’05).

Tiebout, M. (2001). Low-power low-phase-noise differentially tuned quadrature VCO design in standard CMOS. IEEE Journal of Solid-State Circuits, 36(7), 1018–1024.

Ferencic, I., Locher, M., Sedvallson, S., Voegeli, U., Wang, Z., & Vaucher, C. S. (2000). A family of low-power truly modular programmable dividers in standard 0.35 μm CMOS technology. IEEE Journal of Solid-State Circuits, 35(7), 1039–1045.

Yu, X.-P., Do, M. A., Lim, W. M., Yeo, K. S., & Ma, J.-G. (2006). Design and optimization of the extended true-single-phase-clock based prescaler. IEEE Transactions on Microwave Theory and Techniques, 54(11), 3828–3835.

Maneatis, J. G. (1996). Low-jitter process-independent DLL and PLL based on self-biased technique. IEEE Journal of Solid-State Circuits, 31(11), 1723–1732.

Azadmousavi, T., Azadbakht, M., Aghdam, E. N., & Frounchi, J. (2018). A novel zero dead zone PFD and efficient CP for PLL applications. Analog Integrated Circuits and Signal Processing, 95(1), 83–91.

Liang, C.-F., Chen, S.-H., & Liu, S.-I. (2008). A digital calibration technique for charge pumps in phase-locked systems. IEEE Journal of Solid-State Circuits, 43(2), 390–398.

Raja, M. K., Chen, X., Lei, Y. D., Bin, Z., Yeung, B. C. & Xiaojun, Y. (2010). A 18 mW Tx, 22 mW Rx transceiver for 2.45 GHz IEEE 802.15.4 WPAN in 0.18-µm CMOS. In IEEE Asian solid-state circuits conference.

Sahafi, A., Aghdam, E. N., Azadbakht, M. (2016). Low power fractional-N frequency synthesizer for IEEE 802.11 a/b/g/n standards in 90-nm CMOS. In 2016 24th Iranian conference on electrical engineering (ICEE).

Akhmetov, D. B., & Korotkov, A. S. (2018). The reference spur reduction technique for frequency synthesizers. In IEEE conference of Russian young researchers in electrical and electronic engineering (EIConRus).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Abdollahy Gharbali, M., Azadbakht, M., Feyzi, E. et al. A 2.4 GHz integer-N frequency synthesizer for ZigBee applications. Analog Integr Circ Sig Process 99, 167–175 (2019). https://doi.org/10.1007/s10470-019-01401-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-019-01401-5