natureresearch

# **OPEN** Electric-double-layer *p\_i\_n* junctions in WSe<sub>2</sub>

Sara Fathipour<sup>1</sup>, Paolo Paletti<sup>1</sup>, Susan K. Fullerton-Shirey<sup>2,3</sup> & Alan C. Seabaugh<sup>1⊠</sup>

While p-n homojunctions in two-dimensional transition metal dichalcogenide materials have been widely reported, few show an ideality factor that is constant over more than a decade in current. In this paper, electric double layer p-i-n junctions in WSe<sub>2</sub> are shown with substantially constant ideality factors (2-3) over more than 3 orders of magnitude in current. These lateral junctions use the solid polymer, polyethylene oxide: cesium perchlorate (PEO:CsClO<sub>6</sub>), to induce degenerate electron and hole carrier densities at the device contacts to form the junction. These high carrier densities aid in reducing the contact resistance and enable the exponential current dependence on voltage to be measured at higher currents than prior reports. Transport measurements of these WSe<sub>2</sub> p-i-n homojunctions in combination with COMSOL multiphysics simulations are used to quantify the ion distributions, the semiconductor charge distributions, and the simulated band diagram of these junctions, to allow applications to be more clearly considered.

Methods for forming p-n junctions in two-dimensional (2D) transition metal dichalcogenide (TMD) channels have been widely sought to enable electronic and optoelectronic applications<sup>1</sup>. Lateral TMD p-n junctions have been induced using a wide variety of approaches including buried gates (in WSe<sub>2</sub> by Pospischil<sup>2</sup>, Baugher<sup>3</sup>, and Ross<sup>4</sup>, and in MoS<sub>2</sub> by Sutar<sup>5</sup>), using combinations of buried gates and surface charge layers (in MoTe<sub>2</sub> by Lim<sup>6</sup>), by ion gating using solid polymers (in MoTe<sub>2</sub> by Xu<sup>7</sup> and in WSe<sub>2</sub> by Fathipour<sup>8</sup>), using ionic liquids (in WSe<sub>2</sub> by Kozawa<sup>9</sup> and Zhang<sup>1011</sup>), by chemical doping (in MoS<sub>2</sub> by Choi<sup>12</sup> and Li<sup>13</sup>), and by thickness-dependent workfunction engineering (in WSe<sub>2</sub> by Xu<sup>14</sup>). A vertical p-n homojunction was demonstrated by Jin<sup>15</sup> by transfer of Nb-doped, p-type MoSe<sub>2</sub> onto transferred, undoped, n-type MoSe<sub>2</sub> on SiO<sub>2</sub> and an ideality approaching unity was achieved. In addition to these homojunction demonstrations, many 2D p-n heterojunctions have been demonstrated, as reviewed in Frisenda<sup>16</sup>, but few of these reports are ideal in the sense that the forward current increases exponentially with voltage for decades in current. The most ideal heterojunction reported is obtained in a transferred, vertical p-WSe<sub>2</sub>/n-InAs stack, by Chuang<sup>17</sup>, showing an ideality factor of 1.1 over approximately 4 orders of magnitude in current.

In homojunction TMD p-n junctions, the most ideal junctions have been achieved using buried gates<sup>5</sup>, or an ion-containing (solid polymers or ionic liquid) electrolytes biased to create an electric double layer (EDL) at the semiconductor surface. The double layer consists of a cation-electron or an anion-hole layer with a high capacitance density (e.g. 4 μF/cm<sup>2</sup> as measured by Xu<sup>7</sup>). Once the double layers are formed, the ions are locked in place by cooling below a critical temperature. This method of doping in WSe<sub>2</sub> has produced contact resistances as low as 3.4 and 1 k $\Omega$  µm (n and p respectively) and currents as high as 58 and 50 µA/µm at  $|V_{DS}| = 2$  V (*n* and *p* respectively)<sup>18</sup>. The method of forming p-n junctions by application of EDLs has its roots in the light emitting electrochemical cell as discussed by Pei<sup>19</sup>, Gao<sup>20</sup>, and Edman<sup>21</sup>. Our aim in this paper is to analyze the current-voltage (I-V) characteristics of the  $WSe_2$  p-i-n junction using the solid polymer,  $PEO:CsClO_4$ . Through COMSOL multiphysics modeling we provide a quantitative physical understanding of the ion and carrier distributions in the electrolyte and channel. Simulation of EDL properties is of recent interest, as demonstrated by Ueda's<sup>22</sup> work using a drift-diffusion formalism. The doping method described in this paper has allowed demonstration of a homojunction WSe<sub>2</sub> Esaki tunnel diode<sup>23</sup>.

<sup>1</sup>Department of Electrical Engineering, University of Notre Dame, Notre Dame, IN 46556, USA. <sup>2</sup>Department of Chemical and Petroleum Engineering, University of Pittsburgh, Pittsburgh, PA 15213, USA. <sup>3</sup>Department of Electrical and Computer Engineering, University of Pittsburgh, Pittsburgh, PA 15213, USA. <sup>™</sup>email: seabaugh.1@ nd.edu

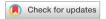

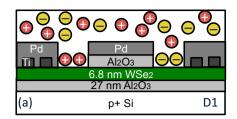

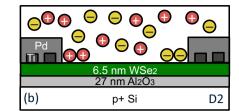

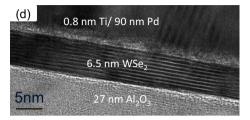

**Figure 1.** Schematic cross sections of two lateral WSe<sub>2</sub> p–i–n junctions: (a) with top gate (5.3 nm Al<sub>2</sub>O<sub>3</sub>), (b) without top gate. (c) TEM image of contact region (Pd/Ti/WSe<sub>2</sub>) of device D1 and (d) device D2. The TEMs correspond to the same devices for which electrical measurements are reported.

|                            | Device D1          | Device D2        |    |

|----------------------------|--------------------|------------------|----|

| Top gate length            | 1.5                | No top gate      | μm |

| WSe <sub>2</sub> thickness | 6.8                | 6.5              | nm |

| Channel length             | 1.7                | 3.5              | μm |

| Channel width              | 2                  | 4                | μm |

| Ti/Pd contacts             | 0.8/90             | 0.8/90           | nm |

| Cool-down bias             | $V_D = -V_S = 1.5$ | $V_D = -V_S = 2$ | V  |

**Table 1.** Device structure parameters. The cool-down bias lists the drain and source biases, which are fixed during cooling to immobilize the ions.

# Results and discussion

Schematic cross sections for two p-i-n junctions are shown in Fig. 1a,b, respectively, in two different channel structures. Following the benchmarking of Sylvia<sup>24</sup> for ultrascaled field-effect transistors (FETs), we focus on WSe<sub>2</sub> as the channel material. Device D1 has a centered top gate with an Al<sub>2</sub>O<sub>3</sub> thickness of 5.3 nm and device D2 has an open channel. Fabrication details are provided in the Methods section. The upper layer is the solid polymer electrolyte, PEO:CsClO<sub>4</sub>. The CsClO<sub>4</sub> dissociates into cations, Cs<sup>+</sup>, and anions, ClO<sub>4</sub><sup>-</sup>, as indicated by the circled + and - symbols in Fig. 1a,b. The metal contact to WSe<sub>2</sub> consists of an electron beam deposition of Ti to partially cover the exfoliated WSe<sub>2</sub> surface followed by Pd deposition. This leads to a dual work-function contact providing low Schottky barriers to both valence and conduction bands<sup>18</sup>. With a positive bias applied to the right contact with respect to the left contact, ions accumulate at the contacts as indicated in the schematic with the bulk of the PEO:CsClO<sub>4</sub> remaining charge neutral. An EDL forms where the ions accumulate. Shown in Fig. 1c,d are transmission electron microscope (TEM) images of the contact region made after electrical measurements were completed. An interfacial layer at the scale of approximately 1 nm can be seen at the metal contact/WSe2 interface. This contact is formed by partially covering the WSe2 with Ti and then completing the metallization with Pd. For this reason, some transition layer can be expected. This dual work-function contact yielded contact resistances as low as 1 and 3.4 k $\Omega$  µm for n and p type contacts, respectively, comparable to the best reports for  $WSe_2^{18}$ . The physical attributes of the two devices are summarized in Table 1.

To form the p-i-n junction, a positive bias is applied to the drain contact and a negative bias of the same magnitude is applied to the source contact, at room temperature. This accumulates negative ions at the drain contact and positive ions at the source contact, Fig. 1a,b. The ions then induce free carriers in the WSe<sub>2</sub> of opposite sign, i.e. electrons at the source and holes at the drain. The structure D1 enforces an undoped region in the center of the channel because the top gate keeps ions out of the central channel region, while the open structure D2 has a central undoped channel due to the charge neutral electrolyte in the region between the electrodes. Once the ions are positioned along the channel, they are locked into place by cooling the device below the glass transition temperature of the PEO:CsClO<sub>4</sub> (measured by Xu<sup>7</sup> to be 240 K) while maintaining the biases on the contacts. Below the glass transition temperature, the ions are immobilized and do not respond to external biases and the device can be tested without ion reconfiguration.

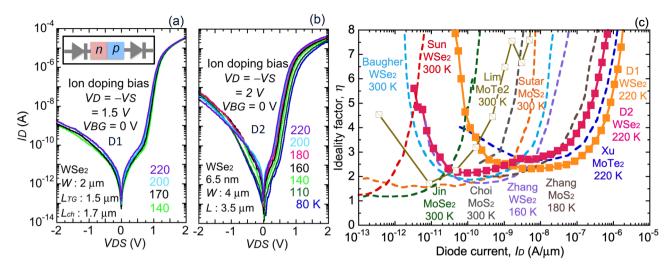

**Figure 2.** Temperature dependence of the I-V characteristics of WSe<sub>2</sub> p-i-n junctions exhibiting exponential turn-on and clear rectification: (a) device D1 and (b) device D2. The inset in (a) is a reminder that the p-i-n junction is in series with an n-Schottky (left source contact) and a p-Schottky (right drain contact). (c) Comparison of ideality factor vs current per width for D1 and D2 vs. published TMD homojunction p-n diodes.

The transfer characteristic of the p-i-n diodes, D1 and D2, are shown in Fig. 2a,b, respectively. The I-V characteristics show a clear rectifying behavior with a forward to reverse current ratio of  $\sim 28,000$  for D1 and  $\sim 2,000$  for D2. More notable is the exponential dependence of the current on voltage over more than 4 orders of magnitude in both device geometries. The p-i-n junction is in series with metal/WSe<sub>2</sub> Schottky contacts with an n-Schottky barrier on the left contact and a p-Schottky barrier on the right, Fig. 2a inset. Under forward bias, the two Schottky contacts are reverse-biased tunnel contacts resulting from the degenerate n and p carrier densities of the EDLs near the contact/channel edges. This series arrangement of Schottky barrier contacts means that the voltage across the junction will be somewhat less than the applied voltage.

The current in the forward-biased p-n junction,  $I=I_0 \exp[V/\eta V_T]$ , is predominantly controlled by the exponential factor  $V/\eta V_T$  where V is the voltage across the p-n junction,  $V_T$  is the thermal voltage,  $V_T = kT/q$ ,  $\eta$  is ideality factor,  $I_O$  is reverse saturation current, k is Boltzmann's constant, T is temperature, and q is fundamental charge. The ideality factor of D1 and D2 can be extracted from the forward biased I-V characteristic using  $\eta = [(kT/q)\ln(10)(d\log(I)/dV)]^{-1}$ , which is valid when the applied voltage is predominantly dropped across the p-n junction. Figure 2c compares the ideality factor vs. current in D1 and D2 vs. published TMD p-n homojunctions. In Zhang<sup>10</sup> and Sutar<sup>5</sup> the width of the MoS<sub>2</sub> junction was not specified and 4 μm is used. Choi's<sup>12</sup> report, on MoS<sub>2</sub> using chemical doping, is an example where the ideality factor varies strongly with current, which is likely due to a series resistance. Sutar<sup>5</sup> formed the p-i-n junction in MoS<sub>2</sub> electrostatically by applying asymmetric biases to buried gates. The ideality factor in Sutar's report is constant over 4 orders of magnitude in current with ideality less than approximately 2. The p-i-n junctions that extend to the highest currents in Fig. 2c were created by the formation of EDLs. Among these reports, Zhang 1011 used ionic liquids, while in the junctions of  $Xu^7$  and this work, PEO:CsClO<sub>4</sub> was used. The WSe<sub>2</sub> p-i-n junctions of this work exhibit substantially constant ideality factor vs. current, over 3 orders of magnitude; these lateral junctions show ideality factors ranging from 2 to 3. In contrast, the transferred MoSe, homojunction of Jin<sup>15</sup> exhibited nearly unity ideality, suggesting that trap-mediated generation/recombination<sup>25</sup> is playing a role in lateral junctions. In the lateral p-i-n junction, the reverse leakage is also higher than the reverse saturation current, consistent with traps playing a significant role.

While it may appear that the D2 junction has a larger temperature dependence than D1, this is only because the measured temperature range is larger for D2. The temperature coefficient,  $\Delta I/\Delta T$  of the forward current is similar in the two junctions 1.4 (nA/µm)/K in D1 and 1.1 (nA/µm)/K in D2 (at 10 nA, normalized by the junction width W). The positive temperature coefficient in forward bias is opposite to what is expected from the  $\exp(qV/kT)$  factor at fixed voltage. This is because the prefactor,  $I_O$ , depends on the energy band gap,  $E_O$ , making the full forward current proportional to  $\exp[-(E_G - qV)/kT]$  as outlined by  $\operatorname{Sze}^{26}$ , and giving a positive temperature coefficient.

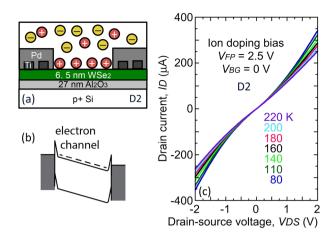

The temperature coefficient of the Schottky contacts and access region can be separated out in the same device. To facilitate this, device D2 was cooled to below the glass transition temperature of PEO, with a 2.5 V side gate bias and 0 V on the source and drain contacts. Thus, positive  $Cs^+$  ions are driven onto the WSe<sub>2</sub> surface, as indicated in Fig. 3a, to induce electrons in the channel, as described in the band diagram in Fig. 3b. Nonrectifying I-V characteristic were obtained as a result of this unipolar doping, Fig. 3c, and the temperature coefficient of the current is weakly negative.

A negative temperature coefficient is not readily explained from Schottky barrier transport, considering Schottky barrier lowering<sup>27</sup> and thermionic field-emission<sup>28</sup>. A negative temperature coefficient is instead an indication of mobility degradation with temperature due to phonon scattering, as is also observed in Si metal-oxide-semiconductor FET inversion layers<sup>29</sup>. A negative temperature coefficient of the conductance has also been observed in WSe<sub>2</sub> FETs using PEO:CsClO<sub>4</sub><sup>8</sup>. The measured series resistance can be directly measured from Fig. 3c in the linear region below 1 V, where 8.7 k $\Omega$  is obtained, corresponding to a channel resistivity

**Figure 3.** Unipolar doping of the WSe<sub>2</sub> channel in device D2, used to measure Schottky contact temperature dependence. (a) Schematic cross section under side gate bias to accumulate positive ions on the channel, doping the channel n-type. (b) Corresponding band diagram for unipolar n-doping. (c) Symmetric, nonrectifying characteristics are obtained. To support the highest current measured in Fig. 2 requires less than  $\sim 0.4$  V drop across the two contacts and access region.

of 6.5 m $\Omega$  cm, which is reasonable for WSe<sub>2</sub> mobility and sheet carrier density (100 cm<sup>2</sup>/Vs and 6×10<sup>12</sup>/cm<sup>2</sup>). Because both the p-i-n junction current and the series resistance increase with temperature, the voltage drop across the p-i-n junction decreases with temperature.

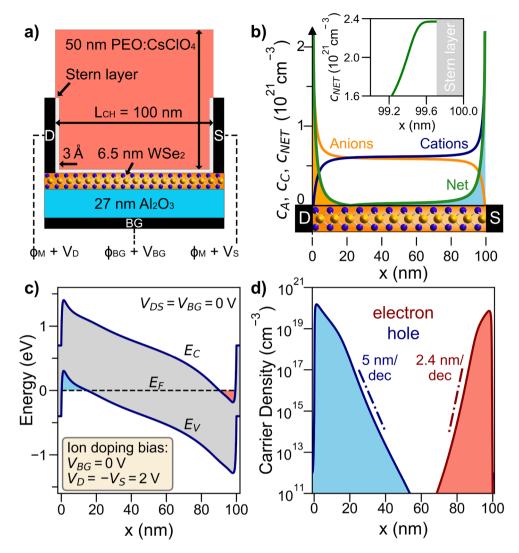

COMSOL multiphysics simulations were performed to better understand the EDL junction formation. Given that this junction formation method is yielding the most ideal and high current homojunctions it is of interest to quantify the expected carrier densities and profiles. Figure 4a represents the simulated device structure for device D2, consisting of a 100 nm-long, 6.5 nm-thick WSe<sub>2</sub> channel ( $E_G$  = 1.2 eV,  $\chi$  = 3.9 eV) on 27 nm Al<sub>2</sub>O<sub>3</sub>. A shorter channel was used than in the experiments to reduce the simulation time while being sufficiently long to capture the electrostatic lengths of the ion distributions. On top of the semiconductor channel, there is a 50 nm layer of PEO electrolyte at a concentration of 1,000 mol/L of monovalent anions and cations. The presence of a Stern layer defining the separation between the ions in the solid polymer and the carriers in the semiconductor channel, is taken into account by inserting a 0.3 nm vacuum layer.

A modified Poisson–Nernst–Planck (MPNP) theory of electrodiffusion accounting for steric effects at large applied biases is applied to calculate the dynamics of ions within the electrolyte  $^{2330}$ . The system of equations consists of the Poisson's equation for the electrostatics and the modified Nernst–Planck equation for ion transport. The semi-classical transport of electrons and holes in the semiconductor is described by a drift-diffusion model. The drift-diffusion equations consist of the Poisson's equation for electrostatics, and the continuity equation for electrons and holes. Dirichlet boundary conditions are applied at the metal contacts ( $\phi_M = 4.8~{\rm eV}, \, \phi_{BG} = 5.0~{\rm eV}$ ), while Neumann boundary conditions are used at the remaining boundaries. The semiconductor and the solid electrolyte domains are connected via an insulating interface so no charge transfer is enabled. Therefore, the two domains are coupled only electrostatically by means of the Poisson's equation.

The simulations follow the p-i-n junction formation protocol for device D2. First, at room temperature, the ion and semiconductor transport are solved self consistently, under an applied voltage of  $V_D = -V_S = 2$  V ( $V_{BG} = 0$  V) to build-up the desired ion distribution in the electrolyte. The in-line electric field splits the positive and negative ions and as Fig. 4b suggests, ions accumulate at the two contacts and decay exponentially towards the middle of the channel. The high bulk ion concentrations resulting in a Debye screening length of order  $\sim 1$  nm. To highlight the impact of the adopted MPNP, the inset of Fig. 4b shows the net ion concentration at the source extremity of the channel reaching a saturation value of  $c_{MAX} = 1/(N_A \, a^3) \approx 3.94$  mol/L ( $\approx 2.37 \times 10^{21}$  cm<sup>-3</sup>), where  $N_A$  is Avogadro's constant. The heuristic parameter, a = 0.75 nm, returns sheet charge density  $\sim 10^{14}$  cm<sup>-2</sup> in accordance with experimental results<sup>31</sup>. This simple assessment reveals that the portion of the channel strongly affected by the presence of ions is mainly in close proximity to the source and drain contacts, hence it justifies our choice to simulate a scaled version of the fabricated device. The  $Al_2O_3$  central gate in device D1 plays an insignificant role in the transport as the p-i-n junction is controlled by the high carrier density regions located within  $\sim 20$  nm of the contacts. This is why devices D1 and D2 produce similar characteristics. The stabilized ion doping profile forms a p-i-n junction in the polymer, and the resulting net ion distribution mirrors the same junction at the surface of the underlying semiconductor channel.

With the computed steady-state room-temperature ion distribution, Poisson's equation is then solved at 220 K under zero bias conditions using the net ion concentration as a fixed charge input. The accumulated anions (cations) near the drain (source) contact induce holes (electrons) in the underlying semiconductor layer. The equilibrium band diagram ( $V_{DS} = V_{BG} = 0$  V) in Fig. 4c clearly shows that a barrier is formed due to the ion-separation, which is confirmed by the free carrier accumulation near the two ends of the semiconductor up to degenerate levels as shown in Fig. 4d. The band diagram also shows a graded profile due to the exponential decay in free carrier density. The graded profile reduces the abruptness of the junction profile, which is limited by the channel length linking the two highly-doped regions. The asymmetry in the hole and electron profiles

**Figure 4.** COMSOL simulations of the EDL p–i–n junction in WSe $_2$ . (a) Simulated device structure, representing a scaled-version of the fabricated device consisting of a 100 nm WSe $_2$  channel and including source, drain, and backgate metal contacts, with PEO:CsClO $_4$  on the surface. PEO:CsClO $_4$  is modeled as a dielectric with  $\varepsilon_{PEO}$ =7 and a concentration of 1,000 mol/L of monovalent ions. A thin, 0.3 nm vacuum layer at the metal/semiconductor interfaces with PEO:CsClO $_4$  represents the effect of the Helmholtz layer. (b) Computed steady-state ion profile after a bias of  $V_D$ =  $-V_S$ =2 V is applied at the drain/source metal contacts. (c) Simulated band diagram along the channel length after the ion locking step at 220 K. (d) Charge density profile along the same cut showing an accumulation of image charges at the two ends of the channel, several orders of magnitude higher than that concentration in the middle of the channel.

is a consequence of the Schottky barriers at the metal contacts and the metal–oxide–semiconductor structure leading to a slight background accumulation of holes in the channel ( $\sim 10^{13}$  cm $^{-3}$ ). The carrier density slopes, 2.4 nm/decade for electrons and 4.1 nm/decade for holes, are highly abrupt relative to impurity dopant slopes, which are larger by a factor of two or more<sup>32</sup>.

#### **Conclusions**

Lateral EDL WSe $_2$  p–i–n junctions are demonstrated with substantially constant ideality factors over nearly 4 orders of magnitude using PEO:CsClO $_4$  to accumulate electrons and holes at the channel contacts. The high carrier densities at the contacts lead to a low resistance of the Schottky barriers and a series resistance which is dominated by the channel access resistance. The lower series resistance of these structures enables observation of the exponential dependence of the forward current over a wider range than previous studies. COMSOL simulations reveal that degenerate carrier densities are induced with abrupt carrier profiles in the vicinity of the contacts. The junction formation method of this paper using PEO:CsClO $_4$  and without a side gate achieves the highest currents with most ideal rectification properties reported to date in doping homojunctions in 2D materials.

In considering applications of this junction formation method, the requirement that the ions need to be positioned under bias and cooled to freeze them in place is undesirable and likely impractical. This freezing

requirement can be lifted if a polymer with a higher glass transition temperature is used, as discussed by Kinder<sup>33</sup>, or if the EDL-induced junction can be frozen in place at room temperature via crosslinking using a thermally triggered polymerization, as demonstrated by Liang<sup>34</sup>. Another way to eliminate the need to freeze the ions in place is to make the ion positioning bias and the operating bias the same; in this case cooling is not required as the fixed forward bias holds the ions in place. This is used, for example, in p-i-n junctions formed by this technique and used as light-emitters<sup>1920</sup>. However, if the terminal biases change, the ions will re-equilibrate and the emission characteristics can be expected to change accordingly.

Another question for this technology is scalability. There exist reports of carbon nanotubes (CNTs) with diameter of 2 nm coated and controllably electrolytically gated with PEO:LiClO<sub>4</sub><sup>35</sup>, showing that there is no intrinsic limit to coating cylindrical structures at the 2 nm scale. InAs nanowires with 50 nm diameter have also been successfully coated and gated with PEO:LiClO<sub>4</sub><sup>36</sup>. The electrolyte itself can also be scaled; ultrathin films of PEO have been spin coated down to 8 nm thickness, and exhibit well-behaved electrical properties<sup>37</sup>. However, to our knowledge there is no investigation of the viability of this doping method in highly-scaled VLSI (very large scale integration) geometries. Regarding the scaling of the TMD thickness, there are no fundamental impediments to the junction formation approach at the single monolayer thickness.

#### Methods

Devices D1 and D2 were fabricated in separate process runs. The fabrication began with backside evaporation of Ti/Au (5/100 nm) on the unpolished side of a  $p^+$  Si wafer. Next, 27 nm of Al<sub>2</sub>O<sub>3</sub> was deposited on the Si top surface by atomic layer deposition (ALD). Synthesized WSe<sub>2</sub> flakes (from 2D Semiconductors Co. with 99.9995% purity) were exfoliated on the oxide using dicing tape (Semiconductor Equipment Corp. P/N 18074). The flakes were patterned for source and drain using electron beam lithography (EBL) followed by metal deposition of Ti/Pd (0.8 nm/90 nm) and lift off. Device D1 omitted the gate process. Device D2 used a TiOPc adhesion layer following by the ALD process of Park and Fathipour<sup>38</sup>. Finally, the top gate contacts were patterned using EBL, followed by thermal metal deposition of 90 nm Pd and lift off. The oxide was then etched from the access regions of the FET in buffered HF, using the top gate as an etch mask. The device structures of this paper were fabricated in the same process run reported in reference<sup>18</sup>; in that paper the transistor and contact properties were analyzed using side-gates to position the ions. In this paper we focus on the formation of p-i-n junctions in transistor geometries without the use of auxiliary gates.

The solid-polymer electrolyte preparation and materials have been previously detailed <sup>18</sup>. In short, PEO (95,000 g/mol) and  $CsClO_4$  were dissolved in anhydrous acetonitrile at a concentration of 1 wt%, and an ether oxygen to  $Cs^+$  molar ratio of 168:1. The solution was drop-cast in an Ar-filled glove box, < 0.1 ppm  $O_2$  and  $H_2O$ , and then annealed for 3 min at 90 °C. Current–voltage measurements were made in a Cascade Microtech PLC50 vacuum probe station at  $1.2 \times 10^{-6}$  Torr. Devices that employ PEO: $CsClO_4$  are stable and give reproducible electrical characteristics under testing over months, as long as the applied voltages are kept within the electrochemical window of the electrolyte ( $\pm 4$  V) and wafers are stored between testing in an Ar or vacuum ambient to prevent water absorption of the PEO.

Received: 7 April 2020; Accepted: 10 July 2020

Published online: 30 July 2020

#### References

- 1. Fiori, G. et al. Electronics based on two-dimensional materials. Nat. Nanotechnol. 9, 768-779 (2014).

- 2. Pospischil, A., Furchi, M. M. & Mueller, T. Solar-energy conversion and light emission in an atomic monolayer *p-n* diode. *Nat. Nanotechnol.* **9**, 257–261 (2014).

- 3. Baugher, B. W. H., Churchill, H. O. H., Yang, Y. & Jarillo-Herrero, P. Optoelectronic devices based on electrically tunable *p*–*n* diodes in a monolayer dichalcogenide. *Nat. Nanotechnol.* **9**, 262–267 (2014).

- Ross, J. S. et al. Electrically tunable excitonic light-emitting diodes based on monolayer WSe<sub>2</sub> p-n junctions. Nat. Nanotechnol. 9, 268–272 (2014).

- 5. Sutar, S. et al. Reconfigurable p-n junction diodes and the photovoltaic effect in exfoliated MoS<sub>2</sub> films. Appl. Phys. Lett. 104, 122104 (2014).

- Lim, J. Y. et al. Homogeneous 2D MoTe<sub>2</sub> p-n junctions and CMOS inverters formed by atomic-layer-deposition-induced doping. Adv. Mater. 29, 1701798 (2017).

- Xu, H., Fathipour, S., Kinder, E. W., Seabaugh, A. C. & Fullerton-Shirey, S. K. Reconfigurable ion gating of 2H-MoTe<sub>2</sub> field-effect transistors using poly(ethylene oxide)-CsClO<sub>4</sub> solid polymer electrolyte. ACS Nano 9, 4900–4910 (2015).

- 8. Fathipour, S., Paletti, P., Fullerton-Shirey, S. & Seabaugh, A. C. Demonstration of electric double layer *p-i-n* junction in WSe<sub>2</sub>. 2016 Dev. Res. Conf. (DRC), 1–2.

- Kozawa, D. et al. Photodetection in p-n junctions formed by electrolyte-gated transistors of two-dimensional crystals. Appl. Phys. Lett. 109, 201107 (2016).

- 10. Zhang, Y. J., Ye, J. T., Yomogida, Y., Takenobu, T. & Iwasa, Y. Formation of a stable *p-n* junction in a liquid-gated MoS<sub>2</sub> ambipolar transistor. *Nano Lett.* **13**, 3023–3028 (2013).

- 11. Zhang, Y. J., Oka, T., Suzuki, R., Ye, J. T. & Iwasa, Y. Electrically switchable chiral light-emitting transistor. *Science* **344**, 725–728 (2014).

- 12. Choi, M. S. *et al.* Lateral MoS<sub>2</sub> *p-n* junction formed by chemical doping for use in high-performance optoelectronics. *ACS Nano* **8**, 9332–9340 (2014).

- 13. Li, H. M. *et al.* Ultimate thin vertical *p-n* junction composed of two-dimensional layered molybdenum disulfide. *Nat. Commun.* **6** 6564 (2015)

- 14. Xu, Z.-Q. et al. Atomically thin lateral p-n junction photodetector with large effective detection area. 2D Mater. 3, 041001 (2016).

- 15. Jin, Y. *et al.* A Van der Waals homojunction: ideal *p*-*n* diode behavior in MoSe<sub>2</sub>. *Adv. Mater.* **27**, 5534–5540 (2015).

- 16. Frisenda, R., Molina-Mendoza, A. J., Mueller, T., Castellanos-Gomez, A. & van der Zant, H. S. J. Atomically thin *p-n* junctions based on two-dimensional materials. *Chem. Soc. Rev.* 47, 3339–3358 (2018).

- Chuang, S. et al. Near-ideal electrical properties of InAs/WSe<sub>2</sub> van der Waals heterojunction diodes. Appl. Phys. Lett. 102, 242101 (2013).

- 18. Fathipour, S., Pandey, P., Fullerton-Shirey, S. & Seabaugh, A. C. Electric-double-layer doping of WSe<sub>2</sub> field-effect transistors using polyethylene-oxide cesium perchlorate. *J. Appl. Phys.* **120**, 234902 (2016).

- 19. Pei, Q., Yu, G., Zhang, C., Yang, Y. & Heeger, A. J. Polymer light-emitting electrochemical cells. Science 269, 1086–1088 (1995).

- 20. Gao, J., Li, Y., Yu, G. & Heeger, A. J. Polymer light-emitting electrochemical cells with frozen junctions. J. Appl. Phys. 86, 4594 (1999).

- 21. Edman, L., Summers, M. A., Buratto, S. K. & Heeger, A. J. Polymer light-emitting electrochemical cells: doping, luminescence, and mobility. *Phys. Rev. B.* **70**, 115212 (2004).

- 22. Ueda, A., Zhang, Y., Sano, N., Imamura, H. & Iwasa, Y. Ambipolar device simulation based on the drift-diffusion model in ion-gated transition metal dichalcogenide transistors. *npj Comput. Mater.* **6**, 144 (2020).

- 23. Paletti, P., Yue, R., Hinkle, C., Fullerton-Shirey, S. K. & Seabaugh, A. Two-dimensional electric-double-layer Esaki diode. npj 2D Mater. Appl. 3, 603–607 (2019).

- 24. Sylvia, S. S., Alam, K. & Lake, R. K. Uniform benchmarking of low-voltage van der Waals FETs. *IEEE J. Explor. Solid State Comput. Devices Circuits* 2, 28–35 (2016).

- 25. Sze, S. M. Physics of Semiconductor Devices 2nd edn, 89-92 (Wiley, New York, 1981).

- 26. Ibid. pp. 88-89.

- 27. Ibid. p. 281, Eq. (82).

- 28. Padovani, F. A. & Stratton, R. Field and thermionic-field emission in Schottky barriers. Solid State Electron. 9, 695-707 (1966).

- 29. Takagi, S., Toriumi, A., Iwase, M. & Tango, H. On the universality of inversion layer mobility in Si MOSFET's: part I—effects of substrate impurity concentration. *IEEE Trans. Electron Devices* 41, 2357–2362 (1994).

- 30. Kilic, M. S., Bazant, M. Z. & Ajiri, A. Steric effects in the dynamics of electrolytes at large applied voltages. II. Modified Poisson–Nernst–Planck equations. *Phys. Rev. E* 75, 021503 (2007).

- 31. Ueno, K. et al. Field-induced superconductivity in electric double layer transistors. J. Phys. Soc. Jpn. 83, 032001 (2014).

- 32. Kujirai, H., Murakami, E. & Kimura, S. Ultra-shallow and abrupt boron profiles in Si by δ-doping technique. *Jpn. J. Appl. Phys.* **34**, 782–786 (1995).

- 33. Kinder, E. W., Fuller, A., Lin, Y.-C., Robinson, J. A. & Fullerton-Shirey, S. K. Increasing the room-temperature electric double layer retention time in two-dimensional crystal FETs. ACS Appl. Mater. Interfaces 9, 25006–25013 (2017).

- 34. Liang, J., Xu, K., Arora, S., Laaser, J. E. & Fullerton-Shirey, S. K. Ion-locking in solid polymer electrolytes for reconfigurable gateless lateral graphene p–n junctions. *Materials* 13, 1089 (2020).

- 35. Lu, C., Fu, Q., Huang, S. & Liu, J. Polymer electrolyte-gated carbon nanotube field-effect transistor. Nano Lett. 4, 623-627 (2004).

- 36. Carrad, D. J. et al. Electron-beam patterning of polymer electrolyte films to make multiple nanoscale gates for nanowire transistors. Nano Lett. 14, 94–100 (2014).

- 37. Gonzalez-Serrano, K. A. & Seabaugh, A. C. Electrical properties of spin-coated polyethylene oxide capacitors as thin as 8 nm. 2020 Electronic Materials Conf (2020).

- 38. Park, J. H. *et al.* Atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> on WSe<sub>2</sub> functionalized by titanyl phthalocyanine. *ACS Nano* **10**, 6888–6896 (2016).

### **Acknowledgements**

This work was supported in part by the Center for Low Energy Systems Technology (LEAST), a STARnet Semi-conductor Research Corporation program sponsored by MARCO and DARPA.

## **Competing interests**

The authors declare no competing interests.

#### Additional information

Correspondence and requests for materials should be addressed to A.S.

Reprints and permissions information is available at www.nature.com/reprints.

**Publisher's note** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2020