Abstract

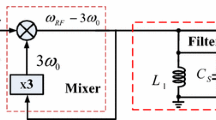

This paper aims to design a low-power and high-frequency divider in an integrated CMOS phase-locked loop. The proposed frequency divider is a two-step divider composed of an injection-locked frequency divider (ILFD) and a current-mode logic (CML) frequency divider. The ILFD has a structure similar to an LC cross-coupled oscillator to adjust the frequency alignment between the oscillator and the ILFD. The LC cross-coupled oscillator operates at 50 GHz, and the ILFD is supposed to provide a divide-by-2 (/2) operation. The CML frequency divider, which is used as the second-stage divider, is applied with an inductive peaking structure for a wide band with low power consumption. The proposed two-step frequency divider is designed with a 0.18 µm CMOS process. By varying the numbers of the ILFD and the CML divider, the characteristics of power consumption are also studied. Post-layout simulation shows that the /2 ILFD and the /128 CML frequency divider operate at an input frequency of 50 GHz, with power consumption of 37.8 mW, and results indicate a low-power two-step divider at high frequency.

Similar content being viewed by others

References

Mo, Y., Skafidas, E., Evans, R., & Mareels, I. (2008). A 40 Ghz power efficient static CML frequency divider in 0.13-µm CMOS technology for high speed millimeter-wave wireless systems. In ICCSC 2008 conference (pp. 812–815).

Plouchart, J. O., Kim, J., Karam, V., Trzcinski, R., & Gross, J. (2006). Performance variation of a 66 GHz static CML divider in a 90 nm SOI CMOS. In ISSCC Digest of Technical papers (pp. 526–527).

Cao, C., & Kenneth, K. O. (2005). A power efficient 26-GHz 32:1 static frequency divider in 130-nm bulk CMOS. IEEE Microwave and Wireless Components Letters, 15(11), 721–723.

Park, J., Ahn, S., Jeong, H., & Kim, N. (2014). High-speed CMOS frequency divider with inductive peaking technique. Transactions on Electrical and Electronics Materials, 15(6), 309–314.

Fazeel, H. S., Raghavan, L., Srinivasaraman, C., & Jain, M. (2009). Reduction of current mismatch in PLL charge pump. Proceedings of IEEE International Symposium on ISVLSI, 2009, 7–12.

Karimi-Ghartemani, M., Khajehoddin, S. A., Jain, P. K., & Bakhshai, A. (2012). Deviation and design of in-loop filters in phase-locked loop systems. IEEE Transactions on Instrumentation and Measurement, 61(4), 930–940.

Park, J., Choi, H., & Kim, N. (2015). Two-stage feedback-looped charge-pump for spur-reduction in CMOS PLL. Analog Integrated Circuits and Signal Processing, 83, 143–148.

Tong, H., Cheng, S., Karsilayan, A. I., & Martinez, J. S. (2007). An injection-locked frequency divider with multiple highly nonlinear injection stages and large division ratios. IEEE Journal of Solid-State Circuits, 42(2), 313–321.

Jalalifar, M., & Byun, G. (2014). A K-band divide-by-five injection-locked frequency divider using a near-threshold VCO. IEEE Microwave and Wireless Components Letters, 24(12), 881–883.

Buonomo, A., Schiavo, A., Awan, M., Asghar, M., & Kenndy, M. (2011). A CMOS injection-locked frequency divider optimized for divide-by-two and divide-by-three operation. IEEE Transactions on Circuits and Systems I, 60(12), 3126–3135.

Tiebout, M. (2004). A CMOS direct injection-locked oscillator topology as high-frequency low-power frequency divider. IEEE Journal of Solid-State Circuits, 39(7), 1170–1174.

Ku, Y., & Cho, S. (2008). An optimum current mirror ratio for low phase noise LC-VCO. IEEE Microwave and Wireless Components Letters, 18(12), 881–883.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Hong, Jp., Ann, SH. & Kim, N. Low-power CMOS injection-locked and current-mode logic frequency dividers in a 50 GHz LC cross-coupled oscillator. Analog Integr Circ Sig Process 86, 377–384 (2016). https://doi.org/10.1007/s10470-015-0687-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-015-0687-8