# **Chapter 5 Evaluation and Validation**

During the design procedure, we have to check repeatedly whether or not the system under design is likely to perform its function and to satisfy all relevant design objectives. This is the purpose of validations and evaluations which must be performed during the design process. This chapter starts with a presentation of techniques for the evaluation of (partial) designs with respect to objectives. In particular, we consider (worst case) execution time, quality of results, thermal behavior, and dependability as objectives. We provide an introduction into fundamental techniques for computing the worst case execution time. Examples of energy models will be presented in order to demonstrate the need for an adjustment of the level of model details to the particular application at hand. Thermal modeling is reduced to the problem of equivalent electrical modeling. With respect to dependability, an introduction to statistical models of reliability as well as an introduction to fault trees are included. As a means for relating results for the different objectives against each other, we introduce the concept of Pareto optimality. This chapter closes with hints regarding validation techniques, including simulation, rapid prototyping, and formal verification.

#### 5.1 Introduction

## 5.1.1 Scope

Specification, hardware platforms, and system software provide us with the basic ingredients which we need for designing embedded systems. During the design process, we must validate and evaluate designs rather frequently. These activities can be defined as follows:

The original version of this chapter was revised: Caption for the second part of Fig. 5.25 has been updated. A correction to this chapter is available at https://doi.org/10.1007/978-3-030-60910-8\_9

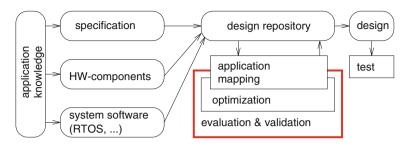

Fig. 5.1 Context of the current chapter

**Definition 5.1 Evaluation** is the process of computing quantitative information of some key characteristics (or "objectives") of a certain (possibly partial) design.

**Definition 5.2 Validation** is the process of checking whether or not a certain (possibly partial) design is appropriate for its purpose, meets all constraints, and will perform as expected.

**Definition 5.3** Validation with mathematical rigor is called (**formal**) **verification**.

Validation and evaluation are required at various phases during the design procedure (see Fig. 5.1). Validation and design should be intertwined and not be considered as two completely independent activities. Validation and evaluation, even though different from each other, are very much linked. Due to their impact, we will describe validation and evaluation before we talk about design steps.

# 5.1.2 Multi-Objective Optimization

Design evaluations will, in general, lead to a characterization of the design by several criteria, such as execution time, energy consumption, quality of results, thermal behavior, and dependability. Merging all these criteria into a single objective function (e.g., by using a weighted average) is usually not advisable, as this would hide some of the essential characteristics of designs. Rather, it is recommended to return to the designer a set of designs among which the designer can then select an appropriate design. Such a set should, however, only contain "reasonable" designs. Finding such sets of designs is the purpose of **multi-objective optimization techniques**.

In order to perform multi-objective optimization, we do consider an m-dimensional space X of possible solutions of the optimization problem. These dimensions could, for example, reflect the number of processors, the sizes of memories, as well as the number and types of buses. For this space X, we define an n-dimensional

5.1 Introduction 241

function

$$f(x) = (f_1(x), \dots, f_n(x))$$

where  $x \in X$

which evaluates designs with respect to several criteria or objectives (e.g., cost and performance). Let F be the n-dimensional space of values of these objectives (the so-called objective space). Suppose that, for each of the objectives, some total order < and the corresponding  $\le$  order are defined. In the following, we assume that the goal is to **minimize** our objectives.

**Definition 5.4** Vector  $u = (u_1, ..., u_n) \in F$  **dominates** vector  $v = (v_1, ..., v_n) \in F$  iff u is "better" than v with respect to at least one objective and not worse than v with respect to all other objectives:

$$\exists j \in \{1, ..., n\} : u_j < v_j \tag{5.2}$$

**Definition 5.5** Vector  $u \in F$  is called **indifferent** with respect to vector  $v \in F$  iff neither u dominates v nor v dominates u.

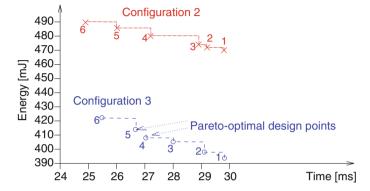

**Definition 5.6** A design  $x \in X$  is called **Pareto optimal** with respect to X iff there is no design  $y \in X$  such that u = f(x) is dominated by v = f(y).

The previous definition defines Pareto optimality in the solution space. The next definition serves the same purpose in the objective space.

**Definition 5.7** Let  $S \subseteq F$  be a subset of vectors in the objective space.  $v \in F$  is called a **non-dominated solution** with respect to S iff v is not dominated by any element  $\in S$ . v is called Pareto optimal iff v is non-dominated with respect to all solutions F.

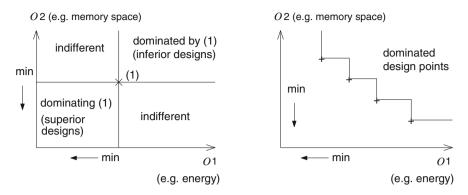

Figure 5.2 highlights the different areas in an objective space with objectives O1 and O2, relative to design point (1).

The upper right area corresponds to designs that would be dominated by design (1), since they would be "worse" with respect to both objectives. Designs in the lower left rectangle would dominate design (1), since they would be "better" with respect to both objectives. Designs in the upper left and the lower right area are indifferent: they are "better" with respect to one objective and "worse" with respect to the other. Figure 5.2 (right) shows a set of Pareto points, i.e., the so-called Pareto front.

**Definition 5.8 Design space exploration** (DSE) based on Pareto points is the process of finding and returning a set of Pareto optimal solutions to the designer, enabling the designer to select the most appropriate implementation.

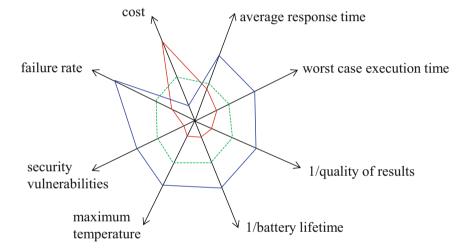

In order to visualize objectives in multiple dimensions, so-called radar charts, spider charts, or Kiviat diagrams can be used [579]. They are extensions of the type of diagram which we have used in Fig. 2.74 to multiple dimensions.

Fig. 5.2 Pareto optimality: left, Pareto point; right, Pareto front

Fig. 5.3 Kiviat diagram: top (red), mid-range (green, dashed), and entry-level (blue) models

Example 5.1 As shown in Fig. 5.3, we can compare several designs (e.g., of mobile phones) according to objectives similar to the ones presented in the next subsection. Minimization of all objectives is assumed. The top model minimizes most objectives, except for costs. For the entry level model, it is the other way around.  $\nabla$

## 5.1.3 Relevant Objectives

For servers and PCs, the average performance plays a dominating role. For embedded and cyber-physical systems, multiple objectives need to be considered. The following list explains if and where this objective is discussed in this book:

- 1. **Average performance:** Some comments on this objective will be made in Sect. 5.2. This objective is frequently computed from simulations, which will be introduced in Sect. 5.7.

- 2. **Worst case performance/real-time behavior:** Some fundamental techniques for computing the worst case execution time (WCET) will be presented in Sect. 5.2.2. This will be complemented by an introduction to real-time calculus in Sect. 5.2.3.

- 3. **Quality metrics:** Quality metrics will be presented in Sect. 5.3. In addition, transformations between number systems are discussed in Sect. 7.1.5.

- 4. **Energy/power consumption:** A brief overview of techniques for evaluating this objective will be presented in Sect. 5.4.

- 5. **Thermal models:** An introduction to this topic will be presented in Sect. 5.5.

- 6. **Dependability:** Dependability is the topic of Sect. 5.6, with subsections on safety, security, and reliability.

- 7. **Electromagnetic compatibility:** This objective will not be considered here.

- 8. **Testability:** Costs for testing systems can be very large, sometimes larger even than production costs. Hence, testability should be considered as well, preferably already during the design. Testability will be discussed in Chap. 8.

- 9. Cost: Cost in terms of silicon area or real money will not be considered here.

- 10. Weight, robustness, usability, extendability, and environmental friendliness: These objectives will also not be considered.

There are more objectives than the ones listed above. For example, we could use standards for the evaluation of software quality, like standards ISO/IEC 25022 [258], ISO/IEC 25023 [259], and ISO/EIC 25024 [257]. The next section presents some approaches for performance evaluation, focusing on the worst case performance.

#### **5.2** Performance Evaluation

Performance evaluation aims at predicting the performance of systems. This is a major challenge (especially for cyber-physical systems) since we might need worst case information, rather than just average case information. Such information is necessary in order to guarantee real-time constraints.

# 5.2.1 Early Phases

Two different classes of techniques have been proposed for obtaining performance information already during early design phases:

• Estimated cost and performance values: Quite a number of estimators have been developed for this purpose. Examples include the work by Jha and Dutt

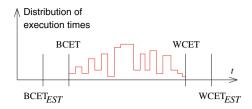

**Fig. 5.4** WCET-related terms

[274] for hardware and Jain et al. [266] and Franke [167] for software. Generating sufficiently precise estimates requires considerable efforts.

• Accurate cost and performance values: We can also use the real binary software code on a close-to-real hardware platform. This is only possible if interfaces to compilers exist. This method can be more precise than the previous one but may be significantly (and sometimes prohibitively) more time-consuming.

In order to obtain sufficiently precise information, communication needs to be considered as well. Unfortunately, it is typically difficult to compute communication cost already during early design phases.

Formal performance evaluation techniques have been proposed by many researchers. For embedded systems, the work of Thiele et al., Henia and Ernst et al., and Wilhelm et al. is particularly relevant (see, e.g., [210, 536] and [587]). These techniques require some knowledge of architectures. They are less appropriate for early design phases, but some of them can be used without knowing all details about target architectures. These approaches model real, physical time.

#### 5.2.2 WCET Estimation

Scheduling of tasks requires knowledge about the duration of task executions, especially if meeting time constraints has to be guaranteed, as in real-time (RT) systems. The **worst case execution time** (WCET) is the basis for most scheduling algorithms. Some definitions related to the WCET are shown in Fig. 5.4.

**Definition 5.9** The worst case execution time (WCET) is the largest execution time of a program for any input and any initial execution state.

Unfortunately, the WCET is extremely difficult to compute. In general, it is undecidable whether or not the WCET is finite. This is obvious from the fact that it is undecidable whether or not a program terminates. Hence, the WCET can only be computed for certain programs/tasks. For example, for programs without recursion, without while loops, and with loops having statically known iteration counts, decidability is not an issue. But even with such restrictions, it is usually practically impossible to compute the WCET exactly. The effect of modern processor architectures' pipelines with their different kinds of hazards and memory hierarchies with limited predictability of hit rates is difficult to precisely predict

at design time. Computing the WCET for systems containing interrupts, virtual memory, and multiple processors is an even greater challenge. As a result, we must be happy if we are able to compute good **upper bounds** on the WCET.

Such upper bounds are usually called **estimated worst case execution times**, or WCET<sub>EST</sub>. Such bounds should have at least two properties:

- 1. The bounds should be safe (WCET<sub>EST</sub> > WCET).

- 2. The bounds should be tight (WCET<sub>EST</sub>-WCET  $\ll$  WCET).

Note that the term "estimated" does not mean that the resulting times are unsafe. Sometimes, architectural features which reduce the average execution time but cannot guarantee to reduce WCET<sub>EST</sub> are completely omitted from the real-time designs (see p. 154). Computing tight upper bounds on the execution time may still be difficult. The architectural features described above also present problems for the computation of WCET<sub>EST</sub>. The computation of such bounds is extremely difficult for multi-cores. In fact, potential conflicts might even cause multi-cores to have larger worst case bounds than the corresponding single cores.

**Definition 5.10** The **best-case execution time** (BCET) is the smallest execution time of a program, considering all feasible inputs and initial states. The BCET $_{EST}$  is a safe and tight lower bound on the execution time.

Computing tight bounds from a program written in a high-level language such as C without any knowledge of the generated assembly code and the underlying architectural platform is impossible. Therefore, a safe analysis must start from real machine code. Any other approach would lead to unsafe results.

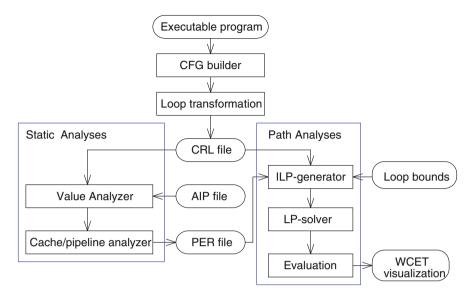

We will study WCET estimation more closely, using a description of the tool aiT by R. Wilhelm [587]. The architecture of aiT is shown in Fig. 5.5.

Consistent with our remark about the problems with high-level code, aiT starts from an executable object file comprising the code to be analyzed. From this code, a control flow graph (CFG) is extracted. Next, loop transformations are applied. These include transformations between loops and recursive function calls as well as virtual loop unrolling. This unrolling is called "virtual" since it is performed internally, without actually modifying the code to be executed. Results are represented in the CRL (control flow representation language) format. The next phase employs different static analyses. Static analyses read the AIP-file comprising designer's annotations. These annotations contain information which is difficult or impossible to extract automatically from the program (e.g., bounds of complex loops). Static analyses include value analysis, cache analysis, and pipeline analyses.

A **value analysis** computes enclosing intervals for possible values in registers and local variables. The resulting information can be used for control flow analysis and for data cache analysis. Frequently, values such as addresses are precisely known (especially for "clean" code), and this helps in predicting accesses to memories.

Fig. 5.5 Architecture of the aiT timing analysis tool

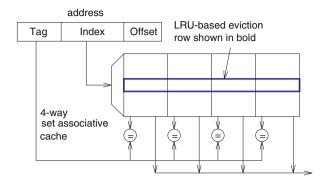

The next step is **cache** and **pipeline analysis**. We will present a few details about the cache analysis. Suppose using an n-way set associative cache (see Fig. 5.6). We consider that part of the cache (the **row**) corresponding to a certain index (shown in bold and blue in Fig. 5.6). We assume that eviction from the row is controlled by the least recently used (LRU) strategy. This means that among all references for a particular index, the last n referenced memory blocks are stored in the row. We assume that the necessary LRU management hardware is available for each index and that each index is handled independently of other indexes. Under this assumption, all evictions for a particular index are completely independent of decisions for other indexes. This independence is extremely important, since it allows us to consider each of the indexes independently.

Let us now consider a row and a particular index. Suppose that we have information about potential entries for each of the cache ways (columns). What will happen in case of an access to a particular index? First of all, let us consider the case of an access to a variable e known to be in the cache. After that access, that variable is known to be the youngest (see Fig. 5.7). Entries on the left are assumed to be younger than the ones on the right.

Now, assume that we have an access to some variable (say c) which is not yet in the cache. This access will remove the oldest entry from the cache (see Fig. 5.8).

<sup>&</sup>lt;sup>1</sup>We assume that students are familiar with concepts of caches.

<sup>&</sup>lt;sup>2</sup>Unfortunately, this strategy is typically not available for processors.

**Fig. 5.6** Set associative cache (for n = 4)

Fig. 5.7 Access to variable e makes it the youngest

Fig. 5.8 Access to variable c causes eviction of f

Furthermore, consider control flow joins. What do we know about the content of the partial cache after the join?

We must distinguish between *may*- and *must*-information and the corresponding analysis. Must-analysis reveals the entries which **must** be in the cache. This information is useful for computing the WCET. May-analysis identifies the entries which **may** be in the cache. This information is typically used to conclude that certain information will definitely not be in the cache. This knowledge is then exploited during the computation of the BCET.

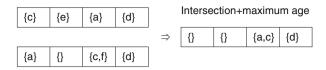

As an example of must- and may-analysis, we consider must information at control flow joins. Figure 5.9 shows the corresponding situation. In Fig. 5.9, memory object c is assumed to be the youngest object for one path to the join and a is assumed to be the youngest object for the other path. The age of the other entries is defined accordingly. What do we know about the "worst" case after the join? A certain entry is guaranteed to be in the cache only if it is guaranteed to be in the cache for both paths. This means that the **intersection** of the memory objects defines the result of the must-analysis after the join. As a worst case, we must assume the **maximum of the ages** along the two paths. Figure 5.9 shows the result. This analysis uses sets of entries for each cache way.

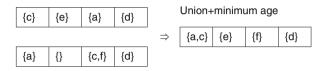

Now, consider may-analysis for control flow joins. Figure 5.10 depicts the situation. Some object being in the cache on either of the two paths to the join *may* be in the cache after the join. Hence, the set of objects which may be in the cache

Fig. 5.9 Must-analysis at program joins for LRU caches

Fig. 5.10 May-analysis at program joins for LRU caches

after the join consists of the **union** of the objects that were in the cache before the join. As a best case, we use the **minimum of the ages** before the join. Figure 5.10 shows the result.

Static analyses also comprise pipeline analysis. Pipeline analysis has to compute safe bounds on the number of cycles required to execute code in the machine pipeline. Details of pipeline analysis are explained by Hahn et al. [196] and Thesing [534]. The result of static analyses consists of bounds on the execution times for each of the basic blocks of a program. Results are written to the PER-file shown in Fig. 5.5.

aiT's next phase exploits these bounds to derive WCET<sub>EST</sub> values for the entire program, using an **integer linear programming** (ILP) model (see p. 393), comprising two types of information:

• The objective function: In our application of ILP modeling, this function represents the overall execution time. This time is calculated as

$$WCET_{EST} = \sum_{\text{basic blocks}} e_i * f_i$$

(5.3)

where  $e_i$  is the worst case execution time of basic block i (as computed during static analysis) and  $f_i$  its worst case execution count. Only some of these counts can be determined automatically, and additional designer-provided information, e.g., about loop bounds, may be required.

• Linear constraints: These reflect the structure of the control flow graph.

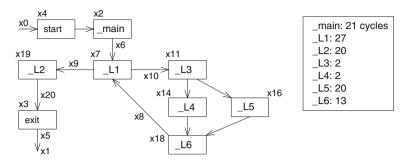

Fig. 5.11 Sample program: left: extended control flow graph; right: WCET<sub>EST</sub> of basic blocks

#### Example 5.2 Let us consider the simple code shown next:

Figure 5.11 (left) shows the control flow graph (CFG) corresponding to this small program. This graph is extended by additional start and exit nodes. Node \_L1 reflects the for-testing, \_L3 the if-testing, \_L4 and \_L5 the two cases of the if-statement, and \_L6 its join operation. Variables x0 to x20 denote the number of executions of the blocks and the number of transitions between blocks. For example, we are transitioning from node main into node \_L1 x6 times and are executing the target node x7 times. We assume that the analysis of the WCET for each of the basic blocks has resulted in the list shown on the right of Fig. 5.11. The following is a partial list of the ILP constraints:

```

01: 21 x2 + 27 x7 + 2 x11 + 2 x14 + 20 x16 + 13 x18 + 20 x19; /*objective*/

02: x7 - x8 - x6 = 0;

/* Constraint for flow entering CFG node _L1 */

03: x7 - x9 - x10 = 0;

/* Constraint for flow leaving CFG node _L1 */

04: x7 - 101 x9 >= 0;

/* Constraint for lower loop bound of _L1 */

05: x7 - 101 x9 <= 0; ...

/* Constraint for upper loop bound of _L1 */

06: x0 - x4 = 0:

/* CFG Start Constraint */

07: x2 - x4 = 0;

/* Constraint for flow entering function _main */

08: x2 - x6 = 0;

/* Constraint for flow leaving CFG node _main */

09: ...

```

Line 01 contains the cost function. All other lines model constraints reflecting the structure of the graph. Consider, for example, node  $\_L1$ . Constraints for this node are shown in lines 02 and 03. The number of times that we are branching into the node (x6+x8) is equal to its number of executions (x7). The number of times that we are leaving from the node (x9+x10) is also equal to its number of executions. Lines 04 and 05 reflect the number of loop iterations. This number is taken from the pragma in the code. Line 06 describes the fact that node start is executed exactly as many times as we are branching into the code. The other lines are reflecting the structure in a similar way.

The ILP problem can be solved with some standard ILP solver. Maximizing the objective function yields a safe upper bound on the WCET.

This technique for modeling execution time is called **implicit path enumeration** (IPET) [343], since the problem of enumerating the potentially large number of execution paths is avoided.

aiT visualizes the results as annotated control flow graphs. The designer could optimize the system under design by exploiting these graphs. Due to the presented approach, aiT has limitations: preemption by other processes, interrupts, input/output, and direct memory transfers (DMA) are not supported.

Only few approaches exist for the WCET analysis of multi-cores [264, 265, 286]. New probabilistic approaches [2] aim at complementing available methods. They are usually based on extreme value theory [123].

#### 5.2.3 Real-Time Calculus

WCET estimates allow us to predict the execution of some algorithm for a single input event. However, the overall goal is more comprehensive. Overall, we should make sure that our hardware platform is capable of processing streams of events in a timely manner (which may be important for some parts of the Internet of Things).

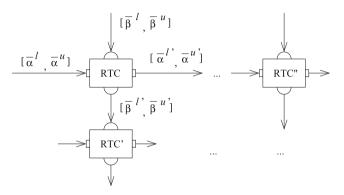

This can be checked with Thiele's **real-time calculus** (**RTC**). This calculus (**RTC**) is based on the description of the rate of incoming events.<sup>3</sup> This description also includes fluctuations of this rate. Toward this end, the timing characteristics of a sequence (or stream) of events are represented by a tuple of *arrival curves*:

$$\overline{\alpha}^{u}(\Delta), \overline{\alpha}^{l}(\Delta) \in \mathbb{R} \ge 0, \Delta \in \mathbb{R} \ge 0$$

These curves represent the maximal resp. the minimal number of events arriving within a time interval of length  $\Delta$ . There are at most  $\overline{\alpha}^{u}(\Delta)$  and at least  $\overline{\alpha}^{l}(\Delta)$

<sup>&</sup>lt;sup>3</sup>Our presentation of the real-time calculus is based on Thiele's presentation in the book edited by Zurawski [536]. Resulting considerations at the system level have been called *modular performance analysis* (MPA).

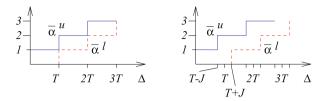

Fig. 5.12 Arrival curves: left: periodic stream; right: periodic stream with jitter J

events arriving within the time interval  $(t, t + \Delta)$  for all  $t \ge 0$ . Figure 5.12 shows the number of possibly arriving events for some possible models of arriving events. For example, in the case of periodic event streams with period T, there is a maximum of a single event happening in time interval (0, T). Similarly, there is an upper bound of two events within time interval (T, 2T). Now, let us consider the lower bound for time interval (0, T). There is possibly not a single event in this interval. Hence, the bound is zero. For time interval (T, 2T), there has to be at least one event. Therefore, the bound is one. So, for  $\Delta = 0.5T$ , there will be at least zero and at most one incoming event (see Fig. 5.12 (left)). In the case of periodic event streams with jitter J, these curves are shifted by this amount (see Fig. 5.12 (right)). The upper bound is shifted to the left; the lower bound is shifted to the right. The jitter is assumed not to be accumulating.

We are using bars on top of symbols (like  $\overline{\alpha}$ ) for all entities referring to incoming events.

Available computational and communication service capacity can be described by *service functions*:

$$\beta^{u}(\Delta), \beta^{l}(\Delta) \in \mathbb{R} \ge 0, \Delta \in \mathbb{R} \ge 0$$

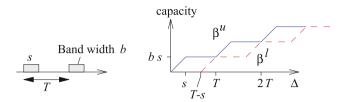

These functions allow us to model situations in which the available service capacity is fluctuating. Figure 5.13 shows the communication capacity of some *time division multiple access* (TDMA) bus (see p. 176). Allocation is done periodically with a period of T. Bus arbitration allocates this bus during a time window s time units long. During this window, the bus achieves a bandwidth of b. The upper bound is obtained if the bus is allocated exactly at the time we are starting our observation. The transferred amount is then increasing linearly. The lower bound is obtained if the bus was just deallocated when we started our observation of length  $\Delta$ . Then we must wait T-s time units until the bus gets allocated again.

Separate methods are required to determine  $\overline{\alpha}$  and  $\beta$  for streams of ("external") events arriving at the system to be modeled. Their computation is not part of RTC. In contrast, bounds for events generated within the system are derived by the calculus (see below).

<sup>&</sup>lt;sup>4</sup>We leave out the subtle discussion of discontinuities at  $\Delta = n * T$ .

Fig. 5.13 Service functions for a TDMA bus

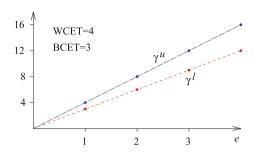

Up till now, there is no information about the **workload** required by each of the incoming events. This workload is represented by additional functions  $\gamma^u(e), \gamma^l(e) \in \mathbb{R} \geq 0$  for each sequence e of incoming events. This information can be derived from bounds on the execution time of code required for each of the events. Figure 5.14 shows an example of such functions. This example is based on the assumption that between three and four time units are required for processing a single event. Accordingly, the workload for a single event varies between three and four time units, the work load for two events varies between six and eight time units, etc. The dashed lines are not part of the function, since it is defined only for an integer number of events. The work load resulting from an incoming stream of events can now be easily computed. Upper and lower bounds are characterized by the functions

$$\alpha^{u}(\Delta) = \gamma^{u}(\overline{\alpha}^{u}(\Delta))$$

and (5.4)

$$\alpha^{l}(\Delta) = \gamma^{l}(\overline{\alpha}^{l}(\Delta)) \tag{5.5}$$

There should be enough computational or communication capacity to handle this workload. The number of events which can be processed with the available computational capacity can be computed as

$$\overline{\beta}^{u}(\Delta) = (\gamma^{l})^{-1}(\beta^{u}(\Delta)) \text{ and}$$

(5.6)

$$\overline{\beta}^{l}(\Delta) = (\gamma^{u})^{-1}(\beta^{l}(\Delta)) \tag{5.7}$$

Equations (5.6) and (5.7) use the inverse of functions  $\gamma^u$  and  $\gamma^l$  to convert bounds on the available capacity (measured in real time units) into bounds measured in terms of the number of events that can be processed.

Based on this information, it is possible to derive the properties of outgoing streams of events from incoming streams of events. Suppose the incoming stream is characterized by bounds  $[\overline{\alpha}^{\ l}, \overline{\alpha}^{\ u}]$ . We can then compute characteristics of the outgoing streams such as the corresponding bounds  $[\overline{\alpha}^{\ l'}, \overline{\alpha}^{\ u'}]$  of the outgoing stream of events and the remaining service capacity, available for other tasks. This remaining capacity is derived by transforming *service curves*  $[\overline{\beta}^{\ l'}, \overline{\beta}^{\ u'}]$  (see Fig. 5.15). This remaining service capacity can be employed for lower-priority tasks to be executed on the same processor.

**Fig. 5.14** Workload characterization (WCET<sub>EST</sub> may be used instead of WCET)

Fig. 5.15 Transformation of event stream and service capacities by real-time components

According to Thiele et al., outgoing streams and remaining service capacities are bounded by the following functions [536]:

$$\overline{\alpha}^{u'} = [(\overline{\alpha}^u \underline{\otimes} \overline{\beta}^u) \overline{\oslash} \overline{\beta}^l] \wedge \overline{\beta}^u$$

(5.8)

$$\overline{\alpha}^{l'} = [(\overline{\alpha}^l \, \overline{\otimes} \, \overline{\beta}^u) \, \underline{\otimes} \, \overline{\beta}^l] \wedge \overline{\beta}^l \tag{5.9}$$

$$\overline{\beta}^{u'} = (\overline{\beta}^u - \overline{\alpha}^l) \otimes 0 \tag{5.10}$$

$$\overline{\beta}^{l'} = (\overline{\beta}^l - \overline{\alpha}^u) \, \overline{\otimes} \, 0 \tag{5.11}$$

Operators used in these equations are defined as follows:

$$(f \underline{\otimes} g)(t) = \inf_{0 < u < t} \{ f(t - u) + g(u) \}$$

(5.12)

$$(f \overline{\otimes} g)(t) = \sup_{0 \le u \le t} \{ f(t - u) + g(u) \}$$

(5.13)

$$(f \overline{\oslash} g)(t) = \sup_{u \ge 0} \{ f(t+u) - g(u) \}$$

(5.14)

$$(f \underline{\oslash} g)(t) = \inf_{u \ge 0} \{ f(t+u) - g(u) \}$$

(5.15)

∧ denotes the minimum operator.

In essence, these equations characterize outgoing streams and capacities. These equations have been adopted from communications theory. Proofs regarding these equations are provided by Network Calculus [327]. The easiest way of using these equations is to download a MATLAB® toolbox [561].

The same theory also allows to compute the delay caused by the real-time components as well as the size of the buffer required to temporarily store incoming/outgoing events. This way, performance and other characteristics of the system can be computed from information about the components.

A second performance analysis method has been proposed by Henia and Ernst et al. In this so-called SymTA/S approach [210], the different curves in Thiele's approach are replaced by standard models of event streams such as periodic event streams, periodic event streams with random jitter, and periodic event streams with bursts. SymTA/S explicitly supports the combination and integration of different kinds of analysis techniques known from real-time research.

## **5.3** Quality Metrics

## 5.3.1 Approximate Computing

Sometimes, computing the best possible output of some algorithm requires a significant amount of resources (in terms of computing time, energy, thermal headroom, etc.). For some applications, the best possible output is not actually needed, since minor degradations will possibly not even be recognized by users. This can be exploited in a resource-constrained environment in order to trade off the quality of the output against needed resources. A certain deviation of the actual output from the best possible output is accepted, for example, for lossy audio, video, and image encoding. This leads us to consider **approximate computing**.

**Definition 5.11** Computing which tolerates a certain deviation of generated output of some algorithm from the best possible result is called **approximate computing** [397].

With approximate computing, it is necessary to consider the quality of the generated output as one of the objectives. Unfortunately, it is not easy to evaluate the quality of some generated result, and several metrics can be used.

# 5.3.2 Simple Criteria of Quality

Some simple metrics can be applied whenever the true (or the best possible) output is known. Suppose that  $x_1, \ldots, x_n$  are n samples of some signal x in discrete time.

Furthermore, suppose that instead of the real (or the best possible) values  $x_1, \ldots, x_n$  we measure or compute approximate values  $y_1, \ldots, y_n$ .

Then, our first metric, the mean-squared error (MSE), is defined as follows:

#### **Definition 5.12** The **mean-squared error** (MSE) is defined as

$$MSE(x, y) = \frac{1}{n} \sum_{i=1}^{n} (x_i - y_i)^2$$

(5.16)

The second metric is the root-mean-squared error.

#### **Definition 5.13** The **root-mean-squared error** (RMSE) is defined as

$$RMSE(x, y) = \sqrt{\frac{1}{n} \sum_{i=1}^{n} (x_i - y_i)^2}$$

(5.17)

RMSE has the same dimension as the difference between the actual and the real value, but it should not be confused with the "average error" which is defined next:

#### **Definition 5.14** The **mean absolute error** (MAE) is defined as

$$MAE(x, y) = \frac{1}{n} \sum_{i=1}^{n} |x_i - y_i|$$

(5.18)

For identical deviations of the measured signal *y* from real values *x*, the MAE is equal to the RMSE. However, the RMSE emphasizes large deviations between real and measured values (so-called outliers).

The signal-to-noise ratio (SNR) was already defined on p. 142. Next, we define the peak signal-to-noise ratio, which is similar to the SNR. Let x be a signal,  $x_{max}$  its maximum, and y its noisy approximation.

#### **Definition 5.15** The **peak signal-to-noise ratio** (PSNR) is defined as

$$PSNR(x, y) = 10 \log_{10} \left( \frac{x_{max}^2}{MSE(x, y)} \right)$$

(5.19)

$$=20\log_{10}\left(\frac{x_{max}}{RMSE(x,y)}\right) \tag{5.20}$$

The PSNR, just like the SNR, is measured in decibels (dB).

The above values are easy to compute, but they are agnostic of the impression which humans might have of certain errors [315]. It is known that certain deviations between real and computed signal values are hardly noticed by humans. This is the foundation of lossy coding techniques such as MP3, JPEG, or digital TV standards. None of the metrics presented so far reflects the impression of deviations by humans.

Next, we will present the **universal image quality index** (UIQI) [562]. This index tries to capture changes in the structure of images, since the human eye is very sensitive to it. We will present the computation of this index for gray-scale images. Several values need to be computed [315]:

$$\mu_{x} = \frac{1}{n} \sum_{i=1}^{n} x_{i} \tag{5.21}$$

$$\mu_{y} = \frac{1}{n} \sum_{i=1}^{n} y_{i} \tag{5.22}$$

$$\ell(x, y) = \frac{2\mu_x \mu_y}{\mu_x^2 + \mu_y^2} \tag{5.23}$$

Equations (5.21) and (5.22) compute the average brightness of each of the images, and these averages are used to compute  $\ell(x, y)$ . For images of the same average brightness,  $\ell(x, y)$  will be equal to 1. Otherwise, this value will be less than 1.

Furthermore, we consider variances. Equations (5.24) and (5.25) compute the contrast of each of the images, and these averages are used to compute c(x, y):

$$\sigma_x = \sqrt{\frac{1}{(n-1)} \sum_{i=1}^{n} (x_i - \mu_x)^2}$$

(5.24)

$$\sigma_{y} = \sqrt{\frac{1}{(n-1)} \sum_{i=1}^{n} (y_{i} - \mu_{y})^{2}}$$

(5.25)

$$c(x, y) = \frac{2\sigma_x \sigma_y}{\sigma_x^2 + \sigma_y^2}$$

(5.26)

For images of the same average contrast, c(x, y) will be equal to 1. Otherwise, this value will be less than 1. Equation (5.27) computes the cross-correlation of the two images:

$$\sigma_{x,y} = \frac{1}{n-1} \sum_{i=1}^{n} (x_i - \mu_x)(y_i - \mu_y)$$

(5.27)

$$s(x, y) = \frac{\sigma_{x, y}}{\sigma_x \sigma_y} \tag{5.28}$$

Positive values of s(x, y) as computed from Eq. (5.28) correspond to a good correlation of the two images; negative values correspond to an inverse correlation. An overall quality index is then computed by Eq. (5.29):

$$Q(x, y) = \frac{2\mu_x \mu_y}{\mu_x^2 + \mu_y^2} * \frac{2\sigma_x \sigma_y}{\sigma_x^2 + \sigma_y^2} * \frac{\sigma_{x,y}}{\sigma_x \sigma_y}$$

(5.29)

Q=1 for identical images, and Q will be negative for inversely correlated images. It does not make sense to consider the correlation of images globally, since some inverse correlation in a particular block will already provide a negative impression about the image. Hence, Eq. (5.29) is computed only for blocks of pixels. The global UIQI value takes the values of Q for the different blocks into account.

The structural similarity index measure (SSIM) [563] is an extension of the UIQI objective.

Kühn compared the different metrics and found that none of these is really superior to others [315]. He recommends that several of these metrics should be computed and a careful comparison should be performed in practice. An overview over some useful objectives is also provided by Mittal [397].

In digital communications, the bit error ratio (BER) is an important metric.

**Definition 5.16** The **bit error ratio** (**BER**) is ratio of the number of bit errors divided by total number of communicated bits.

### 5.3.3 Criteria for Data Analysis

Sensors are typically not ideal in sense that some readouts deviate from the real values. Furthermore, it may be necessary to fuse data generated by various sensors. Hence, it is necessary to use data analysis techniques, e.g., machine learning (see p. 15). Generated results will not always be correct as well, either because sensor readouts were already compromised or due to imperfect data analysis techniques. In a way, we are dealing with approximate computing even though this term was not used in this context.

For data analysis, classification of objects is a very frequent goal. Let *X* be a set of objects which we would like to classify. Suppose that we restrict ourselves to binary classification.

Example 5.3 For example, consider the case of searching for amber at a beach. Unfortunately, white phosphorus as a leftover from bombs found, e.g., at the Baltic ocean, looks very much like amber but starts to suddenly burn at 1300 °C when it dries. Classifying some found objects as either amber or phosphorus is thus a very delicate task (and hence, inexperienced people should not touch such objects anyway).

In this context, four cases are possible:

True positives (TP): we classify some object as amber, and it is actually valuable

amber.

- False positive (FP): we classify some object as amber, and it is actually dangerous.

- **True negative** (TN): we classify some object as dangerous and it is actually dangerous.

- False negative (FN): we classify some object as dangerous, and it is actually

valuable amber.

Absolute numbers have to be related to each other. Hence, the following metrics have been defined:

#### **Definition 5.17** The **precision** p is defined as the fraction

$$p = \frac{TP}{TP + FP} \tag{5.30}$$

In the case of searching for amber, we aim at a precision of 1, since we do not want to get burnt.

#### **Definition 5.18** The **recall** r (or **sensitivity**) is defined as the fraction

$$r = \frac{TP}{TP + FN} \tag{5.31}$$

In order to obtain a good precision, we will have to accept some false negatives (e.g., amber classified as phosphorus).

#### **Definition 5.19** The accuracy acc is defined as the fraction

$$acc = \frac{TP + TN}{TP + FP + TN + FN} \tag{5.32}$$

In the case of searching for amber, we might tolerate a non-optimal accuracy, due to the importance of keeping false positives as close to zero as possible, and, hence, we might have several false negatives.

#### **Definition 5.20** The *specificity* is defined as the fraction

$$specificity = \frac{TN}{TN + FP} \tag{5.33}$$

**Definition 5.21** The *F*1 score or *F-measure* is defined as the harmonic mean of precision and recall:

$$F1 = 2\frac{p * r}{p + r} \tag{5.34}$$

In a more general context, the **quality of service** (QoS) is another well-known metric. Frequently, it is related to the quality of communication channels, where bit error rates, latency, and bandwidth are indicators of quality.

In an even wider sense, we may also consider not just those technical parameters but also the overall experience for the user. This is captured in the **quality of experience** (QoE) metric, which refers to the overall user experience including all aspects which might be considered by a user. There is a number of metrics which can be used to estimate the overall quality of experience [400].

## **5.4** Energy and Power Models

## 5.4.1 General Properties

**Energy models** and **power models** are essential for evaluating the corresponding objectives. Such models are needed for optimizations aiming at a reduction of power and energy consumptions. They are also required for optimizations trying to reduce operating temperatures and to improve reliability. Power estimation is used in **power management** algorithms (see p. 373).

Energy and power models are closely related, as can be seen from Eq. (3.13). Energy can be computed as the integral of power over time. Once the energy consumption is known, we can compute the average power consumption. In general, we can use:

Measurements on real hardware: measurements can be very precise, but they

apply only to the hardware at hands. Measuring voltages is typically rather easy

and does not require complex procedures.

Measuring currents can be done with a current clamp or a shunt resistor.

- Current clamps have to enclose one of the wires of the power supply cable. They measure the magnetic field caused by the current flowing through the cable. The advantage of this approach is that no power wires have to be broken and power will remain connected unchanged to the device being analyzed. The disadvantage is that current clamps do not allow precise measurements.

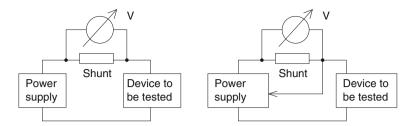

- Using an **ammeter** typically results in a better precision. However, an insertion of the ammeter directly into the power line has some disadvantages. For example, the system is unpowered if we remove the ammeter. Also, long cables might add noise. Therefore, it is typically preferable if we include a shunt resistor. A typical circuit containing a **shunt** is shown in Fig. 5.16 (left).

The advantage of using a shunt resistor over using a simple ammeter is that the shunt can be integrated into the power wires. Due to the shunt resistor, currents flowing into the device under test will cause a voltage drop across the shunt, and this voltage can be measured and used to compute the current from Ohm's law. Finding the right resistance of the shunt is an issue. If the resistance is too large, the device under test will be powered with a voltage lower than the original voltage and might even fail to work. If the resistance is too small, the voltage across the shunt will be too small to be reliably

Fig. 5.16 Measuring current: left, two-wire connection; right, feedback into voltage regulator

measured and will be subject to a substantial amount of noise. Selecting the right resistance depends on the current flowing into the device under test. If this current varies substantially, it may even be necessary to employ several shunt resistors and switch between them, depending on the current actually flowing. The problem regarding the voltage drop can be partially avoided when regulated power supplies are used and the regulator feedback input can be connected to the voltage actually powering the device (see Fig. 5.16 (right)). The power supply would then try to keep the voltage at the device at its nominal level. However, the voltage across the shunt is affected by the current flowing back into the voltage regulator input.

Unfortunately, there will not be a separate power pin or wire for every component within the device and we can compute only a lumped sum of currents drawn by the device. We may have to stimulate the device in a particular way in order to get information about the consumption of the different components.

• Models can be used even when real hardware is not available, but they can be very imprecise. Models have to be validated; otherwise they would remain very questionable. Two validation methods can be found for many of the available power and energy models: either models are validated against more detailed models at a lower level of abstraction, or they are compared with measurement for real devices, resulting in a hybrid model. Validation against measurements requires a method for selecting model parameters. Frequently, linear models are selected, and parameters are selected with using the least square method (minimizing the MSE as per Eq. (5.16)). Curve fitting with this method is typically available in mathematical tool boxes such as MATLAB<sup>®</sup>. More recently, using machine learning for this purpose became more preferable. For example, Falkenberg et al. [161] used machine learning for modeling the power consumption of transmitters in mobile phones.

There is no one-approach-fits-all solution for energy consumption modeling. Instead, the usual approach is to combine ideas for modeling to fit the needs at hand. Therefore, we will present representative examples of power models and hope that the reader will identify the combination of methods which fits his/her constraints best.

## 5.4.2 Energy Model for Memories

As described in the section on memory hardware (see p. 168), the energy consumption of caches and other memories can be computed with CACTI [408, 589]. CACTI assumes an abstract layout of the memory, extracts capacitances from the layout, and computes access times, cycle times, area, leakage, and dynamic power consumption from this information. CACTI has been validated against models of the same memories at a more detailed level, employing SPICE [519] as the solver at that level. Currently (in 2020), the most recent version of CACTI (version 6.5) is available from <a href="http://www.hpl.hp.com/research/cacti/">http://www.hpl.hp.com/research/cacti/</a>. Recent enhancements include detailed modeling of the interconnect and modeling of non-uniform memory accesses. Models of transmitters and sense amplifiers have been included. Also, used architectural and technological parameters can be specified.

## 5.4.3 Energy Model for Instructions

One of the first power models was proposed by Tiwari [542]. The model includes so-called base costs and inter-instruction costs. Base costs of an instruction correspond to the energy consumed per instruction execution if an infinite sequence of instances of that instruction is executed. Base costs have been computed by running programs consisting of 120 identical instructions and a branch back to the beginning of this sequence. Programs are designed such that no stall cycles appear. This may require the adding of no-operation instructions and some simple calculations to eliminate their contribution to the energy consumption.

Inter-instruction costs model the additional energy consumed by the processor if instructions change. This additional energy is required, for example, due to switching functional units on and off. Inter-instruction costs reflect the impact of the initial circuit state on the overall energy consumption of an instruction. These costs can be computed by running programs containing an alternating sequence of instructions pairs.

Base costs and inter-instruction costs are computed for a program not generating any cache misses. The effect of cache misses has to be added to these two costs. This requires the knowledge of the cache miss ratio and the memory access energy. The memory energy depends on the addresses accessed. No attempt is made to statically predict memory addresses. Hence, this contribution can only be determined dynamically, during the execution of the program.

The model has been applied to two real systems, an Intel 486 DX2 and a Fujitsu SPARClite 934. Measurements of the currents have been used to calibrate the model.

<sup>&</sup>lt;sup>5</sup>It is recommended to use this URL, since there are several tools with the same name. Currently, a modifiable C++-version is available. Previously available web interfaces do not exist any longer.

### 5.4.4 Energy Model for Functional Processor Units

The Wattch power estimation tool [70] estimates the power consumption of microprocessor systems at the architectural level. Wattch uses the SimpleScalar simulator to simulate processors. SimpleScalar can be configured to model the processor at hand as closely as possible. The number of pipeline stages and functional units is typically correctly modeled, whereas some more specialized features are possibly not. Wattch is based on detailed information on the energy consumption of the different components which we could find in a microprocessor. While running, SimpleScalar keeps track of invoked functional units. Wattch exploits this information in order to compute an overall energy consumption.

Wattch requires much more information about the architecture than Tiwari's instruction-set level approach. For example, Wattch includes its own detailed model of the energy consumption in memories. Also, clocking is taken explicitly into account, including conditional clocking if clock gating is used. In the original paper [70], results have been validated for three different processors.

## 5.4.5 Energy Model for Processor and Memory

The level of details of the model by Steinke et al. [510] lies between that of Tiwari and that of Wattch. For instructions and for data, the model considers the sum of the energies consumed in the CPU and the memory:

$$E_{total} = E_{cpu\_instr} + E_{cpu\_data} + E_{mem\_instr} + E_{mem\_data}$$

(5.35)

Each of the four terms is then computed from detailed equations. The following notation is used in these equations: m is the number of instructions considered, w(b) returns the number of ones in its argument (either code or data),  $h(b_1, b_2)$  returns the Hamming distance between its two arguments, dir denotes the direction of data transfer, and  $\alpha_i$  and  $\beta_i$  ( $i \in \{1..10\}$ ) are constants computed from curve fitting of measured energies. Using this notation,  $E_{cpu}$  data can be computed as follows:

$$E_{cpu\_data} = \sum_{i=1}^{m} \left\{ \alpha_5 * w(DAddr_i) + \beta_5 * h(DAddr_{i-1}, DAddr_i) + \alpha_{6,dir} * w(Data_i) + \beta_{6,dir} * h(Data_{i-1}, Data_i) \right\}$$

(5.36)

where  $Data_i$  is the data value used in instruction i, and  $DAddr_i$  is its address.

Furthermore, consider  $E_{mem\_data}$ , a term which is relevant only when the data is actually loaded from the main memory:

$$E_{mem\_data} = \sum_{i=1}^{m} \left\{ BaseMem(DataMem, dir, Word\_width) \right. \\ \left. + \alpha_9 * w(DAddr_i) + \beta_9 * h(DAddr_{i-1}, DAddr_i) \right. \\ \left. + \alpha_{10,dir} * w(Data_i) + \beta_{10,dir} * h(Data_{i-1}, Data_i) \right\}$$

(5.37)

where BaseMem is the base cost for accessing a memory object of a particular width in direction dir.

$E_{mem\ instr}$  can be computed as follows:

$$E_{mem\_instr} = \sum_{i=1}^{m} \left\{ BaseMem(InstrMem, Word\_width_i) + \alpha_7 * w(IAddr_i) + \beta_7 * h(IAddr_{i-1}, IAddr_i) + \alpha_8 * w(IData_i) + \beta_8 * h(IData_{i-1}, IData_i) \right\}$$

(5.38)

where BaseMem is the base cost for accessing a memory word of a particular width from the instruction memory,  $IAddr_i$  is the address of the instruction, and  $IData_i$  is instruction i itself.

$E_{cpu\ instr}$  can be computed from the following equation:

$$E_{cpu\_instr} = \sum_{i=1}^{m} \left\{ BaseCPU(Opcode_i) + FUChange(Instr_{i-1}, Instr_i) \right.$$

$$\left. + \alpha_4 * w(IAddr_i) + \beta_4 * h(IAddr_{i-1}, IAddr_i) \right.$$

$$\left. + \sum_{j=1}^{s} \left( \alpha_1 * w(Imm_{i,j}) + \beta_1 * h(Imm_{i-1,j}, Imm_{i,j}) \right) \right.$$

$$\left. + \sum_{k=1}^{t} \left( \alpha_2 * w(Reg_{i,k}) + \beta_2 * h(Reg_{i-1,k}, Reg_{i,k}) \right) \right.$$

$$\left. + \sum_{k=1}^{t} \left( \alpha_3 * w(RegVal_{i,k}) + \beta_3 * h(RegVal_{i-1,k}, RegVal_{i,k}) \right) \right\}$$

where BaseCPU is the base cost for  $Opcode_i$ , FUChange(..) reflects the costs caused by the transition from instruction i-1 to i, Imm reflects the impact of up to s immediate values per instruction, Reg reflects the register numbers of up to t registers per instruction, and RegVal reflects up to t register values per instruction.

To determine constants, dedicated code sequences have to be designed in order to attribute energy consumption to particular terms of the equations.

*Example 5.4* The following code sequence allows measuring the energy required for executing a load word instruction:

```

start: lw R1, address /* load word */

lw R1, address /* load word */

... /* lw instruction repeated 50-100 times */

bra start /* back to the start */

```

The impact of the branch back to the beginning on the energy consumption can be neglected. The impact of different addresses, register numbers, and register content can be studied by varying these values. For example, we can initially set all these values to zero and then incrementally study the impact of additional ones.  $\nabla$

In our own experiments, constants were determined by running a linear regression method on the data. A significant impact of the number of ones in the data was found, which would have been unnoticed for Tiwari's model.

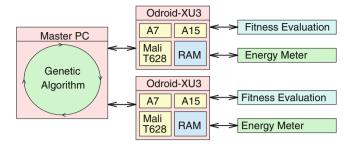

## 5.4.6 Energy Model for an Application

The Odroid-XU3 [202] platform (see Fig. 5.17) comprises current sensors. The sensors enable precise measurement of the consumed power during the execution of applications, measuring the consumption of ARM® big cores, little cores, GPU, and DRAM individually. This possibility is exploited by several researchers. For example, Neugebauer et al. [416] have integrated Odroid-XU3 processors into their design space exploration for one application. Hence, design space exploration is based on a realistic analysis of the consumed energy. This approach eliminates the use of models of unknown precision. The overall approach for design space exploration enabled by the XU3 is shown in Fig. 5.18.

Fig. 5.17 Odroid-XU3

Fig. 5.18 Evolutionary algorithm, fitness estimation based on real measurements

The design space exploration is based on a genetic algorithm. The evaluation of a particular solution is based on real execution of the code on an XU3. The resulting optimized algorithm has been used by Neugebauer et al. [417] within the cyberphysical system PAMONO which is capable of detecting bio-viruses online. It is based on the physical so-called Plasmon effect of visualization of small objects. Unfortunately, the Odroid-XU3 has been discontinued and replaced by the XU4 not including current sensors.

# 5.4.7 Energy Model for Multiple Applications with Hardware Multithreading

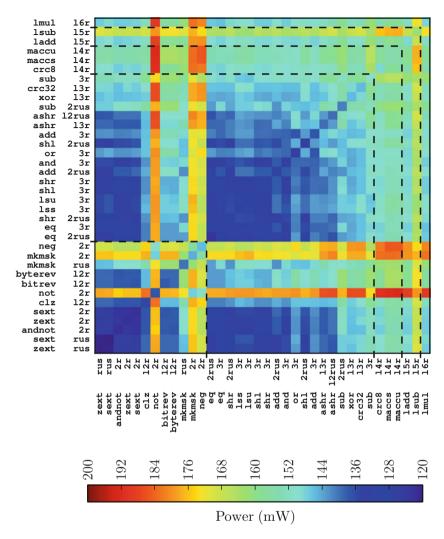

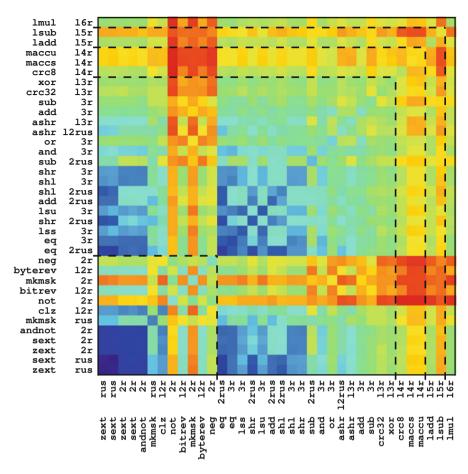

Kerrison and Eder analyzed the energy consumption of the XMOS XS1-L multithreaded processor design for real-time applications [290]. One of the particular features of that processor is its hardware-supported multithreading: it performs fast context switching between four threads in hardware. One of the research questions was: how much does the hardware context switching between threads cost? Due to the availability of real hardware, this question could be answered with real measurements. The power consumed by the XMOS XS1-L was measured with a shunt resistor inserted into its power cable, and the resistor was connected to an INA219 power measurement chip (see <a href="http://www.ti.com/product/ina219">http://www.ti.com/product/ina219</a>). The software running on the processor was controlled from a second processor. It turned out that the best energy efficiency was reached when all four hardware threads are used. However, hardware multithreading leads to many charging/discharging operations and a corresponding energy consumption. The interesting experimental results include an analysis of the impact of executed instructions on the energy consumption, as shown in Fig. 5.19 for the case of 8 bit data.

Figure 5.20 displays the corresponding information for the case of 16 bit data.

The two dimensions of the diagrams encode the applications which are run in the odd and even threads, respectively. In these figures, a change in the number of operands is indicated by dashed lines. Instructions with three or more operands are

Fig. 5.19 Power analysis for multithreading for 8 bit data, top, power consumption as a function of instructions on 8 bit data executed in the even threads (vertical axis) and in the odd threads (horizontal axis) ©Kerrison, Eder; bottom, color encoding of temperatures

shown at the top and at the right end of each diagram. Obviously, the consumed energy increases with the number of operands. Figure 5.20 demonstrates that processing 16 bit data requires more energy than processing 8 bit data. Kerrison et al. use these results in order to optimize embedded software.

**Fig. 5.20** Power analysis for multithreading for 16 bit data, power consumption as a function of instructions on 16 bit data executed in the even threads (vertical axis) and in the odd threads (horizontal axis); temperature encoding as in Fig. 5.19 (bottom) ©Kerrison, Eder

# 5.4.8 Energy Model for an Android Mobile Phone

Zhang et al. [612] describe a power model construction technique for an HTC Android phone, called PowerBooter. Their technique uses the following equation:

$$E = (\beta_{uh} * freq_h + \beta_{ul} * freq_l) * util + \beta_{CPU} * CPU_{on}$$

$$+\beta_{br} * brightness + \beta_{Gon} * GPS\_{on} + \beta_{Gsl} * GPS\_{sl}$$

$$+\beta_{WiFi\_l} * WiFi_l + \beta_{WiFi\_h} * WiFi_h + \beta_{3G\_idle} * 3G_{idle}$$

$$+\beta_{3G\_FACH} * 3G_{FACH} + \beta_{3G\_DCH} * 3G_{DCH}$$

(5.40)

where

$\beta$ : constants to be determined

$freq_i$ : CPU frequencies

util: CPU utilization

$CPU_{on}$ : refers to processor utilization

brightness: takes illumination into account

GPS: relates to GPS usage

$WiFi_l$ : amount of time, Wi-Fi is in low-speed mode

$WiFi_h$ : amount of time, Wi-Fi is in high-speed mode

$3G_{3G\ idle}$ : amount of time, 3G is idle

$3G_{FACH}$ : amount of time, a shared 3G channel is used

$3G_{DCH}$ : amount of time, a dedicated 3G channel is used

Obviously, PowerBooter is abstracting much more from the details of the hardware implementation. Note that PowerBooter also includes communication, which was not taken into account in our previous models. Parameters are determined, as before, by measuring currents in dedicated setups and using some curve fitting method. Measurements are based on a Monsoon power monitor (see <a href="http://www.msoon.com/LabEquipment/PowerMonitor/">http://www.msoon.com/LabEquipment/PowerMonitor/</a>).

The model construction technique allows, in combination with a battery model, a prediction of battery lifetime. The resulting information is made available to a tool called PowerTutor. PowerTutor is intended to provide some help for adjusting applications to different hardware platforms and as an aid for application developers to exploit power-saving techniques in their application without digging deep into the peculiarities of the available hardware.

Another model for the energy consumption in mobile phones was presented by Dusza et al. [144]. Several commercial tools also provide power and/or energy estimation.

All of the energy consumption models considered so far were designed to model an **average case** power or energy consumption, where term "average case" might still need some clarification. Computed models might apply only for certain inputs or for certain initial states. Average case results are valuable for predicting temperatures and battery lifetime for certain time intervals.

## 5.4.9 Worst Case Energy Consumption

In certain contexts, the **worst case** power consumption or **worst case** energy consumption is of interest.

5.5 Thermal Models 269

**Definition 5.22** The worst case energy consumption (WCEC) of an embedded system is defined as the largest energy consumption, computed as the maximum of the energy consumption for all inputs and initial states.

**Definition 5.23** The worst case power consumption (WCPC) of an embedded system is defined as the largest power consumption, computed as the maximum of the power consumption for all inputs and initial states.

The WCPC is relevant in the context of the dimensioning of the interconnect and the power supply. The WCEC is relevant in the context of the design of battery systems. We need to guarantee that the chosen battery system meets the WCEC requirements. A safe upper bound on the WCEC can be computed as follows:

$$WCEC \le \int_0^{WCET} WCPC dt = WCET * WCPC$$

Techniques for tighter WCEC estimation have been proposed, for example, by Jayaseelan et al. [271], by Pallister et al. [443], and by Wägemann et al. [559]. Similar to the computation of worst case execution times, these tighter bounds may still be an overestimation, and the actual worst case power and energy consumption are still unknown.

#### 5.5 Thermal Models

The quest for higher performances of embedded systems increased the chances of components becoming hot. Temperatures of the various components of embedded systems can have a serious impact on their usability, e.g., on sensor readouts. In the worst case, overheated components cause damages to other systems. For example, they may cause fire hazards. Hot components might also have other consequences, even in the absence of immediate failures. For example, the system life might be shortened, sometimes by large factors (see Black's equation on p. 283). Also, it may be necessary to power down parts of silicon chips in order to avoid overheating. This has been called the **dark silicon** problem [153].

The thermal behavior of embedded systems is closely linked to the transformation of electrical energy into heat. Therefore, thermal models are usually linked to energy models. Thermal models are based on the laws of physics.<sup>6</sup>

<sup>&</sup>lt;sup>6</sup>We will denote temperatures by  $\theta$  in order to avoid confusion with periods denotes by T.

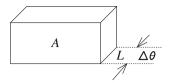

**Fig. 5.21** Plate of thickness *L*

**Table 5.1** Approximate thermal characteristics of materials for air, copper, and silicon

|                 | $\kappa$ : thermal conductivity | $c_p$ : specific heat | $c_v$ : volumetric heat capacity          |

|-----------------|---------------------------------|-----------------------|-------------------------------------------|

| Material        | (W/(K m))                       | (J/(K g))             | $(J/(K m^3))$                             |

| Air (25 C)      | 0.025 [583]                     | 1.012 [578]           | $1.21 * 10^3 [578]$                       |

| Copper          | 401 [583]                       | 0.385 [568, 578]      | 3.45 * 10 <sup>6</sup> [578]              |

| Silicon (≈26 C) | 148 [148]                       | 0.705 [148, 568]      | 1.64 * 10 <sup>6</sup> [148] <sup>a</sup> |

<sup>&</sup>lt;sup>a</sup>Calculated using Eq. (5.56)

## 5.5.1 Steady-State Behavior

Consider a homogeneous plate made of a particular material and of area A and thickness L (see Fig. 5.21). Suppose that there is a temperature difference of  $\Delta\theta$  between the opposite sides. We assume that heat will be propagating independently of the direction (isotropy), and we assume being in the steady state (no transients). Furthermore, the sides of area are supposed to be much larger than the thickness of the plate, and we can ignore effects at the boundary of the plate. Then, the thermal power which gets transferred across the plate is equal to

$$P_{th} = \kappa \frac{\Delta \theta * A}{L}$$

where: (5.41)

$P_{th}$ : thermal power transferred;  $\kappa$ :thermal conductivity; A: area;  $\Delta\theta$ : temperature difference; L: thickness

Equation (5.41) is also known as **Fourier's law**.

**Definition 5.24** Due to Eq. (5.41), we can define **thermal conductivity**  $\kappa$  as the amount of the thermal power  $P_{th}$  transferred through a plate made of some material of unit area and unit thickness when the temperatures at the opposite side differ by one temperature unit (typically Kelvin).

Frequently,  $\lambda$  is used instead of  $\kappa$ .  $\kappa$  depends on the material and environmental conditions. Values for some common materials for common conditions are included in Table 5.1. Refer to the cited sources for more information on the dependency on environmental conditions.

**Definition 5.25 Thermal conductance** [169] is defined as the amount of thermal energy which passes through a plate per unit of time if the temperatures at the two ends differ by one unit of temperature (typically Kelvin).

From Eq. (5.41), we have

5.5 Thermal Models 271

**Fig. 5.22** Thermal model of microprocessor with fan

$$\frac{P_{th}}{\Delta \theta} = \kappa * \frac{A}{L} \tag{5.42}$$

The reciprocal of this value is called thermal resistance  $R_{th}$ :

$$R_{th} = \frac{\Delta \theta}{P_{th}} = \frac{L}{\kappa * A} \tag{5.43}$$

**Lemma 5.1** Thermal resistances add up like electrical resistances. This allows us to map thermal modeling to electrical modeling.

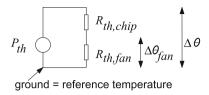

Example 5.5 Figure 5.22 shows a microprocessor generating a thermal power  $P_{th}$  together with the thermal resistance  $R_{th,die}$  of the die (chip) and the thermal resistance  $R_{th,fan}$  of the fan.

Adding resistances results in the following equations

$$R_{th} = R_{th,die} + R_{th,fan} (5.44)$$

$$\Delta \theta = R_{th} * P_{th} \tag{5.45}$$

Let us assume the following:

$$R_{th die} = 0.4 \,\text{W/K}$$

(5.46)

$$R_{th, fan} = 0.3 \text{ W/K}$$

(5.47)

$$P_{th} = 10 \,\mathrm{W}$$

(5.48)

Then, we compute:

$$\Delta \theta = 7 \,\mathrm{K} \tag{5.49}$$

$$\Delta\theta_{fan} = 3 \,\mathrm{K} \tag{5.50}$$

Consumed power and thermal resistances are related to the estimation of the thermal design power.  $\nabla$

**Definition 5.26** ([584]) "The thermal design power (TDP), sometimes called thermal design point, is the maximum amount of heat generated by a computer chip or component (often the CPU or GPU) that the cooling system in a computer is

designed to dissipate in typical operation. Rather than specifying CPU's real power dissipation, TDP serves as the nominal value for designing CPU cooling systems."

We could try to derive the TDP from the WCPC. In practice, however, published TDP values are typically smaller. Hence, temperature sensors are required in order to obtain a safe operation.

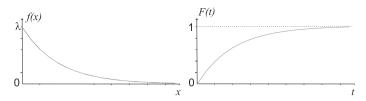

#### 5.5.2 Transient State Behavior

So far, we have just considered the steady state. In general, transients and thermal capacitance (heat capacity) have to be considered.

**Definition 5.27** The **thermal capacitance** (**heat capacity**) of some object is defined as the amount of thermal energy  $E_{th}$  which can be stored per difference  $\Delta\theta$  in temperatures:

$$C_{th} = \frac{E_{th}}{\Delta \theta} \tag{5.51}$$

Primarily,  $C_{th}$  depends on the amount and type of matter contained in the object:

$$C_{th} = c_p * m ag{5.52}$$

where  $c_p$  is the specific heat and m the mass. We can also interpret Eq. (5.52) as the definition of the specific heat:

**Definition 5.28** The **specific heat**  $c_p$  of some object made of some material of mass m is defined as

$$c_p = \frac{C_{th}}{m} \tag{5.53}$$

$c_p$  depends on the type of matter used.  $c_p$  is temperature-dependent, but can be considered constant for small temperature ranges.

In our context, it is frequently more convenient to consider the heat capacity per volume instead of per unit of mass.

**Definition 5.29** The **volumetric heat capacity**  $c_v$  is defined as

$$c_v = \frac{C_{th}}{\mathcal{V}} \tag{5.54}$$

where V is the volume of the object.

$c_v$  and  $c_p$  are related by the mass density:

**Definition 5.30** The mass density or volume density  $\rho$  is defined as

5.5 Thermal Models 273

$$\rho = \frac{m}{V} \tag{5.55}$$

Inserting  $\mathcal{V} = m/\rho$  into the definition of  $c_v$ , we have

$$c_v = \frac{C_{th}}{V} = \frac{C_{th} * \rho}{m} = c_p * \rho \tag{5.56}$$

This allows us to convert between tables published for  $c_p$  and  $c_v$  (see, e.g., Table 5.1). Due to the correspondence to electrical circuits, we can also compute the transient behavior.

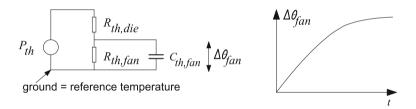

Example 5.6 We extend our microprocessor example as shown in Fig. 5.23 (left).

The resulting transient for the temperature across the die and the fan is shown in Fig. 5.23 (right). The system approaches the stable state like a network of resistors and capacitors.  $\nabla$

Overall, it is feasible to model thermal behavior by using an equivalent electrical model. Equivalences are shown in Table 5.2.

Fig. 5.23 Microprocessor with fan: left, thermal model; right, transient

Table 5.2 Equivalences between electrical and thermal models

| Electrical model                   |                               | Thermal model                    |                                         |

|------------------------------------|-------------------------------|----------------------------------|-----------------------------------------|

| Current                            | I                             | Thermal flow, "power flow"       | $P_{th} = \dot{Q}$                      |

| Total charge                       | $Q = \int I  \mathrm{d}t$     | Thermal energy                   | $E_{th} = \int P_{th}  \mathrm{d}t$     |

| Potential                          | $\phi$                        | Temperature                      | θ                                       |

| Voltage = potential difference     | $V = \Delta \phi$             | Temperature difference           | $\Delta \theta$                         |

| Resistance <sup>a</sup>            | $R = \rho_{el}   \frac{L}{A}$ | Thermal resistance               | $R_{th} = \frac{1}{\kappa} \frac{L}{A}$ |

| Ohm's law                          | V = R * I                     | $\Delta$ temperature at $R_{th}$ | $\Delta\theta = R_{th} * P_{th}$        |

| Capacitance                        | C                             | Thermal capacitance              | $C_{th}$                                |

| Charge on capacitor                | Q = C * V                     | Energy at capacitance            | $E_{th} = C_{th} * \Delta T$            |

| Capacitance of object <sup>b</sup> | $C = \rho_q \mathcal{V}$      | Capacitance of object            | $C_{th} = c_v \mathcal{V}$              |

$<sup>^{\</sup>mathrm{a}}\rho_{el}$  is the specific electrical resistance or volume resistivity

$<sup>{}^{\</sup>rm b}\rho_q$  is the volume charge density

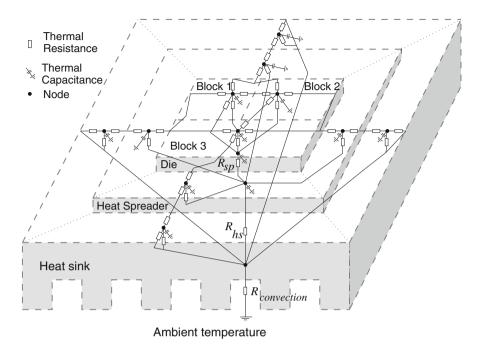

Fig. 5.24 HotSpot model of a chip mounted on a heat spreader and a heat sink

Well-known techniques for solving electrical network equations (see, e.g., Chen et al. [96]) apply. However, there is no component corresponding to inductances on the thermal side. This equivalence between thermal and electrical models is exploited in tools such as HotSpot [500]. Figure 5.24 shows a HotSpot model of a chip mounted on a heat spreader which in turn is mounted on a heat sink [499]. Skadron et al. [499] emphasize the fact that large temperature gradients can exist within a chip, a heat spreader, or a heat sink. Hence, it is important not to assume a uniform temperature for these parts. In Fig. 5.24, the chip is assumed to comprise three micro-architectural components with each component forming one thermal zone.

The heat spreader and the heat sink are modeled as five zones each. One zone of the heat spreader is located beneath the chip, and four zones are located on the sides. Zones on the sides possess a trapezoid-like shape and are indicated by dotted lines. The same partitioning has been done for the heat sink. Zones in the center cannot be shown in Fig. 5.24; they are hidden. Otherwise, each of the zones is shown as a node in the equivalent network in Fig. 5.24. The ambient temperature is assumed to be homogeneous.  $R_{convection}$  is the thermal resistance to the environment. It is connected to the five zones of the heat sink.  $R_{hs}$  is thermal resistance between the heat spreader and the heat sink. The heat sink is also modeled as five zones. The one in the center is connected to the chip via  $R_{sp}$ . The heat source is actually not shown. For each of the zones, there is one thermal capacitance. Each of them models the difference in temperatures if compared to the environment. Accordingly, it is always

considered to be connected to the ground. Furthermore, for each of the zones, there is a pair of thermal resistors connecting adjacent zones.

In their experiments, Skadron at al. have used the Wattch (see p. 262) power simulator as heat source. Microarchitectural simulators such as SimpleScalar can be used to drive Wattch. HotSpot contains mechanisms to create a system of partial differential equations for models such as the one in Fig. 5.24. These equation systems are then solved using a Runge-Kutta equation solver.

Skadron et al. found that it is necessary to consider different thermal zones. Furthermore, they found that power consumption has an impact on the temperature, but in order to really check whether thermal constraints are met, one needs to model temperature explicitly. Several power-saving optimizations had only a small impact on crucial temperatures. For example, register files tend to get hot. Saving power on memory references is of little help in this context and might even have a negative impact.

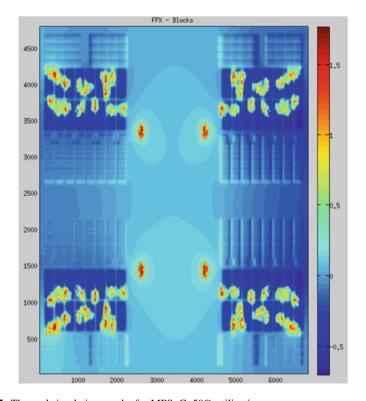

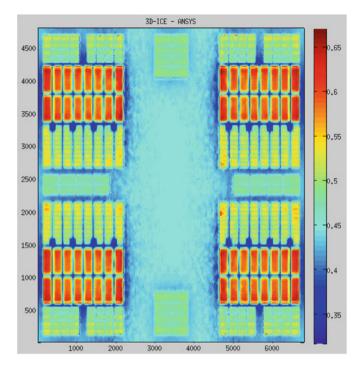

*Example 5.7* As an example of the results of thermal modeling, we consider an MPSoC of STMicroelectronics, comprising 64 P2012 cores [506]. Thermal modeling of this MPSoC has been performed with the 3D-ICE [24] tool. *Relative* temperatures for this MPSoC are shown in Fig. 5.25. High temperatures are shown in red and low temperatures in blue.

The MPSoC contains four clusters, each including 16 cores. Each of the corners of the layout corresponds to one cluster. The 16 processors are located at the center of the clusters. Memories are located below and above the processors. Simulation confirms that the processors are hotter than the memories. The higher utilization of Fig. 5.25 (bottom) leads to higher temperatures. Detailed modeling of the layout avoided temperature overestimation.  $\nabla$

Validation of thermal models requires precise temperature measurements [394].

## 5.6 Dependability and Risk Analysis

Next, we are going to look at dependability and possible risks.

## 5.6.1 Aspects of Dependability

Embedded and cyber-physical systems (like other products) can cause damages to properties and lives. The fact that such systems are potentially safety-critical was already included in Table 1.2 on p. 18. Hence, in general, we have to take this fact into account. It is not possible to reduce the risk of damages to zero. The best that we

<sup>&</sup>lt;sup>7</sup>Images are included with permission of David Atienza (EPFL). Images were obtained as part of the cooperation between EPFL and STMicroelectronics in the FP7 EU Project titled: "PRO3D: Programming for Future 3D Architectures with Many Cores".

Fig. 5.25 Thermal simulation results for MPSoC: 50% utilization

can do is to make the probability of damages small, hopefully orders of magnitude smaller than other risks. Dependability comprises various aspects, most importantly safety and data security. These, in turn, contain aspects such as reliability and confidentiality. Designs must be evaluated with respect to these aspects.

# 5.6.2 Security Analysis

Security of embedded and cyber-physical systems was not seen as a serious issue when these systems were not electronically accessible from the outside. This has changed for systems which can be accessed through communication channels, and the two are now much more related, since security holes can cause physical malfunctions resulting in accidents.

Security analysis needs to consider attacker models mentioned already in Sect. 3.8. This analysis needs to find out if attacks are feasible even without having physical access to the embedded system. If the system can be physically accessed, physical attacks must be considered as well.

Fig. 5.25 (continued): 100% utilization

Furthermore, relationships between encryption and decryption protocols and achievable data rates must be analyzed, since it could easily happen that resource-constrained embedded devices do not provide the expected encryption and decryption rates.

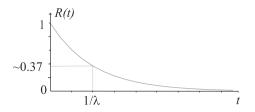

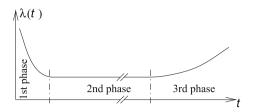

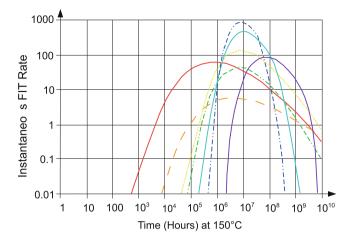

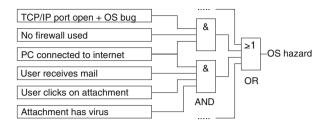

# 5.6.3 Safety Analysis

Damages should also be avoided, as much as possible, by designing safe systems. In practice, at best we can expect to design a system such that the probability of damages is orders of magnitude less than the probability of damages from other risks.