Abstract

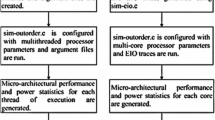

A method and algorithm for accelerating the simulation in the route of the joint hardware-software verification of Multicore systems-on-chip (SoC) are developed. An approach with the peculiarity of simulating the asymmetric memory access, which provides the solution for the synchronization problem in multiprocessor systems with a considerable increase in performance as compared to the simulation of the RTL model, is proposed.

Similar content being viewed by others

References

Solokhina, T.V., Architecture of DSP accelerators based on the Multicore platform for new-generation supercomputers, in Problemy razrabotki perspektivnykh mikro- i nanoelektronnykh sistem: sb. nauch. tr. (Problems of Developing Promising Micro- and Nanoelectronic System: Collection of Papers), Stempkovskii, A.L., Ed., Moscow: IPPM RAN, 2008, pp. 415–418.

Samir Palnitkar, Verilog HDL: A Guide to Digital Design and Synthesis, Pearson Education, 2003, p. 450.

Bibilo, P.N., Osnovy yazyka VHDL (Fundamentals of VHDL), Moscow: Solon-R, 2002, p. 224.

Open Virtual Platforms, First time use of OVP simulators and emulators with MIPS processors and platforms. http://www.ovpworld.org/first_MIPS.php. Accessed March 15, 2012.

ARM Ltd., Emulation baseboard real-time system model user guide. http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.dui0424b/index.html. Accessed March 15, 2012.

Author information

Authors and Affiliations

Corresponding author

Additional information

Original Russian Text © V.S. Gavrilov, G.G. Kazennov, 2013, published in Izvestiya Vysshikh Uchebnykh Zavedenii. Elektronika, 2013, No. 2(100), pp. 59–65.

Rights and permissions

About this article

Cite this article

Gavrilov, V.S., Kazennov, G.G. Method of simulation the asymmetric memory access for solving synchronization problems in multiprocessor systems. Russ Microelectron 43, 496–500 (2014). https://doi.org/10.1134/S1063739714070087

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1134/S1063739714070087