Abstract

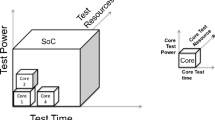

We propose an integrated framework for the design of SOC test solutions, which includes a set of algorithms for early design space exploration as well as extensive optimization for the final solution. The framework deals with test scheduling, test access mechanism design, test sets selection, and test resource placement. Our approach minimizes the test application time and the cost of the test access mechanism while considering constraints on tests and power consumption. The main feature of our approach is that it provides an integrated design environment to treat several different tasks at the same time, which were traditionally dealt with as separate problems. We have made an implementation of the proposed heuristic used for the early design space exploration and an implementation based on Simulated Annealing for the extensive optimization. Experiments on several benchmarks and industrial designs show the usefulness and efficiency of our approach.

Similar content being viewed by others

References

J. Aerts and E.J. Marinissen, “Scan Chain Design for Test Time Reduction in Core-Based ICs, ” in Proceedings of IEEE International Test Conference (ITC), Washington, DC, Oct. 1998, pp. 448–457.

A. Benso, S. Cataldo, S. Chiusano, P. Prinetto, and Y. Zorian, “A High-Level EDAEnvironment for the Automatic Insertion of HD-BIST Structures, ” Journal of Electronic Testing; Theory and Applications (JETTA), vol. 16, no. 3, pp. 179–184, June 2000.

H. Bleeker, P. Van Den Eijnden, and F. De Jong, Boundary-Scan Test: A Practical Approach, Boston, MA: Kluwer Academic Publishers, 1993.

K. Chakrabarty, “Test Scheduling for Core-Based Systems, ” in Proceedings of IEEE/ACM International Conference on Computer Aided Design (ICCAD), San Jose, CA, Nov. 1999, pp. 391–394.

K. Chakrabarty, “Design of System-on-a-Chip Test Access Architectures Using Integer Linear Programming, ” in Proceedings of IEEE VLSI Test Symposium (VTS), Montreal, Canada, April 2000, pp. 127–134.

K. Chakrabarty, “Design of System-on-a-Chip Test Access Architecture under Place-and-Route and Power Constraints, ” in Proceedings of ACM/IEEE Design Automation Conference. (DAC), Los Angeles, CA, June 2000, pp. 432–437.

K. Chakrabarty, “Test Scheduling for Core-Based Systems Using Mixed-Integer Linear Programming, ” IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 19, no. 10, pp. 1163–1174, Oct. 2000.

K. Chakrabarty, “Optimal Test Access Architectures for System-on-a-Chip, ” ACM Trans. on Design Automation of Electronic Systems, vol. 6, pp. 26–49, Jan. 2001.

R. Chou, K. Saluja, and V. Agrawal, “Scheduling Tests for VLSI Systems Under Power Constraints, ” IEEE Transactions on VLSI Systems, vol. 5, no. 2, pp. 175–185, June 1997.

G.L. Craig, C.R. Kime, and K.K. Saluja, “Test Scheduling and Control for VLSI built-in-self-test, ” IEEE Transactions on Computers, vol. 37, no. 9, pp. 1099–1109, Sept. 1988.

M. Garg, A. Basu, T.C. Wilson, D.K. Banerji, and J.C. Majithia, “A New Test Scheduling Algorithm for VLSI Systems, ” in Proceedings of the CSI/IEEE Symposium on VLSI Design, New Delhi, India, Jan. 1991, pp. 148–153.

S. Gerstendorfer and H.-J. Wunderlich, “Minimized Power Consumption for Scan-Based BIST, ” in Proceedings of IEEE International Test Conference (ITC), Atlantic City, NJ, Sept. 1999, pp. 77–84.

G. Hetherington, T. Fryars, N. Tamarapalli, M. Kassab, A. Hassan, and J. Rajski, “Logic BIST for Large Industrial Designs: Real Issues and Case Studies, ” in Proceedings of IEEE International Test Conference (ITC), Atlantic City, NJ, September 1999, pp. 358–367.

IEEE P1500 Web site. http://grouper.ieee.org/groups/1500.

V. Iyengar and K. Chakrabarty, “Precedence-Based, Preemptive, and Power-Constrained Test Scheduling for System-on-a-Chip, ” in Proceedings of IEEE VLSI Test Symposium (VTS), Marina Del Rey, CA, April 2001, pp. 368–374.

S. Kirkpatrick, C. Gelatt, and M. Vecchi, “Optimisation by Simulated Annealing, ” Science, vol. 220, no. 4598, pp. 671–680, 1983.

E. Larsson, “An Integrated System-Level Design for Testability Methodology. ” Ph. D. Thesis no. 660, Linköpings Universitet, Sweden 2000.

E. Larsson and Z. Peng, “An Integrated System-On-Chip Test Framework, ” in Proceedings of the Design, Automation and Test in Europe Conference (DATE), Munchen, Germany, March 2001, pp. 138–144.

E. Larsson, Z. Peng, and G. Carlsson, “The Design and Optimization of SOC Test Solutions, ” in Proceedings of IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Jose, CA, Nov. 2001, pp. 523–530.

E.J. Marinissen, R. Arendsen, G. Bos, H. Dingemanse, M. Lousberg, and C. Wouters, “A Structured and Scalable Mechanism for Test Access to Embedded Reusable Cores, ” in Proceedings of IEEE International Test Conference (ITC), Washington, DC, Oct. 1998, pp. 284–293.

E.J. Marinissen, S.K. Goel, and M. Lousberg, “Wrapper Design for Embedded Core Test, ” in Proceedings of IEEE International Test Conference (ITC), Atlantic City, NJ, Oct. 2000, pp. 911–920.

E.J. Marinissen, Y. Zorian, R. Kapur, T. Taylor, and L. Whetsel, “Towards a Standard for Embedded Core Test: An Example, ” in Proceedings of IEEE International Test Conference (ITC), Atlantic City, NJ, Sept. 1999, pp. 616–627.

V. Muresan, X. Wang, V. Muresan, and M. Vladutiu, “AComparison of Classical Scheduling Approaches in Power-Constrained Block-Test Scheduling, ” in Proceedings of IEEE International Test Conference (ITC), Atlantic City, NJ, Oct. 2000, pp. 882–891.

M. Nourani and C. Papachristou, “An ILP Formulation to Optimize Test Access Mechanisms in System-on-a-Chip Testing, ” in Proceedings of IEEE International Test Conference (ITC), Atlantic City, NJ, Oct. 2000, pp. 902–910.

M. Sugihara, H. Date, and H. Yasuura, “A Test Methodology for Core-Based System LSIs, ” IEICE Transactions on Fundamentals, vol. E81-A, no. 12, Dec. 1998, pp. 2640–2645.

N. Weste and K. Eshraghian, Principles of CMOS VLSI Design, Addison-Wesley, 1993.

Y. Zorian, “A Distributed BIST Control Scheme for Complex VLSI Devices, ” in Proceedings of the IEEE VLSI Test Symposium (VTS), Atlantic City, NJ, April 1993, pp. 4–9.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Larsson, E., Peng, Z. An Integrated Framework for the Design and Optimization of SOC Test Solutions. Journal of Electronic Testing 18, 385–400 (2002). https://doi.org/10.1023/A:1016589322936

Issue Date:

DOI: https://doi.org/10.1023/A:1016589322936