Abstract

Floating-point (FP) multipliers are the main energy consumers in many FP applications. Recently several FP multipliers with multiple- precision modes have been designed to trade energy consumption with output accuracy of FP multiplication operation (MOP). To effectively apply these multi-mode multipliers to FP applications, this paper presents a fast instruction precision assignment method for reducing energy consumption under accuracy and performance constraints. To easily set and check the accuracy constraint, we first build an affine arithmetic based error model to evaluate the overall output accuracy loss caused by inaccurate FP MOPs. Moreover, a simplified instruction scheduling method is also developed to quickly check the performance constraint. Based on these two check functions and the characteristics of proposed multi-mode multiplier, a fast Tabu search (TS) algorithm is then proposed to assign the precision mode of each FP MOP under the accuracy and performance constraints imposed on the given application. Experimental results show that the proposed fast TS algorithm can find the precision assignment with more energy saving and less searching time when compared to previous methods.

Similar content being viewed by others

References

Janhunen J., Pitkanen T., Silven O., Juntti M.: Fixed- and floating-point processor comparison for MIMO-OFDM detector. IEEE J. Sel. Top. Signal Process. 5(8), 1588–1598 (2011)

Amaricai A., Boncalo O., Gavriliu C.-E.: Low-precision DSP-based floating-point multiply-add fused for field programmable gate arrays. IET Comput. Digit. Tech. 8(4), 187–197 (2014)

Pu, Y.; Ha, Y.: An automated efficient and static bit-width optimization methodology towards maximum bit-width-to-error tradeoff with affine arithmetic model. In: Proceedings of the Asia and South Pacific Design Automation Conference, pp. 24–27 (2006)

Lee D.U., Gaffar A.A., Cheung R.C.C., Mencer O., Luk W., Constantinides G.A.: Accuracy-guaranteed bit-width optimization. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 25(10), 1990–2000 (2006)

Osborne, W.G.; Cheung, R.C.C.; Coutinho, J.; Luk, W.; Mencer, O.: Automatic accuracy-guaranteed bit-width optimization for fixed and floating-point systems. In: International Conference on Field Programmable Logic and Applications, pp. 617–620 (2007)

Fang, F.C.; Tsuhan, C.; Rutenbar, R.A.: Floating-point bit-width optimization for low-power signal processing applications. In: IEEE International Conference on Acoustics, Speech, and Signal Processing, pp. 3208–3211 (2002)

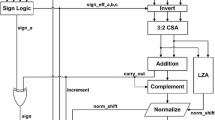

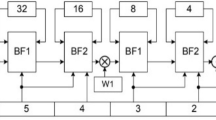

Tan D., Lemonds C.E., Schulte M.J.: Low-power multi-precision iterative floating-point multiplier with SIMD support. IEEE Trans. Comput. 58(2), 175–187 (2009)

Wu K.-Y., Kuang S.-R., Yu K.-K.: An exact method for estimating maximum errors of multi-mode floating-point iterative booth multiplier. Int. J. Comput. Sci. Eng. 8(4), 306–315 (2013)

Kuang S.-R., Wu K.-Y., Yu K.-K.: Energy-efficient multiple-precision floating-point multiplier for embedded applications. J. Signal Process. Syst. 72(1), 43–55 (2013)

Wu, K.-Y.; Liang, C.-Y.; Yu, K.-K.; Kuang, S.-R.: Multiple-mode floating-point multiply-add fused unit for trading accuracy with power consumption. In: IEEE/ACIS 12th International Conference on Computer and Information Science (ICIS), pp. 429–435 (2013)

Chang, M.L.; Hauck, S.: Precis: a design-time precision analysis tool. In: The 10th Annual IEEE Symposium on Field-Programmable Custom Computing Machines, pp. 229–238 (2002)

Pool, J.; Lastra, A.; Singh, M.: Energy-precision tradeoffs in mobile graphics processing units. In: IEEE International Conference on Computer Design, pp. 60.-67 (2008)

Rendell, A.P.; Clarke, B.; Janes, P.; Milthorpe, J.; Rui Yang: Interval arithmetic and computational science: rounding and truncation errors in N-body methods. In: International Conference on Computational Science and Its Applications, pp. 457–466 (2007)

Qi, M.Y.; Miao, L.X.; Zhang, L.; Xu, H.T.: A new Tabu Search heuristic algorithm for the vehicle routing problem with time windows. In: International Conference on Management Science and Engineering, pp. 1648–1653 (2008)

James T., Rego C., Glover F.: Multistart tabu search and diversification strategies for the quadratic assignment problem. IEEE Trans. Syst. Man Cybern. A Syst. Hum. 39(3), 579–596 (2009)

Stephen D.S., Somasundaram P.: Solution for multi-objective reactive power optimization using fuzzy guided tabu search. Arab. J. Sci. Eng. 37(8), 2231–2241 (2012)

Bahrepour D., Sharifi M.J.: A novel high speed full adder based on linear threshold gate and its application to a 4-2 compressor. Arab. J. Sci. Eng. 38(11), 3041–3050 (2013)

Fang, F.C.; Tsuhan, C.; Rutenbar, R.A.: Floating-point error analysis based on affine arithmetic. In: IEEE International Conference on Acoustics, Speech, and Signal Processing, pp. 561–564 (2003)

Vakili, S.; Langlois, J.M.P.; Bois, G.: Finite-precision error modeling using affine arithmetic. In: IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP), pp. 2591–2595 (2013)

Shou H.H., Lin H.W., Ralph R.M., Wang G.J.: Modified affine arithmetic in tensor form for trivariate polynomial evaluation and algebraic surface plotting. J. Comput. Appl. Math. 195(1-2), 155–171 (2006)

Lee R.C.T., Tseng S.S., Chang R.C., Tsai Y.T.: Introduction to the design and analysis of algorithms: a strategic approach. McGraw Hill, New York (2005)

Andrel A., Schmitz M., Eles P., Peng Z., Al-Hashimi B.M.: Overhead-conscious voltage selection for dynamic and leakage energy reduction of time-constrained systems. IEE Proc. Comput. Digit. Tech. 152(1), 28–38 (2005)

Haqras, T.; Janecek, J.: A high performance, low Complexity algorithm for compile-time job scheduling in homogenous computing environments. In: International Conference on Parallel Processing Workshops, pp. 149–155 (2003)

Tsubakitani S., Evans J.R.: Optimizing tabu list size for the traveling salesman problem. Comput. Oper. Res. 194(1), 341–363 (2012)

Pais T.C., Amaral P.: Managing the tabu list length using a fuzzy inference system: an application to examination timetabling. Ann. Oper. Res. 25(2), 91–97 (1998)

Cantin, M.A.; Savaria, Y.; Lavoie, P.: A comparison of automatic word length optimization procedures. In: IEEE International Symposium on Circuits and Systems (ISCAS 2002), vol. 2, pp. 612–615 (2002)

del Barrio, V.M.; Gonzalez, C.; Roca, J.; Fernandez, A.; Espasa, R.: ATTILA: a cycle-level execution-driven simulator for modern GPU architectures. In: IEEE International Symposium on Performance Analysis of Systems and Software, pp. 231–241 (2006)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kuang, SR., Wu, KY. Low-Energy Instruction Precision Assignment for Multi-mode Multiplier Under Accuracy and Performance Constraints. Arab J Sci Eng 40, 787–798 (2015). https://doi.org/10.1007/s13369-014-1539-z

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13369-014-1539-z