Abstract

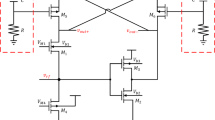

This paper proposes a design methodology for ultra-low-power CMOS radiofrequency (RF) transceivers building blocks. The key parameters of this methodology are the inversion coefficient of CMOS transistor and the extracted equations of passives components introduced in the architecture of the RF building block. The approach of proposed methodology consists of a trade-off between the power consumption and the others RF parameters such as gain, linearity, noise and bandwidth. Two analog RF design examples have been studied in details in order to clarify the design flow and effectiveness of the proposed methodology. A down-conversion mixer and a voltage-controlled oscillator have been implemented in CMOS technology; the obtained results have been compared to others of the state of the art.

Similar content being viewed by others

References

Vittoz E.A.: Sub-threshold Design for Ultra Low-Power Systems. Springer, Berlin (2006)

Rafei M., Mosavi M.R.: A new 0.25–12.5 GHz high quality factor low-power active inductor using local RC feedback to cancel series-loss resistance. Arab. J. Sci. Eng. 38(11), 3125–3132 (2013)

Kaya A., Coskun O.: Single-pole double-throw switches for 2.4 GHz transceiver in wireless communication applications. Arab. J. Sci. Eng. 38(12), 3421–3427 (2013)

ZigBee Alliance, www.zigbee.org, accessed July 2013

Silveira F., Flandre D., Jespers P.G.A.: A gm/ID based methodology for the design of CMOS analog circuits and ist application to the synthesis of a silicon-on-insulator micropower OTA. IEEE J. Solid-State Circuits 31(9), 1314–1319 (1996)

Jespers P.: The gm/ID Methodology a Sizing Tool for Low-Voltage Analog CMOS Circuits: The Semi-empirical and Compact Model Approaches. 1st edn. Springer, Berlin (2009)

Hsieh, H-H.; Lu, L-H.: Design of ultra-low-voltage RF frontends with complementary current-reused architectures. IEEE Trans. Microw. Theory Tech. 55(7) (2007)

Otis, B.P.; Rabaey, J.: Ultra-Low Power Wireless Technologies for Sensor Networks. Springer, (2007)

Al-Absi M.A.: Low voltage and low power current-mode divider and 1/X circuit using MOS transistor in subthreshold. Arab. J. Sci. Eng. 38(9), 2411–2414 (2013)

Binkley D.M.: Tradeoffs and Optimization in Analog CMOS Design. Wiley, New York (2008)

Faitah, K.; El Oualkadi, A.; Ait Ouahman, A.: CMOS RF down-conversion mixer design for low-power wireless Communications. ACM Ubiquity 9(24) (2008)

Terrovitis M.T., Meyer R.G.: Intermodulation distortion in current-commutating CMOS mixers. IEEE J. Solid-State Circuits 35(10), 1461–1473 (2000)

Zoka, N.; Kargaran, E.; Nabovate, G.; Nabovatil, H.: An ultra low-voltage, ultra low-power CMOS mixer using the body effect. IEEE 54th International Midwest Symposium on Circuits and Systems (MWSCAS) (2011)

Mollaalipour, M.; Miar-Naimi, H.: An improved high linearity active CMOS mixer design and Volterra series analysis. IEEE Trans. Circuits Syst. 60(8) (2013)

Lee, W.C.; Tsang, K.F.; Shen, Y.; Chui, K.T.: a current bleeding CMOS mixer featuring LO amplification based on current-reused topology. Circuit Syst. Sci. Res. J. 4(1), 58–66 (2013)

Razavi B.: Design of Analog CMOS Circuit. McGraw-Hill, NY (2000)

Lee T., Hajimiri A.: Oscillator phase noise: a tutorial. IEEE J. Solid-State Circuits 35(3), 326–336 (2000)

Fathi, D.; Nejad, A.G.: Ultra-low power, low phase noise 10 GHz LC VCO in the subthreshold regime. Circuit Syst. Sci. Res. J. (2013)

Lee K.K., Bryant C., Törmänen M., Sjöland H.: Design and analysis of an ultra-low-power LC quadrature VCO. Analog Integr. Circuits Signal Process. 67(1), 49–60 (2011)

Dongmin P., SeongHwan C.: Design techniques for a low-voltage VCO with wide tuning range and low sensitivity to environmental variations. IEEE Trans. Microw. Theory Tech. 57(4), 767–774 (2009)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ouali, A.I., El Oualkadi, A., Moussaoui, M. et al. Design Optimization Methodology Based on Inversion Coefficient Parameter for CMOS RF Circuits. Arab J Sci Eng 39, 8935–8946 (2014). https://doi.org/10.1007/s13369-014-1429-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s13369-014-1429-4