Abstract

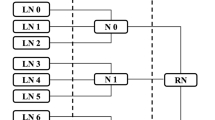

In this paper, we present a general approximation for 2D filters by using only power-of-two terms. This enables to easily implement these filters in electronic devices such as FPGA and ASIC just by using simple hardware shifters and adders/subtractors. Consequently, no division and no multiplication operators are required, which can reduce the memory and the power needed for computing operations such as convolution. Instead of using only additions and power-of-two terms for representing a number like in the standard binary decomposition, our model also uses subtractions for representing and approximating numbers. In addition, we propose a binary tree structure for computing a minimal representation in power-of-two terms in such a way that hardware shifters used for performing a convolution with a low-pass filter for example are well reduced to their minimum. Based on some experiments performed for contrast enhancement, which is a common image processing operation, we have noticed that good results can be obtained using our approximation in terms of image quality, hardware resources, and power consumption when compared to some other binary representations.

Similar content being viewed by others

References

Acharya, K.A., Babu, R.V., Vadhiyar, S.S.: A real-time implementation of SIFT using GPU. J. Real-Time Image Proc. (2014). doi:10.1007/s11554-014-0446-6

Wong, T.S., Bouman, C.A., Pollak, I.: Image enhancement using the hypothesis selection filter: theory and application to JPEG decoding. IEEE Trans. Image Process. 22(3), 898–913 (2013)

Barina, D., Zemcik, P.: Vectorization and parallelization of 2-D wavelet lifting. J. Real-Time Image Proc. (2015). doi:10.1007/s11554-015-0486-6

Ofili, C.A., Glozman, S., Yadid-Pecht, O.: Hardware implementation of an automatic rendering tone mapping algorithm for wide dynamic range display. J. Low Power Electron. Appl. 3(4), 337–367 (2013)

Tsai, C.Y.: A fast dynamic range compression with local contrast preservation algorithm and its application to real-time video enhancement. IEEE Trans. Multimed. 14(4), 1140–1152 (2012)

Yu, W.W.H., Xing, S.: Fixed-point multiplier evaluation and design with FPGA. In: Proceedings of SPIE—The International Society for Optical Engineering, vol. 3844, pp. 153–161 (1999)

Kuang, S.R., Wang, J.P.: Design of power-efficient configurable Booth multiplier. IEEE Trans. Circuits Syst. 57(3), 568–580 (2010)

Chen, J., Chang, C.H., Feng, F., Ding, W., Ding, J.: Novel design algorithm for low complexity programmable FIR filters based on extended double base number system. IEEE Trans. Circuits Syst. I Regul. Pap. 62(1), 224–233 (2015)

Baudin, R., Lesthievent, G.: Design of FIR filters with sum of power-of-two representation using simulated annealing. In: 7th Advanced Satellite Multimedia Systems Conference and the 13th Signal Processing for Space Communications Workshop (ASMS/SPSC), pp. 339–345 (2014)

Kang, H.-J., Park, I.-C.: FIR filter synthesis algorithms for minimizing the delay and the number of adders. IEEE Trans. Circuits Syst. II Analog Digit. Signal Proc. 48(8), 770–777 (2001)

Petrlik, J., Sekanina, L.: Multiobjective evolution of approximate multiple constant multipliers. In: IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), pp. 116–119 (2013)

Hsiao, P.Y., Chen, C.H., Chou, S.S., Li, L.T., Chen, S.J.: A parameterizable digital-approximated 2D Gaussian smoothing filter for edge detection in noisy image. In: IEEE International Symposium on Circuits and Systems, pp. 3189–3192 (2006)

Chiu, C.T., Wang, T.H., Ke, W.M., Chuang, C.Y., Huang, J.S., Wong, W.S., Tsay, R.S., Wu, C.J.: Real-time tone-mapping processor with integrated photographic and gradient compression using 0.13 µm technology on an Arm Soc platform. J. Signal Proc. Syst. 64(1), 93–107 (2011)

Gustafsson, O.: Lower bounds for constant multiplication problems. IEEE Trans. Circuits Syst. II 54(11), 974–978 (2007)

Parhami, B.: Generalized signed-digit number systems: a unifying framework for redundant number representations. IEEE Trans. Comput. 39(1), 89–98 (1990)

Sawada, J.: A simple gray code to list all minimal signed binary representations. SIAM J. Discrete Math. 21(1), 16–25 (2007)

Wu, T., Zhang, M., Du, H.Q., Wang, R.B.: On optimal binary signed digit representations of integers. Appl. Math. A J. Chin Univ. 25(3), 331–340 (2010)

Ebeid, N., Hasan, M.A.: On binary signed digit representations of integers. Des. Codes Crypt. 42(1), 43–65 (2007)

Guo, Z., Xu, W., Chai, Z.: Image edge detection based on FPGA. In: International Symposium on Distributed Computing and Applications to Business Engineering and Science, pp. 169–171 (2010)

Wang, Z., Bovik, A.C., Sheikh, H.R., Simoncelli, E.P.: Image quality assessment: from error visibility to structural similarity. IEEE Trans. Image Process. 13(4), 600–612 (2004)

Horé, A., Ziou, D.: Image quality metrics: PSNR vs. SSIM. In: International Conference on Pattern Recognition (ICPR), pp. 2366–2369 (2010)

Acknowledgments

The completion of this research was made possible thanks to the Natural Sciences and Engineering Research Council of Canada (NSERC) and the Alberta Informatics Circle of Research Excellence (iCORE)/Alberta Innovates—Technology Futures (AITF).

Author information

Authors and Affiliations

Corresponding author

Appendices

Appendix 1: Computation of the derivation tree

Appendix 2: Finding the minimal decomposition

Appendix 3: Minimal decompositions of the numbers used in Fig. 6

Rights and permissions

About this article

Cite this article

Horé, A., Yadid-Pecht, O. On the design of optimal 2D filters for efficient hardware implementations of image processing algorithms by using power-of-two terms. J Real-Time Image Proc 16, 429–457 (2019). https://doi.org/10.1007/s11554-015-0550-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11554-015-0550-2