Abstract

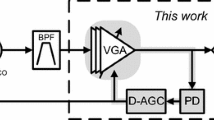

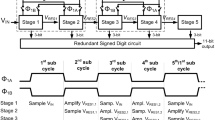

This paper proposes a 10-bit 100 MS/s 20 MHz low power pipelined analog-to-digital converter (ADC) with switched capacitor based programmable gain amplifier (PGA) suitable for wireless receiver applications. In the proposed ADC the double loading problem caused in the first stage of 10-bit pipelined ADC is avoided. In order to minimize the power consumption, split-capacitor sharing correlated double sampling and op-amp sharing technique has been used. Using the technique, low-gain operational amplifiers (op-amps) can be employed to implement a low-power pipelined ADC. Switched capacitor topology based PGA occupies an area of 0.0031 mm2. Switched capacitor topology based PGA with the integration of 10-bit pipelined ADC consumes 25.54 mW of power at 100 MS/s from a 1.8 V power supply.

Similar content being viewed by others

References

Nagaraj, K., Singhal, K., Viswauathan, T. R., & Vlach, J. (2005). Reduction of the finite gain effect in switched-capacitor filters. Electronics Letters, 21, 644–645.

Li, J., & Moon, U. K. (2004). A 1.8 V 67 mW 10-bit 100-MS/s pipelined ADC using time-shifted CDS technique. IEEE Journal of Solid-State Circuits, 39(9), 1468–1476.

Gregoire, B. R., & Moon, U. K. (2008). An over-60 dB true rail-to-rail performance using correlated level shifting and an op-amp with only 30 dB loop gain. IEEE Journal of Solid-State Circuits, 43(12), 2620–2630.

Koo, Y.-J., Li, J., Lee, B. & Moon, U.-K. (2007). Low-power and high-speed pipelined ADC using time-aligned CDS technique. In IEEE custom intergrated circuits conference (CICC) (pp. 321–324)

Lin, J.-F., Chang, S.-J., Liu, C.-C., & Huang, C.-H. (2010). A 10-bit 60 MS/s low power pipelined ADC with split capacitor CDS technique. IEEE Transactions on Circuits and Systems II, Express Briefs, 57(3), 163–167.

Waltari, M., & Halonen, K. A. I. (2001). 1-V 9-bit pipelined switched-op-amp ADC. IEEE Journal of Solid-State Circuits, 36(1), 129–134.

Nagaraj, K., Fetterman, H. S., Anidjar, J., Lewis, S. H., & Renninger, R. G. (1997). A 250-mW, 8-b, 52-Msample/s parallel-pipelined A/D converter with reduced number of amplifiers. IEEE Journal of Solid-State Circuits, 32(3), 312–320.

Kim, H.-C., Jeong, D.-K., & Kim, W. (2006). A partially switched-op-amp technique for high-speed low-power pipelined analog-to-digital converters. IEEE Transactions Circuits Systems I, Regular Papers, 53(4), 795–801.

Chiu, Y., Gray, P. R., & Nikolic, B. (2004). A 14-b 12-MS/s CMOS pipeline ADC with over 100-dB SFDR. IEEE Journal of Solid-State Circuits, 39(12), 2139–2151.

Yu, P. C., & Lee, H.-S. (1996). 2.5-V, 12-b, 5-Msamples/s pipelined CMOS ADC. IEEE Journal of Solid-State Circuits, 31(12), 1854–1861.

Ryu, S.-T., Song, B.-S., & Bacrania, K. (2007). A 10-bit 50-MS/s pipelined ADC with op-amp current reuse”. IEEE Journal of Solid-State Circuits, 42(3), 475–485.

Kim, M.-Y., Kim, J., Lee, T., & Kim, C. (2008). 10-bit 100MS/s CMOS pipelined A/D converter with 0.59 pJ/conversion-step. In IEEE Asian solid-state circuits conference (pp. 65–68).

Li, Jian, Zeng, Xiaoyang, Xie, Lei, Chen, Jun, Zhang, Jianyun, & Guo, Yawei. (2008). A 1.8-V 22-mW 10-bit 30-MS/s pipelined CMOS ADC for low-power sub-sampling applications. IEEE Journal of Solid-State Circuits, 43(2), 321–329.

Lee, Byung-Geun, Min, Byung-Moo, Manganaro, Gabriele, & Valvano, Jonathan W. (2008). A 14-b 100-MS/s pipelined ADC with a merged SHA and first MDAC. IEEE Journal of Solid State Circuits, 43(12), 2613–2619.

Wang, Z., Wang, M., Gu, W., Chen, C., Ye, F., & Ren, J. (2013). A high-linearity pipelined ADC with Op-amp split-sharing in a combined front-end of S/H and MDAC1. IEEE Transactions on Circuits and Systems, 60(11), 2834–2844.

Woo, J.-K., Lee, H., Kim, H.-C., Jeong, D.-K., & Kim, S. (2014). 1.2 V 10-bit 75 MS/s pipelined ADC with phase-dependent gain-transition CDS. IEEE Transactions on VLSI Systems, 22(3), 585–592.

Shylu, D. S., & Jackuline Moni, D. (2012). Design of 10 bit 60 MSPS low power pipelined ADC. CiiT International Journal of Programmable Devices Circuits and Systems, 14(4), 741–746.

Behnoosh Rahmatian and Shahriar Mirabbasi. (2007). A low-power 75 dB digitally programmable variable-gain amplifier in 0.18 μm CMOS. Canadian Journal of Electrical and Computer Engineering, 32(4), 181–186.

Ta, C. M., Yong, C. H., Yeoh, W. G. (2005). A 2.7 mW, 0.064 mm2 linear-in-dB VGA with 60 dB tuning range, 100 MHz bandwidth, and two DC offset cancellation loops. In: IEEE international workshop on radio-frequency integration technology (pp. 74–77).

Hsu, C.-C., & Wu, J.-T. (2002). A 125 MHz-86 dB IM3 programmable-gain amplifier. In Symposium on VLSl circuits digest of technical papers, (pp. 32–35).

Hsu, C.-C., & Wu, J.-T. (2003). A highly linear 125-MHz CMOS switched-resistor programmable-gain amplifier. IEEE Journal of Solid-State Circuits, 38(10), 1663–1670.

Nguyen, H.-H., Nguyen, H.-N., Lee, J.-S., & Lee, S.-G. (2009). A binary-weighted switching and reconfiguration-based programmable gain amplifier. IEEE Transactions on Circuits and Systems, 56(9), 699–703.

Kuo, C.-H., Kuo, T.-H., & Wen, K.-L. (2010). Bias-and-input interchanging technique for cyclic/pipelined ADCs With opamp sharing. IEEE Transactions on circuits and systems-II, 57(3), 168–172.

Miki, Takuji, Morie, Takashi, Ozeki, Toshiaki, & Dosho, Shiro. (2012). An 11-b 300-MS/s double-sampling pipelined ADC with on-chip digital calibration for memory effects. IEEE Journal of Solid-State Circuits, 47(11), 2773–2782.

Shylu, D. S., Jackuline, D., Neenu, M., & Francis, B. (2014). Design and analysis of low power pseudo differential class-AB telescopic operational amplifier. International Journal of Research in Engineering and Technology (IJRET), 3(7), 243–248.

Sumanen, L., Waltari, M., Hakkarainen, V., & Halonen, K. (2002). CMOS dynamic comparators for pipeline A/D converters. IEEE International Symposium on Circuits and Systems, 5, V-157–V-160.

Agrez, D. (2007). Reduction of the conversion time of the non-uniform differential tracking A/D converter. In IMTC 2007-instrumentation and measurement technology conference Warsaw, Poland, (Vol. 1–3, pp. 1–4).

Acknowledgments

The authors are grateful to the management of Karunya University for providing necessary facilities in VLSI laboratory to carryout this research work. The authors would like to thank Ms. Anitha, Ms. Neenu for their help in working with the CADENCE software tool.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Shylu, D.S., Moni, D. & Nivetha, G. Design and Power Optimization of High-Speed Pipelined ADC with Programmable Gain Amplifier for Wireless Receiver Applications. Wireless Pers Commun 90, 657–678 (2016). https://doi.org/10.1007/s11277-016-3186-z

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-016-3186-z