Abstract

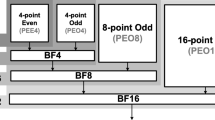

In this study, a novel fast algorithm based hardware-sharing architecture for 4 × 4, 8 × 8, 16 × 16, and 32 × 32 inverse core transforms in high-efficiency video coding (HEVC) with a cost effective and highly hardware efficient design is developed. By using the symmetrical characteristics of the elements in inverse core transform matrices, the core transform matrix with symmetrical characteristics is factorized into several submatrices. Based on the symmetry and similarity between the submatrices, the hardware of the (N/2) × (N/2) inverse core transform is shared with that of the N × N inverse core transform for N = 32, 16, and 8. Compared with each transform design without hardware shares, the proposed multiplierless transform architecture reduces the hardware overheads of adders and shifters by 32 and 36 %, respectively. The hardware efficiency of the proposed architecture is up to 166 % higher than that of several previous transform designs for HEVC, and up to 141 % higher than that of field-programmable gate array (FPGA)-based 16-point transform designs. Because it uses 90-nm complimentary metal-oxide semiconductor (CMOS) technology produced by the Taiwan Semiconductor Manufacturing Company (TSMC), the proposed 1-D hardware sharing scheme requires 115.7 K gate counts to achieve an operational frequency of up to 200 MHz, and it can decode 4 × 2 K (4096 × 2048 pixels) and 8 K UHDTV (7680 × 4320 pixels) video in real time at up to 127 and 32 frames per second, respectively.

Similar content being viewed by others

References

Draft ITU-T. (2003). Recommendation and final draft international standard of joint video specification (ITU-T Rec. H.264/ISO/IEC 14496–10 AVC).

ISO/IEC 11172–2 MPEG-1. (1993). Video coding standard, information technology - coding of moving pictures and associated audio for digital storage media at up to about 1,5 Mbit/s - part 2: video.

ISO/IEC 13818–2 MPEG-2. (1995). Video coding standard, information technology - generic coding of moving pictures and associated audio information: video.

ISO/IEC 14496–2. (1997). Coding of audio-visual objects – part2: visual.

SMPTE. (2006). Standard for Television: VC-1 Compressed Video bitstream format and decoding process. SMPTE 421M-2006.

Pourazad, M. T., Doutre, C., Azimi, M., & Nasiopoulos, P. (July 2012). HEVC : The New Gold Standard for Video Compression: How Does HEVC Compare with H.264/AVC ? IEEE Consumer Electronics Magazine, 1, 36–46.

Sullivan, G. J., Ohm, J., Han, W. J., & Wiegand, T. (December 2012). Overview of the High Efficiency Video Coding (HEVC) Standard. IEEE Transactions on Circuits and Systems for Video Technology, 22, 1649–1668.

Bossen, F., Bross, B., Suhring, K., & Flynn, D. (December 2012). HEVC Complexity and Implementation Analysis. IEEE Transactions on Circuits and Systems for Video Technology, 22, 1685–1696.

Shen, S., Shen, W., Fan, Y., Zeng, X. (2012). A unified 4/8/16/32-point integer IDCT architecture for multiple video coding standards. IEEE International Conference on Multimedia and Expo (ICME). pp. 788–793.

Ahmed, A., Shahid, M. U., Rehman, A. (2012). N Point DCT VLSI Architecture for Emerging HEVC Standard. VLSI Design, volume 2012, Article ID 752024, pp.1–13.

Joint Collaborative Team – Video Coding. (2011). CE10: core transform design for HEVC. JCTVC-G495, Geneva, Switzerland, 21–30.

Haggag, M. N., El-Sharkawy, M., Fahmy, G. (2010). Efficient fast multiplication-free integer transformation for the 2-D DCT H.265 Standard. IEEE International Conference on Image Processing. pp. 3769–3772

Dong, J., Ngan, K. N., Fong, C. K., & Cham, W. K. (October 2009). 2-D Order-16 Integer Transforms for HD Video Coding. IEEE Transactions on Circuits and Systems for Video Technology, 19, 1462–1474.

Jeske, R., C. de Souza, J., Wrege, G., Conceicao, R., Grellert, M., Mattos, J., Agostini, L. (2012). Low cost and high throughput multiplierless design of a 16 point 1-D DCT of the new HEVC Video Coding Standard. Conference on Programmable Logic (SPL). pp.1–6.

Zhao, W., Onoye, T., Song, T. (2013). High-performance multiplierless transform architecture for HEVC. IEEE International Symposium on Circuits and Systems (ISCAS). pp.1668–1671.

Martuza, M., Wahid, K. A. (2012). Implementation of a cost shared transform architecture for multiple video Codecs. Journal of Real-Time Image Processing.

Horn, R.A., Johnson, C.R. (1991). Topics in matrix analysis, Cambridge University Press.

Acknowledgments

This work was supported by the Ministry of Science and Technology, Taiwan, R.O.C., under grant number MOST 102-2220-E-005-003. The authors thank the National Chip Implementation Center in Taiwan for EDA tool support, and also thank the anonymous referees whose careful reviews and detailed comments helped to improve the readability of this paper.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chang, CW., Hsu, HF., Fan, CP. et al. A Fast Algorithm-Based Cost-Effective and Hardware-Efficient Unified Architecture Design of 4 × 4, 8 × 8, 16 × 16, and 32 × 32 Inverse Core Transforms for HEVC. J Sign Process Syst 82, 69–89 (2016). https://doi.org/10.1007/s11265-015-0982-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-015-0982-8