Abstract

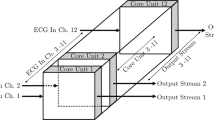

There is increasing research and commercial interest in miniature on-body and implantable devices for continuous real-time biosignal monitoring. A key challenge in realizing this vision is in implementation of biosignal processing algorithms with acceptably low energy consumption. In this article, we investigate implementation of the REACT algorithm for real-time epileptic seizure detection on a Coarse Grained Reconfigurable Array (CGRA) based architecture. Computationally expensive biosignal processing tasks are offloaded from a conventional Digital Signal Processor (DSP) to the CGRA. The CGRA is designed to support low power biosignal processing by means of a systolic architecture, flexible interconnect and low resource usage. The CGRA architecture is shown to provide 38% and 60% improvements in energy consumption and in performance, respectively, for the REACT system, without the use of voltage scaling or increased clock frequency.

Similar content being viewed by others

References

Sander, J., & Shorvon, S. (1987). Incidence and prevalence studies in epilepsy and theirmethodological problems: a review. Journal of Neurology Neurosurgery & Psychiatry, 50(7), 829–839.

Waterhouse, E. (2003). New horizons in ambulatory electroencephalography. IEEE Engineering in Medicine and Biology Magazine, 22(3), 74–80.

Patel, K., Chua, C.P., Faul, S., & C. J. Bleakley (2009). Low power real-time seizure detection for ambulatory EEG. 3rd International Conference on Pervasive Computing Technologies for Healthcare, pp. 1–7.

Temko, A., McEvoy, R., Dwyer, D., Faul, S., Lightbody, G., & Marnane, W. (2010). REACT: Real time EEG analysis for event detection. Proceedings of the AMA-IEEE Medical Technology Conference on Individualized Healthcare.

Faul, S. (2010). Dynamic channel selection to reduce computational burden in seizure detection. Annual International Conference of the IEEE Engineering in Medicine and Biology Society, pp. 365 –368.

Hartenstein, R. (2001). Coarse grain reconfigurable architecture. Proceedings of the 2001 Conference on Asia South Pacific Design Automation, pp. 564–570.

Faul, S., Boylan, G., Connolly, S., & Lightbody, W.M.G. (2005). An evaluation of automated neonatal seizure detection methods. Clinical Neurophysiology, 116(7), 1533–1541.

Young, C.P., Hsieh, C.-H., & Wang, H.-C. (2009). A low-cost real-time closed-loop epileptic seizure monitor and controller. IEEE Instrumentation and Measurement Technology Conference, pp. 1768 –1772.

Bhavaraju, N., Frei, M., & Osorio, I. (2006). Analog seizure detection and performance evaluation. IEEE Transactions on Biomedical Engineering, 53(2), 238–245.

Temko, A., Korotchikova, I., Marnane, W., Lightbody, G., & Boylan, G. (2010). Validation of an automated seizure detection system on healthy babies. Proceedings of the INSTICC/IEEE International Joint Conference on Biomedical Engineering Systems and Technologies, pp. 312–317.

Faul, S., Temko, A., & Marnane, W. (2009). Age-independent seizure detection. Proceedings of the 31st Annual International Conference of the IEEE Engineering in Medicine and Biology Society, pp. 612–615.

Temko, A., Thomas, E., Boylan, G., Marnane, W., & Lightbody, G. (2009). An SVM-based system and its performance for detection of seizures in neonates. Proceedings of the 31st Annual International Conference of the IEEE Engineering in Medicine and Biology Society, pp. 643–646.

Al Khatib, I., Bertozzi, D., Poletti, F., Benini, L., Jantsch, A., Bechara, M., Khalifeh, H., Hajjar, M., Nabiev, R., & Jonsson, S. (2006). MPSoC ECG biochip: a multiprocessor system-on-chip for real-time human heart monitoring and analysis. Proceedings of the 3rd Conference on Computing Frontiers, pp. 21–28.

Kwong, J., & Chandrakasan, A.P. (2011). An energy-efficient biomedical signal processing platform. IEEE Journal of Solid-State Circuits, 46(7), 1742–1753.

Massagram, W., Hafner, N., Chen, M., Macchiarulo, L., Lubecke, V.M., & Boric-Lubecke, O. (2010). Digital heart-rate variability parameter monitoring and assessment ASIC. IEEE Transactions on Biomedical Circuits and Systems, 4(1), 19–26.

Zhang, X., Jiang, H., Zhang, L., Zhang, C., Wang, Z., & Chen, X. (2010). An energy-efficient ASIC for wireless body sensor networks in medical applications. IEEE Transactions on Biomedical Circuits and Systems, 4 (1), 11–18.

Singh, H., Lee, M.-H., Lu, G., Kurdahi, F., Bagherzadeh, N., & Chaves Filho, E. (2000). MorphoSys: an integrated reconfigurable system for data-parallel and computation-intensive applications. IEEE Transactions on Computers, 49(5), 465–481.

Goldstein, S., Schmit, H., Budiu, M., Cadambi, S., Moe, M., & Taylor, R. (2002). Piperench: A reconfigurable architecture and compiler. Computer, 33(4), 70–77.

Ebeling, C., Cronquist, D., Franklin, P., & Fisher, C. (1996). RaPiD-a configurable computing architecture for compute-intensive applications. University of Washington Department of Computer Science & Engineering Tech Report TR-96-11-03.

Mei, B., Vernalde, S., Verkest, D., De Man, H., & Lauwereins, R. (2003). ADRES: An architecture with tightly coupled VLIW processor and coarse-grained reconfigurable matrix. Lecture Notes in Computer Science, 2778, 61–70.

Park, Y., Park, H., & Mahlke, S. (2009). CGRA express: Accelerating execution using dynamic operation fusion. Proceedings of the International Conference on Compilers, Architecture, and Synthesis for Embedded Systems, pp. 271–280.

Park, H., Park, Y., & Mahlke, S. (2009). Polymorphic pipeline array: a flexible multicore accelerator with virtualized execution for mobile multimedia applications. Proceedings of the 42nd Annual IEEE/ACM International Symposium on Microarchitecture, pp. 370–380.

Sudarsanam, A., Barnes, R., Carver, J., Kallam, R., & Dasu, A. (2010). Dynamically reconfigurable systolic array accelerators: A case study with extended Kalman filter and discrete wavelet transform algorithms. IET Computers Digital Techniques, 4(2), 126–142.

Liang, C., & Huang, X. (2008). SmartCell: A power-efficient reconfigurable architecture for data streaming applications. IEEE Workshop on Signal Processing Systems, pp. 257–262.

Rabaey, J. (2006). A Scalable configurable architecture for advanced wireless communication algorithms. The Journal of VLSI Signal Processing, 45(3), 127–151.

Kim, Y., & Mahapatra, R. (2010). Dynamic context compression for low-power coarse-grained reconfigurable architecture. IEEE Transactions on Very Large Scale Integration Systems, 18(1), 15–28.

EPILEPSIAE. - Evolving Platform for Improving Living Expectation of Patients Suffering from Ictal Events. http://www.epilepsiae.eu/.

McEvoy, R., Faul, S., & Marnane, L. (2010). Ambulatory REACT: Real-time seizure detection with a DSP microprocessor 32nd Annual International Conference of the IEEE Engineering in Medicine and Biology Society, pp. 2443–2446.

Patel, K., McGettrick, S., & Bleakley, C.J. (2011). Rapid functional modelling and simulation of coarse grained reconfigurable array architectures. Journal of Systems Architecture, 57(4), 383–391.

Patel, K., & Bleakley, C. (2010). Systolic algorithm mapping for coarse grained reconfigurable array architectures. Lecture Notes in Computer Science, 5992, 351–357.

Acknowledgment

This research was funded as a part of the Efficient Embedded Digital Signal Processing for Mobile Digital Health (EEDSP) cluster, 07/SRC/I1169, by Science Foundation Ireland (SFI).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Patel, K., Bleakley, C.J. Coarse Grained Reconfigurable Array Based Architecture for Low Power Real-Time Seizure Detection. J Sign Process Syst 82, 55–68 (2016). https://doi.org/10.1007/s11265-015-0981-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-015-0981-9