Abstract

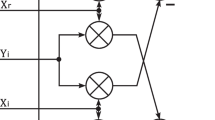

A design technique based on a combination of Common Sub-Expression Elimination and Bit-Slice (CSE-BitSlice) arithmetic for hardware and performance optimization of multiplier designs with variable operands is presented in this paper. The CSE-BitSlice technique can be extended to hardware optimization of multiplier circuits operating on vectors or matrices of variables. The CSE-BitSlice technique has been applied to the design and implementation of 12 × 12 and 42 × 42 bit real multipliers, a complex multiplier, a 6-tap FIR filter, and a 5-point DFT circuit. For comparison purposes, circuit implementations of the same arithmetic and DSP functions have been carried out using Radix-4 Booth and CSA algorithms. Simulation results based on implementations using the Xilinx FPGA 5VLX330FF1760-2 device shows that the circuits based on the CSE-BitSlice techniques require fewer logic resources and yield higher throughput as compared to the CSA and Radix-4 Booth based circuits.

Similar content being viewed by others

References

Pasko, R., Schaumont, P., Derudder, V., Vernalde, V., & Durackova, D. (1999). A new algorithm for elimination of common subexpressions. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 18(1), 58–68.

Macpherson, K. N., & Steward, R. W. (2006). Area efficient FIR filters for high speed FPGA implementation. IEE Proceeding: Vision, Image and Signal Processing, 153(6), 711–720.

Dempster, A. G., & Macleod, M. (1995). Use of minimum-adder multiplier blocks in FIR digital filters. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 42(9), 569–576.

Mirzaei, S., Hosangadi, A., & Kastner, R. (2006). FPGA implementation of high speed FIR filters using add and shift method. Proc. of the 14th Intl. Conference on FPGA FPGA'06, pp. 231–237.

Macleod, M. D., & Dempster, A. G. (2004). Common subexpression elimination algorithm for low-cost multiplierless implementation of matrix multipliers. Electronics Letters, 40(11), 651–652.

Mehendale, M., Sherlekar, S. D., & Vekantesh, G. (1995). Synthesis of multiplierless FIR filters with minimum number of additions. Proceedings of the 1995 IEEE/ACM International Conference on Computer-Aided Design. Los Alamitos CA., pp. 668–671.

Hartley, R. I. (1996). Subexpression sharing in filters using canonic signed digit multipliers. IEEE Transactions Circuits and Systems II, 43, 677–688.

Potkonjak, M., Srivastava, M. B., & Chandrakasan, A. P. (1996). Multiple constant multiplications: efficient and versatile framework and algorithms for exploring common subexpression elimination. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 15(2), 151–165.

Park, I. C., & Kang, H. J. (2002). Digital filter synthesis based on an algorithm to generate all minimal signed digit representations. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 21(12), 1525–1529.

Nguyen, H. T., & Chatterjee, A. (2000). Number-splitting with shift-and-add decomposition for power and hardware optimization in linear DSP synthesis. IEEE Transactions on Very Large Scale Integration Systems, 8(4), 419–424.

Hosangadi, A., Fallah, F., & Kastner, R. (2005). Simultaneous optimization of delay and number of operations in multiplierless implementation of linear systems. Proc. of the 14th Intl. Workshop on Logic and Synthesis IWLS’05.

Wu, Q., Song, Q., & Sun, Y. (2004). A novel algorithm for common subexpression elimination in VLSI implementation of high speed multiplierless FIR filters. Proc. of the 6th IASTED Intl. Conference on Signal and Image Processing SIP’04, pp. 346–350.

Aksoy, L., Gunes, E. O., & Flores, P. (2008). An exact breadth-first search algorithm for the multiple constant multiplications problem. Proc. of the 26th NORCHIP Conf., Nov. 2008, pp. 41–46.

Hwang, K. (1978). Computer arithmetic: Principles, architecture and design. New York: Wiley.

Ercegovac, M. D., & Lang, T. (1990). Fast multiplication without carry propagate addition. IEEE Transactions on Computers, 39, 1385–1390.

Asato, C., Ditzen, C., & Dholakia, S. (1989). A datapath multiplier with automatic insertion of pipeline stages. IEEE Proc. of Custom Integrated Circuits Conference, pp. 23.2.1–23.2.4.

Booth, A. D. (1951). A signed binary multiplication technique. Quarterly Journal of Mechanics and Applied Mathematics, 4(2), 236–240.

McSorley, O. L. (1961). High speed arithmetic in binary computers. Proceedings of the Institute of Radio Engineers, 49(1), 67–91.

Shin, M. C., Kang, S. H., & Park, I. C. (2001). An area-efficient iterative modified-booth multiplier based on self-timed clocking. IEEE Int’l Conf. on Computer, pp. 511–514.

Taylor, F. J. (1984). Residue arithmetic: a tutorial with examples. IEEE Computer Magazine, 17(5), 50–62.

Jenkins, W., & Davidson, E. (1985). A custom-designed integrated circuit for the realization of residue number digital filters. Proc. ICASSP, pp. 220–223.

Mahesh, R., & Vinod, A. P. (2007). An architecture for integrating low complexity and reconfigurability for channel filters in software defined radio receivers. In Proc. IEEE International Symposium on Circuits and Systems, May 2007, pp. 2514–2517.

Muhammad, K., & Roy, K. (2002). Reduced computational redundancy implementation of DSP algorithms using computation sharing vector scaling. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 10(3), 292–300.

Ho, H., Szwarc, V., & Kwasniewski, T. (2007). Hardware optimization of a configurable polyphase-FFT design using common sub-expression elimination. Proc. of the MWSCAS/NEWCAS ‘07, Montreal, Aug. 5–7, 2007.

Quan, G., Davis, J. P., Devarkal, S., & Buell, D. A. (2005). High-level synthesis for large bit–width multipliers on FPGAs: a case study. Proc. of the 3rd IEEE/ACM/IFIP Intl Conference on Hardware/Software Codesign and System Synthesis, pp. 213–218.

Gokul, G., Zhuo, L., Choi, S., & Prasanna, V. (2004). Analysis of high-performance floating-point arithmetic on FPGAs. Proc. of the 18th Parallel and Distributed Processing Symposium IPDPS’04, April 2004, p. 149.

Smith, W. W., & Smith, J. M. (1995). Handbook of real-time fast fourier transforms. Piscataway: IEEE Press.

Xilinx Corporation website, http://www.xilinx.com.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ho, H., Szwarc, V. & Kwasniewski, T. Low Complexity Reconfigurable DSP Circuit Implementations Based on Common Sub-expression Elimination. J Sign Process Syst 61, 353–365 (2010). https://doi.org/10.1007/s11265-010-0458-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-010-0458-9