Abstract

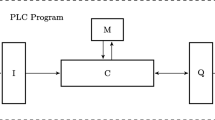

Dataflow descriptions have been used in a wide range of Digital Signal Processing (DSP) applications, such as multi-media processing, and wireless communications. Among various forms of dataflow modeling, Synchronous Dataflow (SDF) is geared towards static scheduling of computational modules, which improves system performance and predictability. However, many DSP applications do not fully conform to the restrictions of SDF modeling. More general dataflow models, such as CAL (Eker and Janneck 2003), have been developed to describe dynamically-structured DSP applications. Such generalized models can express dynamically changing functionality, but lose the powerful static scheduling capabilities provided by SDF. This paper focuses on the detection of SDF-like regions in dynamic dataflow descriptions—in particular, in the generalized specification framework of CAL. This is an important step for applying static scheduling techniques within a dynamic dataflow framework. Our techniques combine the advantages of different dataflow languages and tools, including CAL (Eker and Janneck 2003), DIF (Hsu et al. 2005) and CAL2C (Roquier et al. 2008). In addition to detecting SDF-like regions, we apply existing SDF scheduling techniques to exploit the static properties of these regions within enclosing dynamic dataflow models. Furthermore, we propose an optimized approach for mapping SDF-like regions onto parallel processing platforms such as multi-core processors.

Similar content being viewed by others

References

Eker, J., & Janneck, J. W. (2003). CAL language report, language version 1.0—document edition 1. Electronics Research Laboratory, University of California at Berkeley, Tech. Rep. UCB/ERL M03/48.

Hsu, C., Ko, M., & Bhattacharyya, S. S. (2005). Software synthesis from the dataflow interchange format. In Proceedings of the international workshop on software and compilers for embedded systems (pp. 37–49). Dallas, Texas.

Roquier, G., Wipliez, M., Raulet, M., Janneck, J. W., Miller, I. D., & Parlour, D. B. (2008). Automatic software synthesis of dataflow program: An MPEG-4 simple profile decoder case study. In Proceedings of the IEEE workshop on signal processing systems.

Lee, E. A., & Messerschmitt, D. G. (1987). Synchronous dataflow. Proceedings of the IEEE, 75(9), 1235–1245.

Bhattacharyya, S. S., Leupers, R., & Marwedel, P. (2000). Software synthesis and code generation for DSP. IEEE transactions on circuits and systems—II: Analog and digital signal processing, 47(9), 849–875.

Kienhuis, B., & Deprettere, E. F. (2003). Modeling stream-based applications using the SBF model of computation. Journal of Signal Processing Systems, 34(3), 291–300.

Wipliez, M., Roquier, G., Raulet, M., Nezan, J.-F., & Deforges, O. (2008). Code generation for the MPEG reconfigurable video coding framework: From CAL actions to C functions. In Proceedings of the IEEE international conference on multimedia and expo.

Wipliez, M., Roquier, G., & Nezan, J. (2009). Software code generation for the RVC-CAL language. Journal of Signal Processing Systems. doi:10.1007/s11265-009-0390-z.

Open RVC CAL compiler (2009). http://sourceforge.net/apps/trac/orcc/.

Gu, R., Janneck, J., Raulet, M., & Bhattacharyya, S. S. (2009). Exploiting statically schedulable regions in dataflow programs. In Proceedings of the international conference on acoustics, speech, and signal processing (pp. 565–568). Taipei, Taiwan.

Karp, R. M., & Miller, R. E. (1966). Properties of a model for parallel computations: Determinacy, termination, queuing. SIAM Journal of Applied Math, 14(6), 1390–1411.

Kahn, G. (1974). The semantics of a simple language for parallel programming. In Proceedings of the IFIP congress.

Dennis, J. B. (1975). First version of a data flow procedure language. Tech. Rep., Laboratory for Computer Science, Massachusetts Institute of Technology.

Lee, E. A., & Parks, T. M. (1995). Dataflow process networks. Proceedings of the IEEE, 83, 773–799.

Lublinerman, R., & Tripakis, S. (2008). Translating data flow to synchronous block diagrams. In Proceedings of the IEEE workshop on embedded systems for real-time multimedia.

Sriram, S., & Bhattacharyya, S. S. (2009). Embedded multiprocessors: Scheduling and synchronization (2nd ed.). Boca Raton: CRC.

Bilsen, G., Engels, M., Lauwereins, R., & Peperstraete, J. A. (1996). Cyclo-static dataflow. IEEE Transactions on Signal Processing, 44(2), 397–408.

Buck, J. T., & Lee, E. A. (1993). The token flow model. In L. Bic, G. Gao, & J. Gaudiot (Eds.), Advanced topics in dataflow computing and multithreading. Los Alamitos: IEEE Computer Society.

Plishker, W., Sane, N., Kiemb, M., Anand, K., & Bhattacharyya, S. S. (2008). Functional DIF for rapid prototyping. In Proceedings of the international symposium on rapid system prototyping (pp. 17–23). Monterey, California.

Hsu, C., & Bhattacharyya, S. S. (2005). Porting DSP applications across design tools using the dataflow interchange format. In Proceedings of the international workshop on rapid system prototyping (pp. 40–46). Montreal, Canada.

Gu, R., Janneck, J. W., Bhattacharyya, S. S., Raulet, M., Wipliez, M., & Plishker, W. (2009). Exploring the concurrency of an MPEG RVC decoder based on dataflow program analysis. IEEE Transactions on Circuits and Systems for Video Technology, 19, 1646–1657.

Haubelt, C., Falk, J., Keinert, J., Schlichter, T., Streub’́uhr, M., Deyhle, A., et al. (2007). A SystemC-based design methodology for digital signal processing systems. EURASIP Journal on Embedded Systems, 2007, Article ID 47580 (22 pp.).

Sung, W., Oh, M., Im, C., & Ha, S. (1997). Demonstration of hardware software codesign workflow in PeaCE. In Proceedings of the international conference on VLSI and CAD.

Bhattacharyya, S. S., Eker, J., Janneck, J. W., Lucarz, C., Mattavelli, M., & Raulet, M. (2009). Overview of the MPEG reconfigurable video coding framework. Journal of Signal Processing Systems. doi:10.1007/s11265-009-0399-3.

Lucarz, C., Mattavelli, M., Thomas-Kerr, J., & Janneck, J. (2007). Reconfigurable media coding: A new specification model for multimedia coders. In Proceedings of the IEEE workshop on signal processing systems.

Bhattacharyya, S. S., Brebner, G., Eker, J., Janneck, J. W., Mattavelli, M., von Platen, C., et al. (2008). OpenDF—a dataflow toolset for reconfigurable hardware and multicore systems. ACM SIGARCH Computer Architecture News, 36(5). http://hal.archives-ouvertes.fr/hal-00398827/en/.

Platen, C. V., & Eker, J. (2008). Efficient realization of a CAL video decoder on a mobile terminal. In Proceedings of the IEEE workshop on signal processing systems.

Boutellier, J., Sadhanala, V., Lucarz, C., Brisk, P., & Mattavelli, M. (2008). Scheduling of dataflow models within the reconfigurable video coding framework. In Proceedings of the IEEE workshop on signal processing systems.

Li, M., Wang, H., & Li, P. (2003). Tasks mapping in multi-core based system: Hybrid ACO&GA approach. In Proceedings of the international conference on ASIC.

Ennals, R., Sharp, R., & Mycroft, A. (2005). Task partitioning for multi-core network processors. In Proceedings of the international conference on compiler construction.

Cormen, T. H., Stein, C., Leiserson, C. E., & Rivest, R. L. (2001). Introduction to algorithms (2nd ed.). Cambridge: MIT.

Bhattacharyya, S. S., Murthy, P. K., & Lee, E. A. (1997). APGAN and RPMC: Complementary heuristics for translating DSP block diagrams into efficient software implementations. Journal of Design Automation for Embedded Systems, 2(1), 33–60.

Plishker, W., Sane, N., & Bhattacharyya, S. S. (2009). A generalized scheduling approach for dynamic dataflow applications. In Proceedings of the design, automation and test in Europe conference and exhibition (pp. 111–116). Nice, France.

Ko, M., Zissulescu, C., Puthenpurayil, S., Bhattacharyya, S. S., Kienhuis, B., & Deprettere, E. (2007). Parameterized looped schedules for compact representation of execution sequences in DSP hardware and software implementation. IEEE Transactions on Signal Processing, 55(6), 3126–3138.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gu, R., Janneck, J.W., Raulet, M. et al. Exploiting Statically Schedulable Regions in Dataflow Programs. J Sign Process Syst 63, 129–142 (2011). https://doi.org/10.1007/s11265-009-0445-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-009-0445-1