Abstract

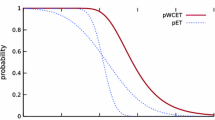

In this paper, we investigate static probabilistic timing analysis (SPTA) for single processor real-time systems that use a cache with an evict-on-miss random replacement policy. We show that previously published formulae for the probability of a cache hit can produce results that are optimistic and unsound when used to compute probabilistic worst-case execution time (pWCET) distributions. We investigate the correctness, optimality, and precision of different approaches to SPTA for random replacement caches. We prove that one of the previously published formulae for the probability of a cache hit is optimal with respect to the limited information (reuse distance and cache associativity) that it uses. We derive an alternative formulation that makes use of additional information in the form of the number of distinct memory blocks accessed (the stack distance). This provides a complementary lower bound that can be used together with previously published formula to obtain more accurate analysis. We improve upon this joint approach by using extra information about cache contention. To investigate the precision of various approaches to SPTA, we introduce a simple exhaustive method that computes a precise pWCET distribution, albeit at the cost of exponential complexity. We integrate this precise approach, applied to small numbers of frequently accessed memory blocks, with imprecise analysis of other memory blocks, to form a combined approach that improves precision, without significantly increasing complexity. The performance of the various approaches are compared on benchmark programs. We also make comparisons against deterministic analysis of the least recently used replacement policy.

Similar content being viewed by others

Notes

In a fully associative cache, any memory block may be placed in any cache line.

The term stack distance of an element \(e_l\) refers to the position of the element on a stack with least-recently used ordering.

Each memory access with a stack distance larger than or equal to the associativity results in a cache miss in the case of an LRU cache, while each memory access with a smaller stack distance results in a cache hit.

References

Abella J, Hardy D, Puaut I, Quinones E, Cazorla F (2014) On the comparison of deterministic and probabilistic WCET estimation techniques. In: Proceedings of the 2014 26th Euromicro conference on real-time systems, ECRTS ’14, pp 266–275

Altmeyer S, Davis RI (2014) On the correctness, optimality and precision of static probabilistic timing analysis. In: Proceedings of the conference on design, automation & test in Europe, DATE ’14, pp 26:1–26:6

Bernat G, Colin A, Petter S (2002) WCET analysis of probabilistic hard real-time systems. In: Proceedings of the 23rd IEEE real-time systems symposium, RTSS ’02, pp 279–288

Bernat G, Colin A, Petters S (2003) pWECT: a tool for probabilistic worst-case execution time analysis of real-time systems. Tech. Rep. YCS-353-2003, Department of Computer Science, The University of York

Bernat G, Burns A, Newby M (2005) Probabilistic timing analysis: an approach using copulas. J Embed Comput 1(2):179–194

Binkert N, Beckmann B, Black G, Reinhardt SK, Saidi A, Basu A, Hestness J, Hower DR, Krishna T, Sardashti S, Sen R, Sewell K, Shoaib M, Vaish N, Hill MD, Wood DA (2011) The gem5 simulator. SIGARCH Comput Archit News 39(2):1–7

Burns A, Edgar S (2000) Predicting computation time for advanced processor architectures. In: Proceedings of the 12th Euromicro conference on real-time systems, Euromicro-RTS’00, pp 89–96

Cazorla FJ, Quiñones E, Vardanega T, Cucu L, Triquet B, Bernat G, Berger ED, Abella J, Wartel F, Houston M, Santinelli L, Kosmidis L, Lo C, Maxim D (2013) Proartis: probabilistically analyzable real-time systems. ACM Trans Embed Comput Syst 12(2s):94

Cucu-Grosjean L (2013) Independence—a misunderstood property of and for probabilistic real-time systems. In: Audsley N, Baruah S (eds) In real-time systems: the past, the present and the future, pp 29–37

Cucu-Grosjean L, Santinelli L, Houston M, Lo C, Vardanega T, Kosmidis L, Abella J, Mezzetti E, Quiones E, Cazorla FJ (2012) Measurement-based probabilistic timing analysis for multi-path programs. In: Proceedings of the 2012 24th Euromicro conference on real-time systems, ECRTS ’12, pp 91–101

Davis R (2013) Improvements to static probabilistic timing analysis for systems with random cache replacement policies. In: Real-time scheduling open problems seminar (RTSOPS), pp 22–24

Davis R, Santinelli L, Altmeyer S, Maiza C, Cucu-Grosjean L (2013) Analysis of probabilistic cache related pre-emption delays. In: Proceedings of the 2013 25th Euromicro conference on real-time systems, ECRTS ’13, pp 168–179

Edgar S, Burns A (2001) Statistical analysis of WCET for scheduling. In: Proceedings of the 22nd IEEE real-time systems symposium, RTSS ’01, pp 215–225

Ferdinand C, Martin F, Wilhelm R, Alt M (1999) Cache behavior prediction by abstract interpretation. Sci Comput Program 35(2–3):163–189

Griffin D, Burns A (2010) Realism in statistical analysis of worst case execution times. In: 10th international workshop on worst-case execution time analysis (WCET’10), pp 49–57

Grund D, Reineke J (2010a) Precise and efficient FIFO-replacement analysis based on static phase detection. In: Proceedings of the 22nd Euromicro conference on real-time systems, ECRTS ’10, pp 155–164

Grund D, Reineke J (2010b) Toward precise PLRU cache analysis. In: 10th international workshop on worst-case execution time analysis (WCET’10), pp 28–39

Gustafsson J, Betts A, Ermedahl A, Lisper B (2010) The Mälardalen WCET benchmarks—past, present and future. In: 10th international workshop on worst-case execution time analysis (WCET’10), pp 136–146

Hansen J, Hissam S, Moreno GA (2009) Statistical-based wcet estimation and validation. In: 9th international workshop on worst-case execution time analysis (WCET’09), pp 1–11

Hardy D, Puaut I (2013) Static probabilistic worst case execution time estimation for architectures with faulty instruction caches. In: Proceedings of the 21st international conference on real-time networks and systems, RTNS ’13, pp 35–44

Kosmidis L, Abella J, Quiñones E, Cazorla FJ (2013) A cache design for probabilistically analysable real-time systems. In: Proceedings of the conference on design, automation and test in Europe, DATE ’13, pp 513–518

Li YT, Malik S (2006) Performance analysis of embedded software using implicit path enumeration. Trans Comp-Aided Des Integ Circ Syst 16(12):1477–1487

Maxim D, Houston M, Santinelli L, Bernat G, Davis RI, Cucu-Grosjean L (2012) Re-sampling for statistical timing analysis of real-time systems. In: Proceedings of the 20th international conference on real-time and network systems, RTNS ’12, pp 111–120

Quiñones E, Berger ED, Bernat G, Cazorla FJ (2009) Using randomized caches in probabilistic real-time systems. In: Proceedings of the 2009 21st Euromicro conference on real-time systems, ECRTS ’09, pp 129–138

Refaat K, Hladik PE (2010) Efficient stochastic analysis of real-time systems via random sampling. In: Proceedings of the 22nd Euromicro conference on real-time systems, ECRTS ’10, pp 175–183

Reineke J (2014) Randomized caches considered harmful in hard real-time systems. LITES 1(1):03:1–03:13

Theiling H, Ferdinand C, Wilhelm R (2000) Fast and precise wcet prediction by separated cache and path analyses. Real-Time Syst 18(2/3):157–179

Wilhelm R, Engblom J, Ermedahl A, Holsti N, Thesing S, Whalley D, Bernat G, Ferdinand C, Heckmann R, Mitra T, Mueller F, Puaut I, Puschner P, Staschulat G, Stenströem P (2008) The worst-case execution time problem: overview of methods and survey of tools. Trans Embed Comput Syst 7(3):36:1–36:53

Yue L, Bate I, Nolte T, Cucu-Grosjean L (2011) A new way about using statistical analysis of worst-case execution times. ACM SIGBED Rev 8(3):11–14

Zhou S (2010) An efficient simulation algorithm for cache of random replacement policy. In: The 7th IFIP international conference on network and parallel computing (NPC2010), pp 144–154

Acknowledgments

This work was partially funded by COST Action IC1202: Timing Analysis On Code-Level (TACLe), the UK EPSRC Project MCC (EP/K011626/1), and the EU FP7 Integrated Project PROXIMA (611085).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Altmeyer, S., Cucu-Grosjean, L. & Davis, R.I. Static probabilistic timing analysis for real-time systems using random replacement caches. Real-Time Syst 51, 77–123 (2015). https://doi.org/10.1007/s11241-014-9218-4

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11241-014-9218-4