Abstract

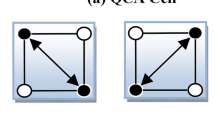

Increasing device density and reducing energy consumption are challenging issues in integrated nanoscale circuits. Reversible logic in quantum-dot cellular automata (QCA) nanotechnology is emerging as a promising candidate to overcome these issues and to introduce new computation paradigms with unique features like nanoscale feature size and ultra-low power dissipation. For the first time, QCA cell-based designs of reversible Feynman, Toffoli, Fredkin, and Peres gates are presented in this paper. These elementary gates are usually used in the synthesis of reversible circuits. The proposed layouts utilize electrostatic interactions between cells within QCA configurations to perform desired functions. All the robust designs are evaluated in terms of hardware complexity and power dissipation using QCADesigner and QCAPro simulation tools. The efficient QCA layouts of proposed gates have notable improvements as compared to the existing ones in terms of gate delay, cell count, area occupation, quantum cost, leakage energy, and switching energy. As a result, the proposed elementary gates via QCA cell level-based design are good candidates for building and developing high-level nanoelectronic reversible circuits.

Similar content being viewed by others

References

Sen B, Goswami M, Mazumdar S, Sikdar BK (2015) Towards modular design of reliable quantum-dot cellular automata logic circuit using multiplexers. Comput Electr Eng 45:42–54

Roohi A, Demara R, Khoshavi N (2015) Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron J 46:531–542

Sen B, Dutta M, Mukherjee R, Nath R, Sinha A, Sikdar B (2016) Towards the design of hybrid QCA tiles targeting high fault tolerance. J Comput Electron 15:429–445

Seminario J, Derosa P, Cordova L, Bozard B (2004) A molecular device operating at terahertz frequencies: theoretical simulations. IEEE Trans Nanotechnol 3:215–218

Cowburnand R, Welland M (2000) Room temperature magnetic quantum cellular automata. Science 287:1466–1468

Lent C, Tougaw P, Porod W, Bernstein G (1993) Quantum cellular automata. Nanotechnology 4:49–57

Rashidi H, Rezai A, Soltany S (2016) High-performance multiplexer architecture for quantum-dot cellular automata. J Comput Electron 15:968–981

Abutaleb MM (2017) A novel power-efficient high-speed clock management unit using quantum-dot cellular automata. J Nanoparticle Res 19:128

Sen B, Chowdhury MR, Mukherjee R, Goswami M, Sikdar BK (2017) Reliability-aware design for programmable QCA logic with scalable clocking circuit. J Comput Electron 16:473–485

Abutaleb MM (2018) QCAPUF: QCA-based physically unclonable function as a hardware security primitive. Semicond Sci Technol 33:045011

Abutaleb MM (2018) A novel configurable flip flop design using inherent capabilities of quantum-dot cellular automata. Microprocess Microsyst 56:101–112

Desoete B, Vos AD (2002) A reversible carry-look-ahead adder using control gates. Integr VLSI J 33:89–104

Al-Rabadi AN (2004) Reversible logic synthesis: from fundamentals to quantum computing. Springer, Berlin

Wille R, Soeken M, Miller DM, Drechsler R (2014) Trading off circuit lines and gate costs in the synthesis of reversible logic. Integr VLSI J 47:284–294

Wille R, Grobe D, Frehse S, Dueck GW, Drechsler R (2011) Debugging reversible circuits. Integr VLSI J 44:51–61

Landauer R (1961) Irreversibility and heat generation in the computing process. IBM J Res Dev 5:183–191

Miller DM, Wille R, Drechsler R (2010) Reducing reversible circuit cost by adding lines. In: 40th IEEE International Symposium on Multiple-Valued Logic, pp 217–222

Rice JE, Nayeem N (2011) Ordering techniques for ESOP-based Toffoli cascade generation. In: IEEE Pacific Rim Conference on Communications, Computers and Signal Processing, pp 274–279

Rauchenecker A, Ostermann T, Wille R (2017) Exploiting reversible logic design for implementing adiabatic circuits. In: 24th Int. Conf. Mixed Design of Integrated Circuits and Systems, pp 264–270

Rahmati M, Houshmand M, Kaffashian MH (2017) Novel designs of a carry/borrow look-ahead adder/subtractor using reversible gates. J Comput Electron 16:856–866

Tougaw PD, Lent CS (1994) Logical devices implemented using quantum cellular automata. Appl Phys 75:1818–1824

Lent CS, Tougaw PD (1997) A device architecture for computing with quantum dots. Proc IEEE 85:541–557

Toth G, Lent C (1999) Quasi-adiabatic switching for metal-island quantum-dot cellular automata. J Appl Phys 85:2977–2984

Bernstein GH, Imre A, Metlushko V et al (2005) Magnetic QCA systems. Microelectron J 36:619–624

Snider GL, Orlov AO, Amlani I et al (1998) Experimental demonstration of quantum-dot cellular automata. Semicond Sci Technol 13:A130–A134

Bagherian Khosroshahy M, Sam Daliri M, Abdoli A, Navi K, Bagherzadeh N (2016) A 3D universal structure based on molecular-QCA and CNT technologies. J Mol Struct 1119:86–95

Liu W, Swartzlander E Jr, O’Neill M (2013) Design of semiconductor QCA systems. Artech House, Norwood

Taherkhani E, Moaiyeri M, Angizi S (2017) Design of an ultra-efficient reversible full adder-subtractor in quantum-dot cellular automata. Optik 142:557–563

Smith C, Gardelis S, Rushforth A et al (2003) Realization of quantum-dot cellular automata using semiconductor quantum dots. Superlattices Microstruct 34:195–203

Wang Z, Liu F (2011) Nanopatterned graphene quantum dots as building blocks for quantum cellular automata. Nanoscale 3:4201–4205

DiLabio GA, Wolkow RA, Pitters JL, Piva PG (2014) Atomistic quantum dots, US Patent 14/448, p 899

Cho H, Swartzlander E Jr (2009) Adder and multiplier design in quantum-dot cellular automata. IEEE Trans Comput 58:721–727

Niemier MT (2004) Designing digital systems in quantum cellular automata. Master’s Thesis, University of Notre Dame, Notre Dame, Indiana, USA

Schulhof G, Walus K, Jullien G (2007) Simulation of random cell displacements in qca. ACM J Emerg Technol Comput Syst 3:2

Shin SH, Jeon JC, Yoo KY (2013) Wire-crossing technique on quantum-dot cellular automata, Next Gener. In: Compu. Inf. Technol. Int. Conf., pp. 52–57

Walus K, Dysart T, Jullien G, Budiman R (2004) QCADesigner: a rapid design and simulation tool for quantum-dot cellular automata. IEEE Trans Nanotechnol 3:26–31

Timler J, Lent CS (2002) Power gain and dissipation in quantum dot cellular automata. J Appl Phys 91:823–830

Timler J, Lent C (2003) Maxwell’s demon and quantum-dot cellular automata. J Appl Phys 94:1050–1060

Toth G, Lent C, Tougaw P (1996) Quantum cellular neural networks. Superlattices Microstruct 20:473–478

Das JC, De D (2016) Quantum-dot cellular automata based reversible low power parity generator and parity checker design for nanocommunication. Front Inf Technol Electron Eng 17:224–236

Debnath B, Das JC, De D (2017) Reversible logic-based image steganography using quantum dot cellular automata for secure nanocommunication. IET Circ Dev Syst 11:58–67

Singh G, Sarin RK, Raj B (2017) Design and analysis of area efficient QCA based reversible logic gates. Microprocess Microsyst 52:59–68

Mohammadi Z, Mohammadi M (2014) Implementing a one-bit reversible full adder using quantum-dot cellular automata. Quantum Inf Process 13:2127–2147

Garg U, Jain R (2016) Design and performance analysis of reversible RSG gate using QCA. Int J Comput Appl 139:37–41

Thapliyal H, Ranganathan N, Kotiyal S (2013) Design of testable reversible sequential circuits. IEEE Trans Very Large Scale Integr Syst 21:1201–1209

Das JC, De D (2017) Nanocommunication network design using QCA reversible crossbar switch. Nano Commun Netw 13:20–33

Sarker A, Bahar AN, Biswas PK, Morshed M (2014) A novel presentation of Peres gate (PG) in quantum-dot cellular automata (QCA). Eur Sci J 10:101–106

Kumawat R, Sasamal TN (2016) Design of 1-bit and 4-bit adder using reversible logic in quantum-dot cellular automata. In: 2016 IEEE International Conference on Recent Trends in Electronics, Information & Communication Technology, pp 593–597

Das JC, De D (2016) Novel low power reversible binary incrementer design using quantum-dot cellular automata. Microprocess Microsyst 42:10–23

Srivastava S, Sarkar S, Bhanja S (2009) Estimation of upper bound of power dissipation in QCA circuits. IEEE Trans Nanotechnol 8:116–127

Srivastava S, Asthana A, Bhanja S, Sarkar S, QCAPro-an error power estimation tool for QCA circuit design. In: Proc. IEEE Int. Symp. Circuits Syst, pp 2377–2380

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Abutaleb, M.M. Robust and efficient QCA cell-based nanostructures of elementary reversible logic gates. J Supercomput 74, 6258–6274 (2018). https://doi.org/10.1007/s11227-018-2550-z

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-018-2550-z