Abstract

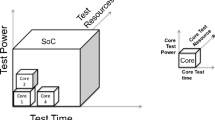

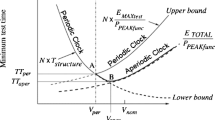

As a consequence of technology scaling and increasing power consumption of modern high performance designs, various techniques, such as clock gating and Dynamic Voltage and Frequency Scaling (DVFS), have been adapted to address power issues. These techniques are important and desirable to address reliability needs as well as economic issues. From a testing point of view, the introduction of power constraints during testing is needed to achieve the desired product quality and to avoid yield loss. Unlike designers who have benefited from the Design-for-Test hardware introduced for testing, test engineers have rarely taken advantage of the extra hardware introduced to meet design needs. In this paper, we make use of the DVFS technology and its associated hardware to improve test economics. We formulate the power constrained testing problem as an optimization problem that makes use of DVFS technology. We show that superior test schedules can be obtained for both session-based and sessionless testing methods relative to existing and traditional methods of obtaining test schedules.

Similar content being viewed by others

References

Bild DR, Misra S, Chantemy T, Kumar P, Dick RP, Huy XS, Choudhary A (2008) Temperature-aware test scheduling for multiprocessor systems-on-chip. In: IEEE/ACM international conference on computer-aided design (ICCAD), pp 59– 66

Chakrabarty K (2000) Test scheduling for core-based systems using mixed-integer linear programming. IEEE Trans Computer-Aided Des of Integr Circ and Syst 19(10):1163–1174

Cheng WH, Baas BM (2008) Dynamic voltage and frequency scaling circuits with two supply voltages. In: IEEE international symposium on circuits and systems (ISCAS), pp 1236–1239.

Choi K, Soma R, Pedram M (2004) Fine-grained dynamic voltage and frequency scaling for precise energy and performance trade-off based on the ratio of off-chip access to on-chip computation times. In: Proceedings of the conference on design, automation and test in Europe (DATE), p 10004

Chou RM, Saluja KK, Agrawal VD (1997) Scheduling tests for VLSI systems under power constraints. IEEE Trans Very Large Scale Integr (VLSI) Syst 5:175–185

Craig GL, Kime CR, Saluja KK (1988) Test scheduling and control for VLSI built-in self-test. IEEE Trans Comput 37(9):1099–1109

Davidson S (1999) ITC’99 Benchmark Circuits - Preliminary Results. In: Proceedings of the international testing conference, pp 1125–1125

Girard P, Nicolici N, Wen X (2010) Power-aware testing and test strategies for low power devies. Springer, New York

He Z, Peng Z, Eles P (2006) Power constrained and defect-probability driven soc test scheduling with test set partitioning. In: Proceedings of design, automation & test in Europe (DATE), pp 1–6

Iyengar V, Chakrabarty K, Marinissen EJ (2003) Test access mechanism optimization, test scheduling, and tester data volume reduction for system-on-chip. IEEE Trans Comput 52:1619– 1631

Kavousianos X, Chakrabarty K, Jain A, Parekhji R (November 2011) Test scheduling for multicore SoCs with dynamic voltage scaling and multiple voltage islands. In: 20th asian test symposium, pp 33–39

Kavousianos X, Chakrabarty K, Jain A, Parekhji R (2012) Test schedule optimization for multicore SoCs: handling dynamic voltage scaling and multiple voltage islands. IEEE Trans Computer-Aided Des Integr Circ and Syst 31:1754–1766

Kime CR, Saluja KK (1982) Test schduling in testable VLSI Circuits. In: Twenty-fifth international symposium on fault-tolerant computing, Santa Monica, pp 406–412

Marinissen EJ, Iyengar V, Chakrabarty K (2002) A set of benchmarks for modular testing of SOCs. In: Proceedings of the international test conference, Baltimore, pp 519–528.

Millican SK, Saluja KK (2012) Linear programming formulations for thermal-aware test scheduling of 3D-stacked integrated circuits. In: IEEE 21st asian test symposium, Niigata, pp 37–42

Millican SK, Saluja KK (2013) Formulating optimal test scheduling problem with dynamic voltage and frequency scaling. In: 22nd Asiantest symposium (ATS), pp 165–170

Moore GE (1965) Cramming more components onto integrated circuits. Electronics 38(8)

Nose K, Sakurai T (2000) Optimization of VDD and VTH for low-power and high-speed applications. In: Proceedings of the asia and south pacific design automation conference (ASP-DAC), pp 469–474

Nourani M, Chin J (2003) Power-time tradeoff in test scheduling for SoCs. In: Proceedings of the 21st international conference on computer design, pp 548–553. IEEE Computer Society

Park J, Shin D, Chang N, Pedram M (2010) Accurate modeling and calculation of delay and energy overheads of dynamic voltage scaling in modern high-performance microprocessors. In: ACM/IEEE international symposium on low-power electronics and design (ISLPED), Austin, pp 419 –424

Sakurai T, Newton AR (1990) Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas. IEEE J Solid-State Circ 25:584–594

Salamy H, Harmanani HM (2011) An optimal formulation for test scheduling network-on-chip using multiple clock rates. In: 24th Canadian conference on electrical and computer engineering (CCECE), pp 215–218

Samii S, Selkala M, Larsson E, Chakrabarty K, Peng Z (2008) Cycle-accurate test power modeling and its application to SoC test architecture design and scheduling. IEEE Trans Computer-Aided Des Integr Circ Syst 27:973–977

Sheshadri V, Agrawal VD, Agrawal P (2012) Optimal power-constrained SoC test schedules with customizable clock rates. In: IEEE international SOC conference (SOCC), Niagara Falls, NY, pp 271–276

Sheshadri V, Agrawal VD, Agrawal P (2013) Optimum test schedule for SoC with specified clock frequencies and supply voltages. In: 26th international conference on VLSI design and international conference on embedded systems, Pune, pp 267–272

Yao C, Saluja KK, Ramanathan P (2011) Power and thermal constrained test scheduling under deep submicron technologies. IEEE Trans Computer-Aided Des Integr Circ and Syst 30:317–322

Zhao D, Upadhyaya S (2005) Dynamically partitioned test scheduling with adaptive TAM configuration for power-constrained SoC testing. IEEE Trans Computer-Aided Des Integr Circ and Syst 24:956–965

Zorian Y (1993) A distributed BIST control scheme for complex VLSI devices. In: 11th annual IEEE VLSI test symposium. Atlantic City, pp 4–9

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: J.-L. Huang

A version of this paper appeared in IEEE Asian Test Symposium 2013 (ATS13) [16]

Rights and permissions

About this article

Cite this article

Millican, S.K., Saluja, K.K. Optimal Test Scheduling Formulation under Power Constraints with Dynamic Voltage and Frequency Scaling. J Electron Test 30, 569–580 (2014). https://doi.org/10.1007/s10836-014-5473-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-014-5473-5