Abstract

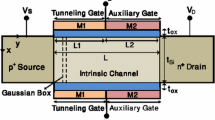

A two dimensional (2D) analytical drain current model has been developed for a delta-doped tunnel field-effect transistor (D-TFET) that can address the ON-current issues of the conventional TFET. Insertion of a highly doped delta layer in the source region paves the way for improved tunneling volume and thus provides high drain current as compared with TFETs. The present model takes into account the effects of the distance between the delta-doping region and the source–channel interface on the subthreshold swing (SS), current ratio, and ON-current performance. The D-TFET is predicted to have a higher current ratio \(\left( {\frac{I_\mathrm{ON} }{I_\mathrm{OFF} }\cong 10^{11}} \right) \) compared with TFETs \(\left( {\frac{I_\mathrm{ON} }{I_\mathrm{OFF} }\cong 10^{10}} \right) \) with a reasonable SS \(\left( {{\sim }52\,\mathrm{mV/dec}} \right) \) and \(V_\mathrm{th}\) performance at an optimal position of 2 nm from the channel. The surface potential, electric field, and minimum tunneling distance have been derived using the solution of the 2D Poisson equation. The accuracy of the D-TFET model is validated using the technology computer aided design (TCAD) device simulator from Synopsys.

Similar content being viewed by others

References

Reddick, W.M., Amaratunga, G.A.J.: Silicon Surface Tunnel Transistor. Applied Physics Letters 67, 494–496 (1995)

Datta, S., Liu, H., Narayanan, V.: Tunnel FET Technology: A reliability perspective. Solid State Electronics 54, 861–874 (2014)

Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.J.K.: Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Letters 28, 743–745 (2007)

Zhang, Q., Zhao, W., Seabaugh, A.: Low subthreshold-swing tunnel transistors. IEEE Electron Device Letters 27, 297–300 (2006)

Samuel, T.S.A., Balamurugan, N.B., Bhuvaneswari, S., Sharmila, D., Padmapriya, K.: Analytical modelling and simulation of single-gate SOI TFET for low-power applications. International Journal of Electronics 101, 779–788 (2014)

Kanungo, S., Rahaman, H., Dasgupta, P.S.: A Simple Analytical Model of Silicon On Insulator Tunnel FET, Proceedings of IEEE International Conference on Computers and Devices for Communication, pp. 1-4 (2012)

Vandenberghe, W.G., Verhulst, A.S., Groeseneken, G., Soree, B., Magnus, W.: Analytical Model for a Tunnel Field-Effect Transistor, Proceedings of IEEE Mediterranean Conference on Electro-technical Conference, pp. 923-928 (2008)

Lee, M.J., Choi, W.Y.: Analytical model of single-gate silicon-on- insulator (SOI) Tunneling Field-Effect Transistors (TFETs). Solid-State Electronics 63, 110–114 (2011)

Zhang, L., Lin, X., He, J., Chan, M.: An Analytical Charge Model for Double-Gate Tunnel FETs. IEEE Transaction on Electron Devices 59, 3217–3223 (2012)

Wu, C., Huang, R., Huang, Q., Wang, C., Wang, J., Wang, Y.: An Analytical Surface Potential Model Accounting for the Dual-Modulation Effects in Tunnel FETs. IEEE Transaction on Electron Devices 61, 2690–2696 (2014)

Dash, S., Mishra, G.P.: A 2D analytical cylindrical gate tunnel FET (CG-TFET) model: impact of shortest tunneling distance. Advances in Natural Sciences: Nanoscience and Nanotechnology 6, 035005–035014 (2015)

Dash, S., Mishra, G.P.: A new analytical threshold voltage model of cylindrical gate tunnel FET (CG-TFET). Superlattices and Microstructures 86, 211–220 (2015)

Vishnoi, R., Kumar, M.J.: An Accurate Compact Analytical Model for the Drain Current of a TFET from Subthreshold to Strong Inversion. IEEE Transaction on Electron Devices 62, 478–484 (2015)

Born, M., Bhuwalka, K.K., Schindler, M., Abelein, U., Schmidt, M., Sulima, T., Eisele, I.: Tunnel FET: A CMOS device for high temperature applications, Proceedings of IEEE International Conference on Microelectronics, pp. 124-127 (2006)

Narang, R., Saxena, M., Gupta, R.S., Gupta, M.: Impact of temperature variations on the device and circuit performance of Tunnel FET: A Simulation Study. IEEE Transactions on Nanotechnology 12, 951–957 (2013)

Kim, S. H., Agarwal, S., Jacobson, Z.A., Matheu, P., Chenming, H., Liu, T-J.K.: Tunnel Field Effect Transistors with raised Germanium Source, IEEE Electron Devices Letters 31, pp. 1107-1109 (2010)

Virani, H.G., Kottantharayil, A.: Optimization of Heterojunction n-channel Tunnel FET with high-k spacers, Proceedings of IEEE International workshop on Electron Devices and semiconductor technology, pp. 1-6 (2009)

Bagga, N., Sarkar, S.K.: An Analytical Model for Tunnel Barrier Modulation in Triple Metal Double Gate TFET. IEEE Transactions on Electron Devices 62, 2136–2142 (2015)

Boucart, K., Ionescu, A.M.: Double gate Tunnel FET with high-k gate dielectric. IEEE Transactions on Electron Devices 54, 1725–1733 (2007)

Choi, W.Y., Lee, W.: Hetero-Gate-Dielectric Tunneling Field Effect Transistors. IEEE Transactions on Electron Devices 57, 2317–2319 (2010)

Sentaurus Device User Guide, Synopsys, Inc., Mountain View (2010)

Bhuwalka, K.K., Schulze, J., Eisele, I.: Scaling the vertical tunnel FET with tunnel bandgap modulation and gate work function engineering. IEEE Transaction on Electron Devices 52, 909–917 (2005)

Samuel, T.S.A., Balamurugan, N.B.: Analytical modeling and simulation of germanium single gate silicon on insulator TFET. Journal of Semiconductor 35, 034002–034005 (2014)

Gholizadeh, M., Hosseini, S.E.: A 2-D Analytical Model for Double-Gate Tunnel FETs. IEEE Transaction on Electron Devices 61, 1494–1500 (2014)

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflicts of interest

We have no conflict of interest to declare.

Rights and permissions

About this article

Cite this article

Panda, S., Dash, S., Behera, S.K. et al. Delta-doped tunnel FET (D-TFET) to improve current ratio (\(I_\mathrm{ON}/I_\mathrm{OFF}\)) and ON-current performance. J Comput Electron 15, 857–864 (2016). https://doi.org/10.1007/s10825-016-0860-z

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-016-0860-z