Abstract

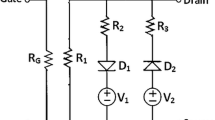

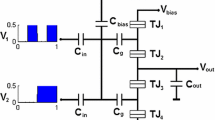

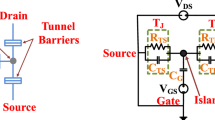

A new macro model of single electron transistor (SET) for SPICE based simulation of SET circuits is proposed. Two voltage controlled current sources and some scaling factors are incorporated in the existing model to derive our model. The V–I characteristics of the proposed SET is promising enough to be used as the basic element for designing circuits based on SETs. A comparison with the previous models establishes the fact that our model efficiently removes the drawbacks of the existing models. Our model also agrees well with the results obtained from popular SIMON simulator. To verify the accuracy, we have designed a SET inverter cell and investigated its characteristics. The work includes the effect of the parameters on the noise margin and voltage transfer characteristics of the inverter circuit. Further, to verify the applicability, a multi peak negative differential resistance circuit based on the proposed model is designed and simulated.

Similar content being viewed by others

References

Grabert, H., Devoret, M.H. (eds.): Single Charge Tunneling Coulomb Blockade Phenomena in Nanostructures. Plenum press, New York and London (1992)

Gordon, D.G., Montemerlo, M.S., Love, J.C., Opiteck, G.J., Ellenborgen, J.C.: Overview of nanoelectronic devices. Proc. IEEE 85, 521 (1997)

Ionescu, A.M., Declercq, M.J., Mahapatra, S., Banerjee, K., Gautier, J.: Few Electron devices: towards hybrid CMOS-SET integrated circuits. In: Proceedings \(39^{{\rm th}}\)Design Automation Conference. New Orleans (2002)

Jain, A., Singh, N.B., Sarkar, S.K.: A new compact analytical model of single electron transistor for hybrid SET-MOS circuits. Solid State Electron. 104, 90 (2015)

Jana, B., Jana, A., Sing, J.K., Sarkar, S.K.: Performance of multigate single electron transistor in wide temperature range and 22 nm hybrid technology. J. Nanoelectron. Optoelectron. 9, 357 (2014)

Chen, R.H., Korotkov, A.N., Likharev, K.K.: Single-electron transistor logic. Appl. Phys. Lett. 68, 1954 (1996)

Boubaker, A., Sghaier, Na, Trodi, M., Kalbossi, A., Boboux, N., Souifi, A.: A new SIMPLORER model for single-electron transistors. Microelectron. J. 38, 894 (2007)

Mahapatra, S., Banerjee, K., Pegeon, F., Ionescu, A.M.: A CAD framework for co-design and analysis of CMOS-SET hybrid integrated circuits. In: Proceedings of ICCAD. SanJose (2003)

Mahapatra, S., Vaish, V., Wasshuber, C., Banerjee, K., Ionescu, A.M.: Analytical modeling of single electron transistor for hybrid CMOS-SET analog IC design. IEEE Trans. Electron. Devices 51, 1772 (2004)

Durrani, Z.A.K.: Single Electron Devices and Circuits in Silicon. Imperial College Press, London (2010)

Wasshuber, C.: Computational Single-Electronics. Springer, New York (2001)

Chaohong, H., Cotofana, S.D., Jianfei, J., Qiyu, C.: Analog-to-digital converter based on single-electron tunneling transistors. IEEE Trans. VLSI Syst. 12, 1209 (2004)

Gerousis, C., Grepiotis, A.: Reconfigurable gate array architecture for logic functions in tunneling transistor technology. Microelectron. J. 44, 706 (2011)

Chen, Y.C., Wang, C.Y., Huang, C.Y.: Verification of reconfigurable binary decision diagram-based single-electron transistor arrays. IEEE Trans. Comput. Aided Des. Integr. Circuit. Syst. 32, 1473 (2013)

Sahafi, A., Moaiyeri, M.H., Navi, K., Hashemipour, O.: Efficient single-electron transistor inverter-based logic circuits and memory elements. J. Comput. Theor. Nanosci. 10, 1171 (2013)

agarwal, P.B., Kumar, A.: Design and simulation of octal-to-bi nary encoder using capacitive single-electron transistors (C-SETs). Microelectron. J. 42, 96 (2011)

Wasshuber, C.: Single-electronics-how it works: how it’s used—how it’s simulated. In: Proceedings of the International Symposium on Quality Electronic Design. San Jose (2002)

Samanta, D., Ghosh, A., Sarkar, S., Sarkar, S.K.: Design and simulation of a sequence generator using single electron devices and hybrid architecture. J. Nanoelectron. Optoelectron. 5, 1 (2010)

Abutaleb, M.M.: A new static differential design style for hybrid SET-CMOS logic circuits. J. Comput. Electron. 14, 329 (2015)

Jana, A., Basanta Singh, N., Sing, J.K., Sarkar, S.K.: Design and simulation of hybrid CMOS-SET circuits. Microelectron. Reliab. 53, 592 (2012)

Sui, B., Fang, L., Chi, Y., Zhang, C.: Nano-reconfigurable cells with hybrid circuits of single-electron transistors and MOSFETs. IEEE Trans. Electron. Devices 57, 2251 (2010)

Koppimen, P.J., Stewart, M.D., Zimmerman, M.J.: Fabrication and electrical characterization of fully CMOS-compatible Si single-electron devices. IEEE Trans. Electron. Device. 60, 78 (2013)

Jain, A., Singh, N.B., Ghosh, A., Sarkar, S.K.: Stability and reliability analysis of hybrid CMOS-SET circuits: a new approach. J. Comput. Theor. Nanosci. 11, 2519 (2014)

Wei, W., Han, J., Lombardi, F.: Design and evaluation of a hybrid memory cell by single-electron transfer. IEEE Trans. Nanotechnol. 12, 57 (2013)

Yu, Y.S., Hwang, S.W., Ahn, D.: Transient modelling of single-electron transistors for efficient circuit simulation by SPICE. IEE Proc. Circuit Device. Syst. 152, 691 (2005)

Boubaker, A., Troudib, M., Sghaierb, N., Souifia, A., Babouxa, N., Kalboussib, A.: A spice model for single electron transistor applications at low temperatures: inverter and ring oscillator. Proceedings of International Conference on Design & Technology of Integrated Systems in Nanoscale Era. Tozeur (2008)

Wei, W., Han, J., Lombardi, F.: Robust HSPICE modeling of a single electron turnstile. Microelectron. J. 45, 394 (2014)

Yu, Y.S., Hwang, S.W., Ahn, D.: Macromodeling of single-electron transistors for efficient circuit simulation. IEEE Trans. Electron. Device. 46, 1667 (1999)

Wu, Y.L., Lin, S.T.: An improved single electron transistor model for SPICE application. Nanotechnology 3, 321 (2003)

Karimian, M.R., Dousti, M.: A new SPICE macro-model for the simulation of single electron circuits. J. Korean Phys. Soc. 56, 1202 (2001)

Jain, A., Ghosh, A., Singh, N.B., Sarkar, S.K.: A new SPICE macro model of single electron transistor for efficient simulation of single-electronics circuits. Analog Integr. Circuit Signal Process. 82, 653 (2015)

Rabey, J., Chandrakasan, A., Nikolic, B.: Digital Integrated Circuits a Design Perspective. Prentice Hall, Englewood Cliffs (2003)

Gan, K.J.: Novel four-peak or five-peak current-voltage characteristics for three negative differential resistance devices in series. Solid-State Electron. 44(9), 1597–1602 (2000)

Gan, K.J.: The low-high-low I V characteristics of five to seven peaks based on four NDR devices. IEEE Trans. Electron. Device. 48(8), 1683–1687 (2001)

Shin, S., Kim, K.R.: Novel design of multiple negative-differential resistance (NDR) device in a 32 nm CMOS technology using TCAD. Proceeding of International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), pp. 316–319 (2013)

Acknowledgments

Subir Kumar Sarkar thankfully acknowledges the financial support obtained from UGC UPE-Phase II project, Jadavpur University.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ghosh, A., Jain, A., Singh, N.B. et al. A modified macro model approach for SPICE based simulation of single electron transistor. J Comput Electron 15, 400–406 (2016). https://doi.org/10.1007/s10825-015-0790-1

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-015-0790-1