Abstract

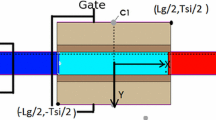

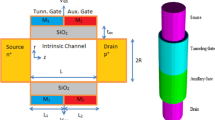

In this paper, we propose analytical modeling of double gate (DG) tunnel field effect transistor (TFET) which is derived by using Evanescent-mode analysis approach. This approach considers the channel potential as the sum of a long channel potential and a short channel perturbation along with the whole structure rather than just the \(\hbox {Si}/\hbox {SiO}_{2}\) interface or the channel centre. Due to this, the characteristic length lambda \((\lambda )\) does not depend on the transverse position within the channel. Analytical potential modeling of DG-TFET along with evaluation of electric field and drain current has been carried out. It has also been shown in the results that the proposed model has better channel potential and tunnel current than single-gate SOI TFET.

Similar content being viewed by others

References

Frank, D., Dennard, R.H., Nowak, E., Solomon, P.M., Taur, Y., Wong, H.-S.P.: Device scaling limits of Si MOSFETs and their application dependence. Proc. IEEE 89(3), 259–288 (2001)

Roy, K., Mukhopadhyay, S., Mahmoodi-Meimand, H.: Leakage current mechanisms and leakage reduction techniques in deep-submicrometer CMOS circuits. Proc. IEEE 91(2), 305–327 (2003)

Ionescu, A.M., Boucart, K., Moselund, K.E., Pott, V., Tsamados, D.: Small slope micro/nano-electronic switches. In: Proceedings of the International Semiconductor Conference, pp. 397–402 (2007)

Goplakrishnan M., et al.: I-MOS: A novel semiconductor device with a subthreshold slop lower than kT/q. In: IEDM Technical Digest, pp. 289–292 (2002)

Nathanson, H., et al.: Resonant gate transistor. IEEE Trans. Electron Devices 14(3), 117–133 (1967)

Seabaugh, A.C., Zhang, Q.: Low-voltage tunnel transistors for beyond CMOS logic. Proc. IEEE 98(12), 2095–2110 (2010)

Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.K.: Tunneling field-effect transistors with subthreshold swing less than 60mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

Koswatta, S.O., Lundstrom, M.S., Nikonov, D.E.: Performance comparison between p-i-n tunneling transistors and conventional MOSFETs. IEEE Trans. Electron Devices 56(3), 456–465 (2009)

Boucart, K., Ionescu, A.M.: Double-gate Tunnel FET with high-K gate dielectric. IEEETrans. Electron Devices 54(7), 1725–1733 (2007)

Toh, E.-H., Wang, G.H., Samudra, G., Yeo, Y.C.: Device physics and design of germanium tunneling field-effect transistor with source and drain engineering for low power and high performance applications. J. Appl. Phys. 103(10), 104504–104504-5 (2008)

International Technology Roadmap for Semiconductor, http://www.itrs.net/ (2013)

Bhuwalka, K.K., Schulze, J., Eisele, I.: Scaling the vertical tunnel FET with Tunnel bandgap modulation and gate workfunction engineering. IEEE Trans Electron Devices 52(5), 909–917 (2005)

Wang, L., Yu, E., Taur, Y., Asbeck, P.: Design of tunneling field-effect transistors based on staggered heterojunctions for ultralow-power applications. IEEE Electron Device Lett. 31(5), 431–433 (2010)

Nayfeh, O.M., Chleirigh, C.N., Hennessy, J., Gomez, L., Hoyt, J.L., Antoniadis, D.A.: Design of tunneling field-effect transisitors using strained-silicon/strained-germanium type-II staggered heterojunctions. IEEE Electron Device Lett. 29(9), 1074–1077 (2008)

Appenzeller, J., Lin, Y.M., Knoch, J., Chen, Z.H., Avouris, P.: Comparing carbon nanotube transistors–the ideal choice: a novel tunneling device design. IEEE Trans. Electron Devices 52(12), 2568–2576 (2005)

Vandenberghe, W., Verhulst, A., Groeseneken, G., Soree, B., Magnus, W.: Analytical model for a tunnel field-effect transistor. In: Proceedings of the MELECON, pp. 923–928 (2008)

Bardon, M.G., Neves, H.P., Puers, R., Hoof, C.V.: Pseudo-two-dimensional model for double-gate tunnel FETs considering the junctions depletion regions. IEEE Trans. Electron Device 57(4), 827–834 (2010)

Shen, C., Ong, S.L., Heng, C-Huat, Samudra, G., Yeo, Yee-Chia: A variational approach to the two-dimensional nonlinear Poisson’s equation for the modeling of tunneling transistors. IEEE Electron Device Lett. 29(11), 1252–1255 (2008)

Zhang, L., Lin, X., He, J., Chan, M.: An analytical charge model for double-gate tunnel FETs. IEEE Trans. Electron Devices 59(12), 3217–3223 (2012)

Zhang, L., He, J., Chan, M.: A compact model for double-gate tunneling field-effect-transistors and its implications on circuit behaviors. In: IEEE International Electron Devices Meeting (IEDM), pp. 6.8.1–6.8.4 (2012)

De Graaff, H.C., Klaassen, F.M.: Compact transistor modelling for circuit design. Computational microelectronics. Springer, New York (1990)

Holtij, Thomas, Graef, Michael, Hain, Franziska Marie, Kloes, Alexander, Iñíguez, Benjamín: Compact model for short-channel junctionless accumulation mode double gate MOSFETs. IEEE Trans. Electron Devices 61(2), 288–299 (2013)

Gildenblat, Gennady: Compact Modeling Principles, Techniques and Applications. Springer, New York (2010)

Oh, S.-H., Monroe, D., Hergenrother, J.M.: Analytic description of short-channel effects in fully-depleted double-gate and cylindrical, surrounding-gate MOSFETs. IEEE Electron Device Lett. 21(9) (2000)

Lee, Jiyeong, Shin, Hyungsoon: Evanescent-mode analysis of short-channel effects in MOSFETs. J. Korean Phys. Soc. 44(1), 50–55 (2004)

Lee, Min Jin, Choi, Woo Young: Analytical model of single-gate silicon-on-insulator (SOI) tunneling field-effect transistors (TFETs). Solid-State Electron. 63, 110–114 (2011)

Kane, E.O.: Theory of tunneling. J. Appl. Phys. 32, 83 (1961)

Silvaco ATLAS, Device Simulation Software, Silvaco Int., Santa Clara, CA (2012)

Frank, D.J., Taur, Y., Wong, H.-S.P.: Generalized scale length for two-dimensional effects in MOSFETs. IEEE Electron Device Lett. 19, 385–387 (1998)

Nguyen, T.N.: Small-geometry MOS transistors: physics and modeling of surface- and buried-channel MOSFETs. Ph.D. Dissertation, Stanford University, Stanford (1984)

Frenkil, J.: A multi-level approach to low-power IC design. IEEE Spectr. 35, 54–60 (1998)

Kloes, A., Kostka, A.: A new analytical method of solving 2D poisson’s equation in MOS devices applied to threshold voltage and subthreshold modeling. Solid State Electron. 39(12), 1761–1775 (1996)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Kumar, S., Raj, B. Compact channel potential analytical modeling of DG-TFET based on Evanescent-mode approach. J Comput Electron 14, 820–827 (2015). https://doi.org/10.1007/s10825-015-0718-9

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-015-0718-9