Abstract

In this work, we have presented a comprehensive analysis of the performance of copper (Cu) and existing carbon nano tube (CNT) bundle structures (i.e. SWCNT, DWCNT and MWCNT) across nanometer technology nodes like 45, 32, 22 and 16 nm at local, intermediate and global level interconnects. Double walled carbon nano tubes (DWCNTs) and multi walled carbon nano tubes (MWCNTs) are modeled like simple single walled carbon nano tube (SWCNT) equivalent model with high accuracy. The analytical closed form delay expressions for SWCNT, DWCNT and MWCNT bundles have been found out. It has been observed that sparse SWCNT bundle interconnects show about 50 % performance improvement for 20 \(\upmu \)m long local level interconnects over Cu in 16 nm technology node, whereas the performance advantage numbers for MWCNT and sparse DWCNT bundles are 50 and 35 % respectively. For 200 \(\upmu \)m long intermediate level interconnects, the performance advantage numbers are 85, 80 and 75 % for dense SWCNT, MWCNT and dense DWCNT bundles respectively in 16 nm node. For 10 mm long global level interconnects, the performance advantage numbers are 85, 85 and 75 % for dense SWCNT, MWCNT and dense DWCNT bundles respectively in 16 nm node. It is also observed that the performance numbers improve with scaling for all levels of interconnects. It is also shown that the ratio of delay of CNT bundles and Cu for various levels of interconnects agree well with the existing work.

Similar content being viewed by others

References

Sahoo, M., et al. Performance analysis of multiwalled carbon nanotube bundles. In: 23rd IEEE International International Scientific Conference Electronics and Nanotechnology, (IEEE ELNANO 2013), pp. 200–204

Sahoo, M., et al. Efficient and compact electrical modeling of multi walled carbon nanotube interconnects. In: 3rd IEEE International Symposium on Electronic System Design (IEEE ISED 2012), pp. 236–240

Ijima, S.: Helical microtubules of graphitic carbon. Nature 354, 56–58 (1991)

Avouris, P., Appenzeller, J., Martel, R., Wind, S.J.: Carbon nanotube electronics. Proc. IEEE 91(11), 1772–1784 (2003)

Collins, P.G., Hersam, M., Arnold, M., Martel, R., Avouris, P.: Current saturation and electrical breakdown in multiwalled carbon nanotubes. Phys. Rev. Lett. 86(14), 3128–3131 (2001)

Liew, K.M., Wong, C.H., He, X.Q., Tan, M.J.: Thermal stability of single and multi-walled carbon nanotubes. Phys. Rev. B 71, 075424-1–075424-6 (2005)

Berber, S., Kwon, Y.-K., Tomanek, D.: Unusually high thermal conductivity of carbon nanotubes. Phys. Rev. Lett. 84(20), 4613–4616 (2000)

Thess, A., Lee, R., Nikolaev, P., Dai, H., Petit, P., Robert, J., Xu, C., Lee, Y.H., Kim, S.G., Rinzler, A.G., Colbert, D.T., Scuseria, G.E., Tomanek, D., Fischer, J.E., Smalley, R.E.: Crystalline ropes of metallic carbon nanotubes. Science 273(5274), 483–487 (1996)

Wei, B.Q., Vajtai, R., Ajayan, P.M.: Reliability and current carrying capacity of carbon nanotubes. Appl. Phys. Lett. 79(8), 1172–1174 (2001)

McEuen, P.L., et al.: Single-walled carbon nanotube electronics. IEEE Trans. Nanotechnol. 1(1), 78–85 (2002)

Srivastava, N., Banerjee, K.: Interconnect challenges for nanoscale electronic circuits. TMS J. Mater. 56(10), 30–31 (2004)

Srivastava, N., Banerjee, K.: A comparative scaling analysis of metallic and carbon nanotube interconnections for nanometer scale VLSI technologies. In: Proceedings of the 21st International VLSI Multilevel Interconnect Conference, Sep. 2004, pp. 393–398 (2004)

Im, S., Srivastava, N., Banerjee, K., Goodson, K.E.: Scaling analysis of multilevel interconnect temperatures for high-performance ICs. IEEE Trans. Electron Device 52(12), 2710–2719 (2005)

Burke, P.J.: Luttinger liquid theory as a model of the gigahertz electrical properties of carbon nanotubes. IEEE Trans. Nanotechnol. 1(3), 129–144 (2002)

Srivastava, Navin, Li, Hong, Kreupl, Franz, Banerjee, Kaustav: On the applicability of single-walled carbon nanotubes as VLSI interconnects. IEEE Trans. Nanotechnol. 8(4), 542–559 (2009)

Naeemi, A., Sarvari, R., Meindl, J.D.: Performance comparison between carbon nanotube and Cu interconnects for gigascale integration (GSI). IEEE Electron Device Lett. 26(2), 84–86 (2005)

Naeemi, A., Meindl, J.D.: Design and performance modeling for single-walled carbon nanotubes as local, semiglobal, and global interconnects in gigascale integrated systems. IEEE Trans. Electron Devices 54(1), 26–37 (2007)

Naeemi, A., Meindl, J.D.: Physical modeling of temperature coefficient of resistance for single- and multi-wall carbon nanotubes interconnects. IEEE Electron Device Lett. 28(2), 135–138 (2007)

Kreupl, F., Graham, A.P., Liebau, M., Duesberg, G.S., Seidel, R., Unger, E.: Carbon nanotubes for interconnect applications. IEDM Tech. Dig. 2004, 683–686 (2004)

Li, J., Ye, Q., Cassell, A., Ng, H.T., Stevens, R., Han, J., Meyyappan, M.: Bottom-up approach for carbon nanotube interconnects. Appl. Phys. Lett. 82(15), 2491–2493 (2003)

Nihei, M., Kondo, D., Kawabata, A., Sato, S., Shioya, H., Sakaue, M., Iwai, T., Ohfuti, M., Awano, Y.: Low-resistance multi-walled carbon nanotube vias with parallel channel conduction of inner shells. In: Proceedings of the Interconnect Technology Conference, 2005, pp. 234–236 (2005)

Sato, S., Nihei, M., Mimura, A., Kawabata, A., Kondo, D., Shioya, H., Iwai, T., Mishma, M., Ohfuti, M., Awano, Y.: Novel approach to fabricating carbon nanotube via interconnects using size-controlled catalyst nanoparticles. In: Proceedings of the Interconnect Technology Conference, 2006, pp. 230–232 (2006)

Srivastava, N., Banerjee, K.: Performance analysis of carbon nanotube interconnects for VLSI applications. In: Proceedings of the IEEE/ACM ICCAD, Nov. 2005, pp. 383–390 (2005)

Patel, D., Bin Kim, Yong.: Carbon nanotube bundle interconnect: performance evaluation, optimum repeater size and insertion for global wire. In: IEEE International Midwest Symposium on Circuits and Systems, pp. 749–752 (2010)

Raychowdhury, A., Roy, K.: Modeling of metallic carbon-nanotube interconnects for circuit simulations and a comparison with Cu interconnects for scaled technologies. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 25(1), 58–65 (2006)

Fu, G., Yin, W. Y.: Circuit modeling and time delay analysis of double-walled carbon nanotube interconnects. In: Proceedings of Asia-Pacific Microwave Conference, pp. 1–4 (2007)

Naeemi, A., Meindl, J.D.: Compact physical models for multiwall carbon-nanotube interconnects. IEEE Electron Device Lett. 27(5), 338–340 (2006)

Li, H., Yin, W.Y., Banerjee, K., Mao, J.F.: Circuit modeling and performance analysis of multi-walled carbon nanotube interconnects. IEEE Trans. Electron Devices 55(6), 1328–1337 (2008)

Li, H.J., Lu, W.G., Li, J.J., Bai, X.D., Gu, C.Z.: Multichannel ballistic transport in multiwall carbon nanotubes. Phys. Rev. Lett. 95, 086601–086604 (2005)

Liang, Feng, Wang, Gaofeng: Estimation of time delay and repeater insertion in multiwall carbon nanotube interconnects. IEEE Trans. Electron Devices 58(8), 2712–2720 (2011)

Sarto, M.S., Tamburrano, A.: Single-conductor transmission line model of multiwall carbon nanotubes. IEEE Trans. Nanotechnol. 9(1), 82–92 (2010)

Elmore, W.C.: The transient response of damped linear networks with particular regard to wideband amplifiers. J. Appl. Phys. 19(1), 55–63 (1948)

Burke, P.J.: An RF circuit model for carbon nanotubes. IEEE Trans. Nanotechnol. 2(1), 55–58 (2003)

Kim, W., Javey, A., Tu, R., Cao, J., Wang, Q., Dai, H.: Electrical contacts to carbon nanotubes down to 1 nm in diameter. Appl. Phys. Lett. 87, 173101-1–173101-3 (2005)

Rosa, E.B., Grover, F.W.: Formulas and Tables for the Calculation of Mutual and Self-inductance. Government Printing Office, Washington, DC (1916)

Pop, E., Mann, D., Goodson, K., Dai, H.: Electrical and thermal transport in metallic single-wall nanotubes on insulating substrates. J. Appl. Phys. 101(9), 093710-1–093710-10 (2007)

Nieuwoudt, Arthur, Massoud, Yehia: Evaluating the impact of resistance in carbon nanotube bundles for VLSI interconnect using diameter-dependent modeling techniques. IEEE Trans. Electron Devices 53(10), 2460–2466 (2006)

Banerjee, K., et al.: Analysis of on-chip inductance effects for distributed RLC interconnects. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 21, 904–915 (2002)

Sylvester, D., Hu, C.: Analytical modeling and characterization of deep-submicrometer interconnect. Proc. IEEE 89(5), 634–664 (2001)

International Technology Roadmap for Semiconductors (ITRS) Reports [Online]. http://www.itrs.net/reports.html (2006)

Predictive Technology Model [Online]. http://ptm.asu.edu/

Carbon Nanotube Interconnect Analyzer tool [Online]. http://www.nanohub.org/tools/

Acknowledgments

This work is partially supported by the DIT, Government of West Bengal, India under VLSI Design Project.

Author information

Authors and Affiliations

Corresponding author

Appendix

Appendix

1.1 Optimized repeater insertion methodology for copper wire

1.1.1 Local level interconnects

Electrical model of a Cu wire at the local level is shown in Fig. 22. Definitions for various parameters shown in the figure are tabulated in Table 15. Here, we approximate the whole system as a single dominant pole transfer function. The effective time constant (\(\tau \)) of the system is given as,

Differentiating (39) w.r.t S , the expression in (27) can be derived. By replacing S in (39), the expression in (26) can be found out.

1.1.2 Intermediate and global level interconnects

Electrical model of a Cu wire at the intermediate and global level is shown in Fig. 23. The effective time constant of a single stage (i.e. from one repeater to the immediately succeeding one) is denoted by \(\tau _{stage}\) and it can be calculated as,

and, the effective time constant (\(\tau \)) of the whole system is given by,

Differentiating (41) w.r.t S , the expression in (29) can be derived. Similarly, differentiating (41) w.r.t N , the expression in (30) can be derived. By replacing S and N in (41), the expression in (31) can be found out. Also one point to note is that as a single dominant pole transfer function is considered here, so the delay ratio of CNT bundle to Cu is equivalent to the ratio of their time constants.

1.2 Optimized Repeater insertion methodology for CNT bundles

1.2.1 Local level interconnects

Electrical model of a CNT bundle at the local level is shown in Fig. 24. The effective time constant (\(\tau \)) of the whole system is given by,

Differentiating (42) w.r.t S , the expressions in (34) can be derived. Finally, replacing S in (42), the expression in (33) can be found out.

1.2.2 Intermediate and global level interconnects

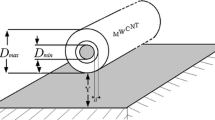

Electrical model of a CNT bundle at the intermediate and global level is shown in Fig. 25. Definitions for various parameters shown in the figure are tabulated in Table 15. The effective time constant (\(\tau \)) of the whole system is given by,

Differentiating (43) w.r.t S and N, the expressions in (37) and (36) can be derived. Finally, replacing S and N in (43), the expression in (38) can be found out.

Rights and permissions

About this article

Cite this article

Sahoo, M., Ghosal, P. & Rahaman, H. Performance modeling and analysis of carbon nanotube bundles for future VLSI circuit applications. J Comput Electron 13, 673–688 (2014). https://doi.org/10.1007/s10825-014-0587-7

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10825-014-0587-7