Abstract

Design of Embedded Systems is becoming more and more complex in terms of verify that requirements are fulfilled at different design levels. This requires the simulation of the system and the checking of its timing and functional properties. model-driven design and UML give a reasonable solution to cope with such complexity since they have mechanisms to model and verify embedded systems. This paper presents a methodology which starts from UML/MARTE sequence diagrams with timing constraints and the automatic generation of executable SystemC/TLM and VHDL code with checkers from such diagrams. The simulation of the generated model allows to verify the specified sequence of exchanged information between components while checkers allow to verify that properties and timing constraints are met. Three case studies are used to show the validity of the approach and a less than linear increase of execution time overhead due to time observation and assertion checkers.

Similar content being viewed by others

References

Accellera Standard OVL V2 Library Reference Manual (2011) OVL 2.6. http://www.accellera.org

Alagar VS, Periyasamy K (2011) Extended Finite State Machine. In: Gries D, Schneider FB (eds) Specification of Software Systems. Texts in Computer Science, Springer London, pp 105–128. http://link.springer.com/book/10.1007%2F978-0-85729-277-3

Atego (2013) Artisan Studio. http://www.atego.com

Bombieri N, Di Guglielmo G, Ferrari M, Fummi F, Pravadelli G, Stefanni F, Venturelli A (2010) HIFSuite: Tools for HDL Code Conversion and Manipulation. EURASIP Journal on Embedded Systems 1:436,328

EDALAB (2012) HIFSuite: Tools and APIs for HDL Code Conversion and Manipulation- version 2012.12. http://www.hifsuite.com

Balarin F et al (1997) Hardware–Software Co-design of embedded systems: the polis approach. Kluwer Academic Press, Norwell

Habibi A, Tahar S (2006) Design and verification of SystemC Transaction-Level Models. Very Large Scale Integr (VLSI) Syst, IEEE Trans 14(1):57–68

Heng D, Ping G, Xiao-mei Y, Lin-li Z (2010) A research of object constraint language used in PIM accurate modeling. In: International conference on information management and engineering (ICIME), pp 629–632

IBM (2012) IBM Rational. http://www-01.ibm.com/software/rational/

Manual R (2000) IEEE Standard VHDL Language. IEEE Std 1076–2000, pp i–290. doi:10.1109/IEEESTD.2000.92297

Martin G, Muller W (2005) UML for SoC design. Springer, New York

Martin G, Smith G (2009) High-level synthesis: past, present, and future. Des Test Comput, IEEE 26(4):18–25

McUmber W, Cheng B (1999) UML-based analysis of embedded systems using a mapping to VHDL. In: International symposium on high-assurance systems engineering, 1999, pp. 56–63

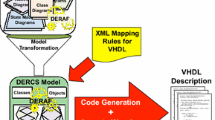

Moreira T, Wehrmeister M, Pereira C, Petin JF, Levrat E (2010) Automatic code generation for embedded systems: from UML specifications to VHDL code. In: International conference on industrial informatics (INDIN), 2010, pp 1085–1090

Mueller W, Villar E, Carballeda, M (2010) The SATURN approach to SysML-Based HW/SW Codesign. In: Computer society annual symposium on VLSI (ISVLSI), 2010, pp 506–511

Nguyen K, Sun Z, Thiagarajan P, Wong WF (2004) Model-driven SoC design via executable UML to SystemC. In: Real-Time systems symposium, pp 459–468

Object Management Group (2009) OMG Unified Modeling LanguageTM (OMG UML), superstructure(version 2.2). In: OMG document number: formal/2009-02-02. http://www.omgmarte.org

Object Management Group (2011) A UML Profile for MARTE (version 1.1). In: OMG document number: formal/2011-06-02. http://www.omgmarte.org

Object Management Group (2013) Acceleo. http://www.eclipse.org/acceleo/

Riccobene E, Scandurra P, Rosti A, Bocchio S (2005) A SoC design methodology involving a UML 2.0 profile for SystemC. In: Design, Automation and test in Europe, pp 704–709 Vol. 2

Sébastien Gérard et al. (2012) Papyrus UML, http://www.papyrusuml.org

Technical report (2005) Survey of system design trends. Technical report, Electronics Weekly & Celoxica

Transaction Level Modeling Working Group (2006) OSCI TLM 2.0. http://www.systemc.org

Vanderperren Y, Mueller W, Dehaene W (2008) UML for electronic systems design: a comprehensive overview, vol 12. Springer, Berlin

Xi C, Hua LJ, ZuCheng Z, YaoHui S (2005) Modeling SystemC design in UML and automatic code generation. In: Design automation conference, 2005. Proceedings of the ASP-DAC 2005. Asia and South Pacific, vol 2, pp 932–935

Yu J, Li T, Tan Q (2006) The use of UML sequence diagram for System-on-Chip system level transaction-based functional verification. in: the sixth world congress on intelligent control and automation, 2006, vol 2, pp 6173–6177

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ebeid, E., Fummi, F. & Quaglia, D. HDL code generation from UML/MARTE sequence diagrams for verification and synthesis. Des Autom Embed Syst 19, 277–299 (2015). https://doi.org/10.1007/s10617-014-9158-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10617-014-9158-1