Abstract

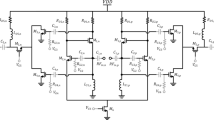

Scaling of minimum length of the MOSFET has improved its performance but has reduced the breakdown voltage which makes it prone to Electrostatic Discharge (ESD) damage. This work presents a low-power g m -boosted common gate (CG) ultra wideband (UWB) low noise amplifier (LNA) architecture, operating in the 5–7 GHz range, employing current-reuse technique with LC based Electrostatic Discharge (ESD) protection. Common gate topology supports wide band input matching and noise figure independent of operating frequency. A PMOS common source topology is used as the gm-boosting stage in order to reduce the noise figure and to remove the dependency of noise figure from the bias point. The gm-boosting stage and the amplifier share common bias current to reduce the power consumption of the LNA. A shunt inductor, series capacitor and power clamp are used for protecting the circuit from ESD damage. The ESD circuit is co-designed with the input matching network in order to reduce the area of the layout. The proposed topology has shown significant improvement in gain and noise figure with ESD protection.

Similar content being viewed by others

References

Muhammad, K., & Rezaul Hassan, S. M. (2012). A 3–5 GHz Current-Reuse gm-boosted CG LNA for ultra wide band in 130 nm CMOS process. IEEE Transaction on Very Large Scale Integration (VLSI) Systems, 20(3), 400–409.

Tsai, Ming-Hsien, Hsu, Shawn S. H., Fu lung, H., Fu lung, H., Chewn-Pu, I., & Tzu-Jin, Y. (2013). Design of 60 GHz low noise amplifier with low NF and robust ESD protection in 65 nm CMOS. IEEE Transaction on Microwave Theory and Techniques, 61(1), 553–561.

Tsai, Ming-Hsien, Hsu, Shawn S. H., Fu lung, H., & Chewn-Pu, I. (2011). ESD protected K-band low noise amplifier using RF junction varactors in 65 nm CMOS. IEEE Transaction on Microwave Theory and Techniques, 59(12), 3455–3462.

Rafaella, F., Fernado, S., & Eduardo, P. (2014). Most moderate–weak-inversion region as the optimum Design zone for CMOS 2.4 GHz CS LNAs. IEEE Transaction on Microwave Theory and Techniques, 62(3), 556–566.

Schell, Z., Hosein A. -R., Mustapha C. E. Y., (2012). A high gain low power 2–14 GHz UWB CMOS LNA for wireless receivers. International Journal of Electronics and Communication (AEU), 66(9), 727–731.

Voldman, S. (2006). ESD: Circuits and devices. New York: Wiley.

Amerasekera, A., & Duvvury, C. (2002). ESD in silicon integrated circuits (2nd ed.). London, U.K.: Wiley.

Wang, A. (2002). On-chip ESD protection for integrated circuits: an IC design perspective. Norwell, MA: Kluwer.

Wang, A., Feng, H., Zhan, R., Xie, H., Chen, G., Wu, Q., et al. (2005). A review on RF ESD protection design. IEEE Transactions on Electron Devices, 52(7), 1304–1311.

Mergens, M. P. J., Marichal, O., Thijs, S., Van Camp, B., Russ, C. C. (2005). Advanced SCR ESD protection circuits for CMOS/SOI nanotechnologies. In Proceedings of the IEEE Custom Integr. Circuits Conference, pp. 481–488.

Li, J., Mitra, S., Li, H., Abou-Khalil, M. J., Chatty, K., & Gauthier, R. (2008). Capacitance investigation of diode and GGNMOS for ESD protection of high frequency circuits in 45 nm SOI CMOS technologies. In Proceedings of the EOS/ESD Symposium, pp. 228–234.

Ker, M.-D., & Lin, C. Y. (2008). Low-capacitance SCR with waffle layout structure for on-chip ESD protection in RF ICs. IEEE Transactions on Microwave Theory and Techniques, 56(5), 1286–1294.

Xie, H., Feng, H., Zhan, R., Wang, A., Rodriguez, D., & Rice, D. (2005). A new low-parasitic polysilicon SCR ESD protection structure for RF ICs. IEEE Electron Device Letters, 26(2), 121–123.

Voldman, S., Geissler, S., Nakos, J., Pekarik, J., & R. Gauthier, (1998). Semiconductor process and structural optimization of shallow trench isolation-defined and polysilicon-bound source/drain diodes for ESD networks. In Proceedings of the EOS/ESD Symposium, pp. 151–160.

Wei, M. D., Chang, S. F., & Liu, Y. C. (2008). A low-power ultra-compact CMOS LNA with shunt-resonating current-reused topology. In Proceedings of the 3rd EMICC, pp. 350–353.

Cha, C. Y., & Lee, S. G. (2003). A 5.2-GHz LNA in 0.35 μmCMOS utilizing inter-stage series resonance and optimizing the substrate resistance. IEEE Journal of Solid-State Circuits, 38(4), 669–672.

Huang, Z. D., Lin, Z. M., & Lai, H. C., (2007). An high gain low noise amplifier with current-reused technique for UWB applications. In Proceedings of the IEEE Conference EDSSC, pp. 977–980.

Walling, J. S., Shekhar, S, & Allstot, D. J. (2007). A gm-boosted current reuse LNA in 0.18 μm CMOS. In Proceedings of the IEEE Radio Freq. Integr. Circuits Symposium, pp. 613–616.

Bindhiya V., Karthigha B., & Jayakumar M., (2014). Design of CMOS based reconfigurable LNA at millimeter wave frequency using active load. In IEEE International Conference on Advanced Communication Control and Computing Technologies, pp 713–718.

Sari, S., Balamurugan, Karthigha, & Jayakumar, M. (2012). Dependence of Substrate Resistance of RF MOSFET on the Performance of LNA at 60 GHz. International Journal of Computer Science, 9(4), 277–283.

Qiuzhen, W., Qingdi, W., & Zhiwei, Z. (2014). Design and analysis of a 3.1–10.6 GHz UWB low noise amplifier with forward body bias technique. International Journal of Electronics and Communications (AEÜ), 69, 119–125.

Chen, C. C., & Wang, Y. C. (2013). 3.1–10.6 GHz ultra-wideband LNA design usingdual-resonant broadband matching technique. Int J Electron Commun, 67(6), 500–503.

Weng, R. M., Liu, C. Y., & Lin, P. C. (2010). A low-power full-band low-noise amplifier for ultra-wideband receivers. IEEE Trans Microw Theor Tech, 58(8), 2077–2083.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ankathi, S., Vignan, S., Athukuri, S. et al. A 5–7 GHz current reuse and gm-boosted common gate low noise amplifier with LC based ESD protection in 32 nm CMOS. Analog Integr Circ Sig Process 90, 573–589 (2017). https://doi.org/10.1007/s10470-016-0915-x

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10470-016-0915-x